# ZDP323B Series Digital PIR Sensor with I<sup>2</sup>C Interface

Product Specification Preliminary

PS041704-0824

Copyright ©2024 Zilog Inc. All rights reserved. www.zilog.com

#### LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

#### As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

#### **Document Disclaimer**

©2024 by Zilog, Inc. All rights reserved. Information in this publication concerning the devices,

applications, or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

Z8, Z80, Z8 Encore!, Z8 Encore! XP and ZMOTION are trademarks or registered trademarks of Zilog, Inc. All other product or service names are the property of their respective owners.

# **Revision History**

Each instance in this document's revision history reflects a change from its previous edition. For more details, refer to the corresponding page(s) or appropriate links furnished in the table below.

| Date        | <b>Revision Level</b> | Description                                                           | Pages      |

|-------------|-----------------------|-----------------------------------------------------------------------|------------|

| April 2022  | 01                    | Original issue.                                                       | All        |

| Jan. 2024   | 02                    | Updated copyright dates<br>Added note on bandpass output data values. | i, ii<br>9 |

| March 2024  | 03                    | Corrected Product Brief document number                               | 23         |

| August 2024 | 04                    | Removed PS0416 from Table 11                                          | 23         |

### 1 Overview

Zilog's ZDP323B series of Digital Passive Infrared (DPIR) sensors combines a dual element PIR sensor with all necessary signal processing and an I<sup>2</sup>C communication interface to provide a fully integrated motion sensor, delivering high performance and excellent EMI immunity for the most demanding motion detection applications.

The device is a dual element, balanced differential (series-opposed type) sensor that comes in a 4-pin TO-5 nickel-plated metal can. The sensing elements are placed behind a spectral filter window tuned to 8-13µm wavelength to help block out unwanted IR energy sources.

Communication is supported over an I<sup>2</sup>C interface and signal processing is performed digitally with programmable gain, bandwidth, and detection thresholds.

The ZDP323B DPIR sensor should be used in combination with a passive infrared lens.

#### 1.1 Features

- Dual-element balanced differential (series opposed) PIR sensor

- Integrated signal processing with programmable filter/gain profiles

- Programmable thresholds

- I<sup>2</sup>C interface with trigger output mode

- Up to 4 devices can be supported on a single I<sup>2</sup>C bus

- 10-bit addressing, or General Call supported

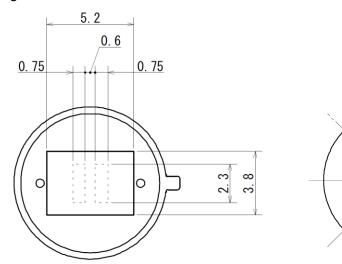

- Elements are 0.75mm x 2.3mm spaced 0.6mm apart

- Wide Field of View: 148° x 136°

- Standard 4-pin metal TO-5 package

- Wide operating voltage range of 1.8V to 5.5V

- 3µA operating current

- Operating temperature range of -40°C to +80°C

#### 1.2 Applications

- Video Doorbell

- IP Camera

- HVAC Control

- Home Appliances

- Lighting Control

- Proximity Detection

# 2 Ordering Information

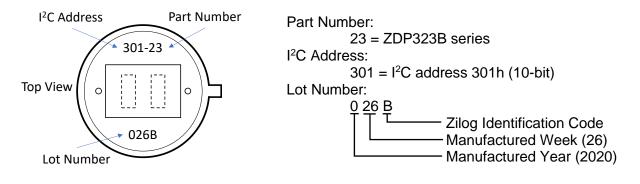

There are four variations of the ZDP323B series Digital PIR Sensor available, differentiated by their I<sup>2</sup>C bus address. All other performance, functions and features remain the same. All devices will also respond to an I<sup>2</sup>C General Call transaction.

| Part Number | Description                               | I <sup>2</sup> C Bus Address |

|-------------|-------------------------------------------|------------------------------|

| ZDP323B1    | Digital PIR Sensor; Dual Element, I2C Bus | 301h                         |

| ZDP323B2    | Digital PIR Sensor; Dual Element, I2C Bus | 302h                         |

| ZDP323B3    | Digital PIR Sensor; Dual Element, I2C Bus | 303h                         |

| ZDP323B4    | Digital PIR Sensor; Dual Element, I2C Bus | 304h                         |

#### Table 1 - Ordering Information

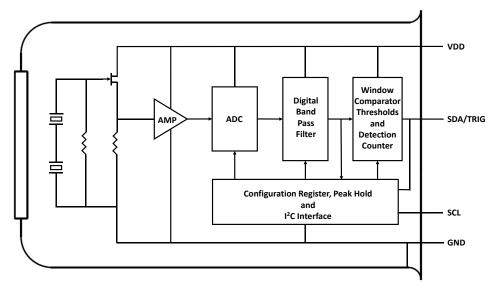

# 3 Block Diagram

The device consists of two series opposed PIR sensing elements connected to a FET follower and all other processing required to detect motion. An I<sup>2</sup>C interface is provided for communications. The SDA signal can be used as a Motion Trigger output to interrupt or wake up a host processor when motion is detected.

Figure 1 - Block Diagram

### 3.1 Operation

Refer to Figure 1. An amplifier provides buffering of the PIR signal for the ADC which performs a conversion every 9.5ms and passes the result to the digital bandpass filter. One of several different filter profiles can be selected depending on performance requirements and lens characteristics.

Peak values from the output of the bandpass filter are saved in the Peak Hold register and can be read over the I<sup>2</sup>C interface. This is useful for development when selecting the best filter profile for the application requirements and specific lens being used.

If Trigger Output mode is enabled, the output of the digital band pass filter is passed to a digital window comparator with programmable thresholds. When the signal exceeds the selected window threshold, the detection counter is incremented. If the signal still exceeds 1/2 the selected threshold when the next ADC sample is processed, the detection counter is incremented again, and the Trigger Output (TRIG pin) is driven active for 50µs indicating that a motion event has been detected. When multiple devices are on the same I<sup>2</sup>C bus, the Peak Hold value is read to determine which device asserted its Trigger Output.

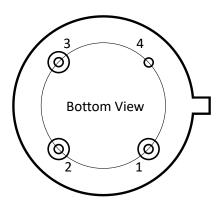

### **4** Pin Descriptions

Figure 2 - Bottom View Pin Out

| Pin | Name     | Description                                                                                             |

|-----|----------|---------------------------------------------------------------------------------------------------------|

| 1   | SDA/TRIG | <b>SDA:</b> I <sup>2</sup> C Serial Data<br>Transfers data to/from external I <sup>2</sup> C<br>master. |

|     |          | <b>TRIG:</b> Motion Trigger<br>Driven low when motion detected                                          |

| 2   | VDD      | Power Supply                                                                                            |

| 3   | SCL      | I <sup>2</sup> C Serial Clock<br>Serial clock input from extern I <sup>2</sup> C<br>master              |

| 4   | GND      | Ground - Case                                                                                           |

|     |          |                                                                                                         |

#### **Table 2 - Pin Descriptions**

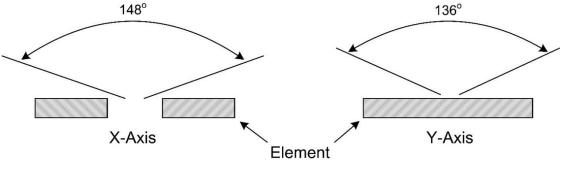

### 5 Field of View

The typical Field of View (FOV) of the ZDP323B series Digital PIR Sensor is 148° in the X axis and 136° in the Y axis as shown in the following figure.

Figure 3 - Field of View

5

5.08

PCD

# **6** Mechanical Dimensions

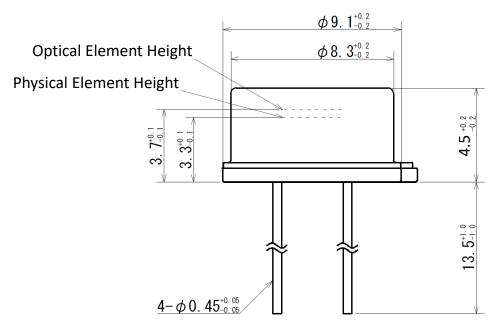

The dimensions of the ZDP323B series Digital PIR Sensor are shown in the following figures. All dimensions are  $\pm 0.2$ mm unless otherwise stated.

Figure 4 - Top View

Figure 5 - Bottom View

4

ø

3

Ø

Ø

2

Figure 6 – Side View

Note: The Optical Element Height specified provides the effective focal length required for the lens. The higher distance as compared to the Physical Element Height is due to the refraction caused by the window material.

# 7 Device Markings

Figure 7 - Device Markings

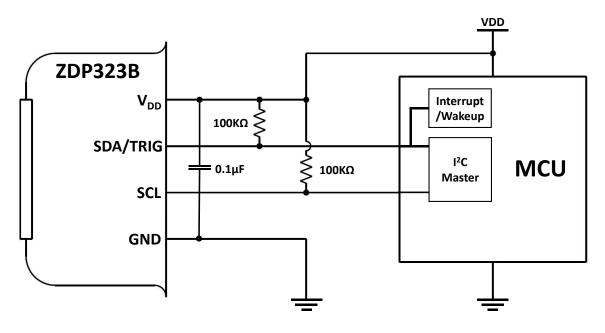

# 8 Recommended Circuit

The recommended SDA and SCL pull up resistor value for 100KHz I<sup>2</sup>C operation is 100K $\Omega$ .

Note: The  $0.1\mu$ F decoupling capacitor is not required in all applications. Include this capacitor in designs where the supply voltage is not well regulated or contains significant noise.

# 9 Communications Interface

### 9.1 I<sup>2</sup>C Bus Mode

The ZDP323B Digital PIR Sensor provides an  $I^2C$  interface to communicate with a host MCU. The  $I^2C$  interface operates as a slave device and supports standard mode (100 KHz) and fast mode (400 KHz) operation.

### 9.2 I<sup>2</sup>C Slave Addressing

There are four unique 10-bit I<sup>2</sup>C addresses to choose from, which are differentiated by the last digit in the part number (see Table 3 below). This allows up to four ZDP323 devices to share the same I<sup>2</sup>C bus.

All devices also respond to the I<sup>2</sup>C 7-bit General Call transaction. This is recommended for applications where the ZDP323 Digital PIR Sensor is the only device on the I<sup>2</sup>C bus as it provides a simpler communications method with less overhead.

Device part numbers end in 1, 2, 3 or 4 to identify the specific 10-bit  $I^2C$  address the device is using (301h to 304h). The specific addresses are listed in Table 3 along with the recommended part numbers to use depending on the number of Digital PIR sensors on a shared  $I^2C$  bus.

For example, if only a single Digital PIR sensor is on the I<sup>2</sup>C bus, the ZDP323B1 is recommended. If two Digital PIR sensors are on the same I<sup>2</sup>C bus, it is recommended to select the ZDP323B1 and ZDP323B2 sensors.

| Part<br>Number | I <sup>2</sup> C Bus<br>Address | Number of Digital PIR Devices on<br>Same I <sup>2</sup> C Bus |   |   |   |  |

|----------------|---------------------------------|---------------------------------------------------------------|---|---|---|--|

| Number         | Audress                         | 1                                                             | 2 | 3 | 4 |  |

| ZDP323B1       | 301h                            | Х                                                             | Х | Х | Х |  |

| ZDP323B2       | 302h                            |                                                               | Х | Х | Х |  |

| ZDP323B3       | 303h                            |                                                               |   | Х | Х |  |

| ZDP323B4       | 304h                            |                                                               |   |   | Х |  |

### Table 3 - I<sup>2</sup>C Slave Addresses

### 9.3 Power On Initialization

The device is ready for communications 0.5 seconds after  $V_{DD}$  reaches the minimum supply voltage of 1.8V. No communication should be attempted prior to this time.

After 0.5 seconds, the Configuration Register may be written and stability time delay  $T_{\text{STAB}}$  started.

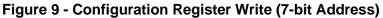

### 9.4 Writing to the Configuration Register

The Configuration Register data consists of 56 bits and controls the operation of the Digital PIR Sensor. The device can support either a 10-bit I<sup>2</sup>C transaction or a 7-bit General Call transaction. Both transaction types are shown in the following figures.

The configuration register bits are sent to the sensor directly after sending the slave address (or General Call Address). No internal device addressing is required. Configuration bits are sent sequentially starting with bit 55 (Most Significant Bit first).

If the configuration register is not set after power on, the default values are applied for Detection Threshold, Digital band pass filter step and Digital band pass filter type.

See Table 4 for configuration register bit definitions and default values.

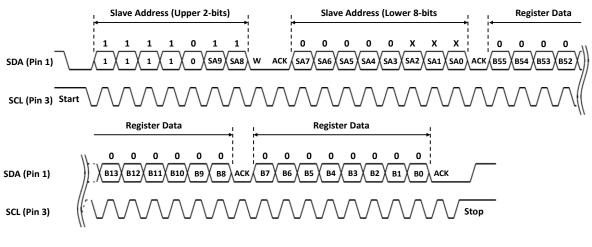

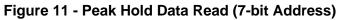

### 9.4.1 Reading Peak Hold Data

The ZDP323B Digital PIR Sensor tracks the peak value from the output of the bandpass filter which can be read over the I<sup>2</sup>C interface. This value is provided in a 12-bit, signed, 2's compliment format.

The peak hold value is tracked each time the bandpass filter output is updated. The output value from the bandpass filter is compared against the current peak hold value. If the absolute value of the bandpass filter output is greater than the current peak hold absolute value, it is saved as the new peak hold value.

Figure 11 shows the  $I^2C$  transaction used to read the Peak Hold Data using the 7-bit General Call transaction and Figure 12 shows the  $I^2C$  transaction required to read the Peak Hold Data using a 10-bit address.

#### Figure 12 - Peak Hold Data (10-bit Address)

When the Peak Hold value is read, it is reset to 0 and tracking starts over. If the Peak Hold Data is read at a rate shorter than  $T_{CYC}$ , the value returned could be 0 (since it has not been updated since the last read). Therefore, it is recommended to read the Peak Hold data at a rate not less than ~10ms.

The Peak Hold value should not be read until the sensor stability time ( $T_{\text{STAB}}$ ) has completed.

### 9.5 Trigger Output Mode

The ZDP323B Digital PIR Sensor can operate in a Trigger Output Mode to signal a host MCU when a motion event is detected. When Trigger Output Mode is enabled, the SDA/TRIG pin is driven active low when the sensor signal meets the defined motion detection qualification parameters.

### 9.5.1 Enabling and Disabling Trigger Output Mode

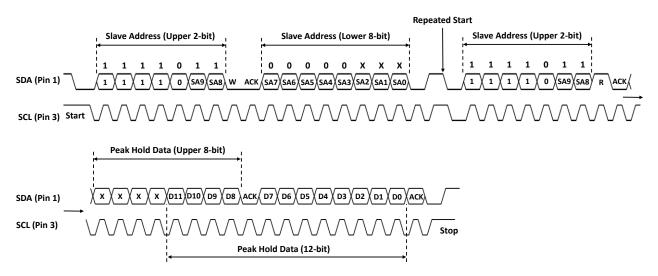

Trigger Output Mode is enabled by writing control register TRIGOM (Bit 23) to a 1 and is disabled by writing it to a 0. The default state is disabled.

When enabled, the SDA/TRIG pin remains open drain (external pull up resistor required) until a qualified motion event is detected. SDA/TRIG is driven low for 50µs when a motion event is detected.

When Trigger Output mode is enabled, if the SCL pin is driven low while the SDA/TRIG pin is active (low), and an I<sup>2</sup>C START condition is satisfied, the SDA/TRIG pin is released automatically, and the sensor operates as slave. The ensures an I<sup>2</sup>C master can write to and read from the device while Triggered Output Mode is enabled.

#### 9.6 Detection Counter

This ZDP323B features a detection counter, which controls the Trigger Output. The Detection counter is set to 1 when the signal output of the Bandpass Filter exceeds the Detection Threshold level set in the Configuration Register (bits 15 to 22). If the next bandpass filter output exceeds ½ the Detection Threshold, the counter is incremented to 2 and the Trigger Output is activated.

The Detection Counter is cleared under the following conditions:

- After activating the Trigger Output.

- When the bandpass filter output is less than 1/2 the Detection Threshold.

- When an I<sup>2</sup>C Start condition is satisfied.

**Caution:** Since the Detection Counter is reset on each I<sup>2</sup>C Start condition, the Trigger Output will not be asserted if the I<sup>2</sup>C Master continuously communicates with the device. If the I<sup>2</sup>C Master needs to continually communicate with the device (monitoring Peak Hold data), Trigger Output Mode should be disabled.

Note:

The bandpass filter sampling period is more frequent than the Trigger output update period which can result in a situation where the Trigger Output deactivation appears delayed as compared to the output data. This can result in the output data being up to  $\pm$ -3 counts outside of the programmed threshold value.

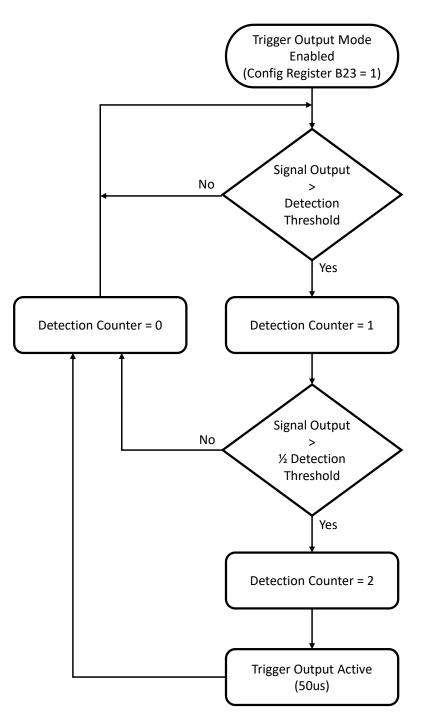

Refer to the flow chart in Figure 13 and the operation example in Figure 14 for more details.

Figure 13 - Detection Counter Flow Chart

### 9.6.1 Trigger Output Operation Example

Refer to Figure 14 for the following description.

| A: | I <sup>2</sup> C transaction. Host MCU enables Trigger Output mode by setting TRIGOM (Configuration register bit 23) to a 1. The Detection Counter is reset to 0.                                                                                                                                                                                                                                                               |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B: | Signal Output exceeds Detection Threshold; Detection Counter = 1                                                                                                                                                                                                                                                                                                                                                                |

| C: | Signal Output still exceeds $\frac{1}{2}$ Detection Threshold; Detection Counter = 2; Trigger Output (SDA/TRIG) activated (driven low) for 50µs.                                                                                                                                                                                                                                                                                |

| D: | I <sup>2</sup> C transaction. Host MCU disables Trigger Output mode by writing TRIGOM to 0.                                                                                                                                                                                                                                                                                                                                     |

| E: | I <sup>2</sup> C transaction. Host reads Peak Hold data. This is required when multiple ZDP323B devices are connected on the same I <sup>2</sup> C bus. Reading Peak Hold data allows the Host MCU to determine which device activated the Output Trigger since the Peak Hold data value will be greater than the Detection Threshold. If only a single device is on the I <sup>2</sup> C bus, steps D and E are not necessary. |

Figure 14 - Trigger Output Mode Example

Note:

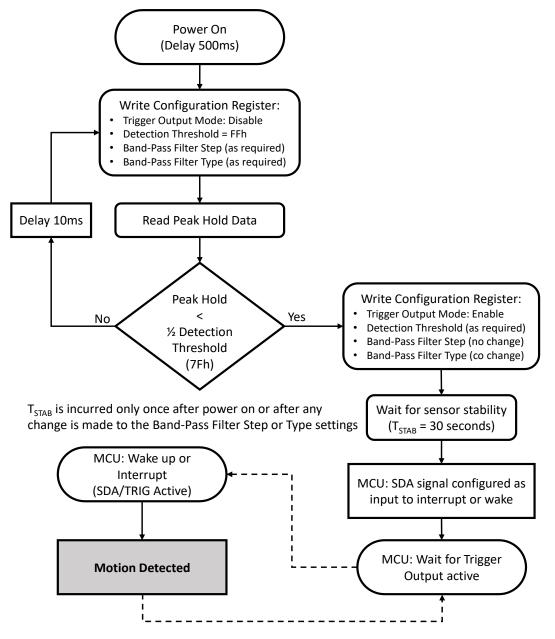

Trigger Output mode should be enabled only when the signal output is less than the ½ Detection Threshold. The following procedure can be used to ensure this:

- 1. Write the Detection Threshold (Configuration register bits 15 to 22) to its maximum value (FFh).

- 2. Continually read the Peak Hold value every 10ms until the value is below ½ the Detection Threshold value (7Fh).

- 3. Write the Configuration register with the required Detection Threshold, filter selection and Trigger Output mode enabled.

# **10 Device Reset**

The ZDP323B Digital PIR Sensor can be reset by the following methods:

- 1. Write to the Configuration Register with default values as described in section 9.4 and 13.

- 2. Power cycle. The supply voltage should be held below 0.5V for 30ms or longer. After a power cycle, the Configuration Register values will be at their reset value described in Table 4.

# **11 Stability Time**

After the device is powered on, or any time the Bandpass filter settings are changed, the device must be allowed to stabilize before motion can be detected reliably. Sensor Data values and the Trigger Output should be ignored until the stability time has finished. This time is defined by  $T_{STAB}$  in Table 9.

# **12 Operation Examples**

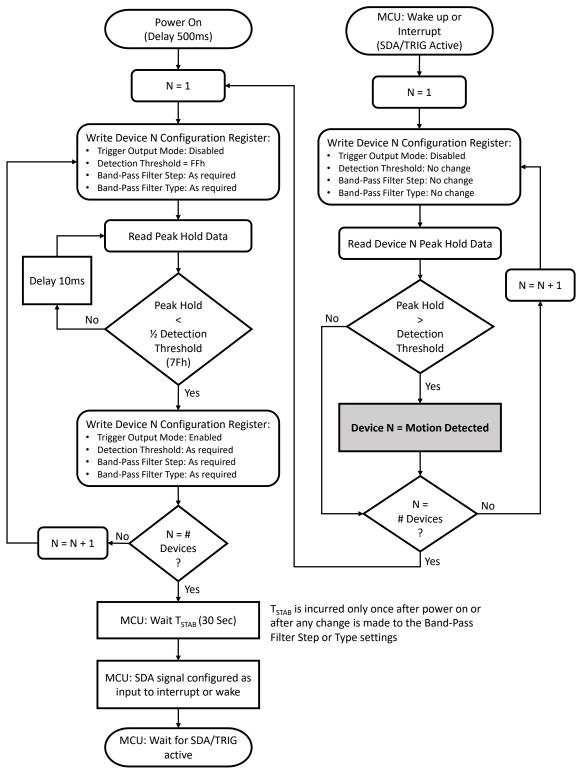

The following sections provide an example of operating the ZDP323B Digital PIR Sensor in a single device application (Figure 15) and a multiple device application (Figure 16).

### **12.1 Single Device Operation**

Figure 15 - Single Device Operating Example

### **12.2 Multi-Device Operation**

# **13 Control Register Bit Definitions**

The Configuration Register data consists of 56 bits and controls the operation of the Digital PIR Sensor. Several of the bits are reserved and should be set to 0. There are 4 main configuration parameters: Detection Threshold Level, Trigger Output Mode, and Digital Band-Pass Filter Step and Type.

| Bit       | Default | Name     | Description                                                                                                                 |  |  |

|-----------|---------|----------|-----------------------------------------------------------------------------------------------------------------------------|--|--|

| B0 – B7   | 0       | Reserved | These bits are reserved and should be set to 0.                                                                             |  |  |

| B8 – B14  | 0       | Reserved | These bits are reserved and should be set to 0.                                                                             |  |  |

| B15       | 0       | DETLVL0  | Detection Threshold Level:                                                                                                  |  |  |

| B16       | 0       | DETLVL1  | Sets the upper and lower detection threshold levels used by the window comparator. The value is based on the ADC conversion |  |  |

| B17       | 1       | DETLVL2  | after the band-pass filter.                                                                                                 |  |  |

| B18       | 1       | DETLVL3  | 3. These bits can be set from 0 to 255.                                                                                     |  |  |

| B19       | 1       | DETLVL4  | <ol> <li>The actual value is 8 times the value set in this field.</li> </ol>                                                |  |  |

| B20       | 0       | DETLVL5  | 5. MSb is B22; LSb is B15                                                                                                   |  |  |

| B21       | 0       | DETLVL6  | Example:<br>DETLVL[7:0] = 16 $\rightarrow$ Threshold: ±16 * 8 = ±128 ADC Value                                              |  |  |

| B22       | 0       | DETLVL7  | DETLVL[7:0] = $100 \rightarrow$ Threshold : $\pm 100 * 8 = \pm 800$ ADC Value                                               |  |  |

| B23       | 0       | TRIGOM   | Trigger Output Mode:<br>Disabled = 0; Enabled = 1                                                                           |  |  |

| B24       | 1       | FSTEP0   | Digital Band-Pass Filter Step Selection:<br>Step 1 = 01; Step 2 = 11; Step 3 = 00                                           |  |  |

| B25       | 1       | FSTEP1   | (See section 14 for more details)                                                                                           |  |  |

| B26       | 0       | FILSEL0  | Digital Band-Pass Filter Type Selection:                                                                                    |  |  |

| B27       | 0       | FILSEL1  | Type A = 111; Type B = 000; Type C = 001; Type D = 010<br>Direct = 011 (Band-Pass Filter Bypassed)                          |  |  |

| B28       | 0       | FILSEL2  | (See section 14 for more details)                                                                                           |  |  |

| B29 – B31 | 0       | Reserved | These bits are reserved and should be set to 0.                                                                             |  |  |

| B32 – B39 | 0       | Reserved | These bits are reserved and should be set to 0.                                                                             |  |  |

| B40 – B47 | 0       | Reserved | These bits are reserved and should be set to 0.                                                                             |  |  |

| B48 – B55 | 0       | Reserved | These bits are reserved and should be set to 0.                                                                             |  |  |

### Table 4 - Configuration Register Bit Definitions

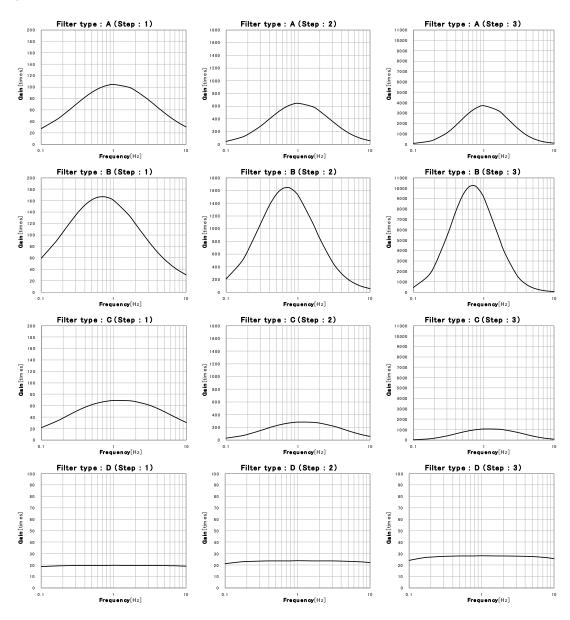

# **14 Digital Bandpass Filter Characteristics**

Figure 17 - Band-Pass Filter Characteristics

| Filter Type | High-Pass    | Low-Pass     | Typical Gain @ 1Hz (Linear) |        |        |

|-------------|--------------|--------------|-----------------------------|--------|--------|

|             | Cut-off (Hz) | Cut-off (Hz) | Step 1                      | Step 2 | Step 3 |

| А           | 0.4          | 2.7          | 104.7                       | 642.8  | 3713.7 |

| В           | 0.3          | 1.5          | 160.7                       | 1521.2 | 9134.6 |

| С           | 0.3          | 5.0          | 69.0                        | 279.7  | 1067.9 |

| D           | 0.01         | 100.0        | 19.7                        | 23.6   | 28.1   |

| Table 5 - | Band-Pass | Filter | Parameters |

|-----------|-----------|--------|------------|

|-----------|-----------|--------|------------|

# **15 Electrical Characteristics**

#### **15.1 Absolute Maximum Ratings**

Stresses greater than those listed in Table 6 can cause permanent damage to the device. These ratings are stress ratings only. Operation of the device at any condition outside those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods can affect device reliability.

$Ta = 25^{\circ}C$  unless otherwise specified.

|                       |      | •                     |       |

|-----------------------|------|-----------------------|-------|

| Parameter             | Min  | Max                   | Units |

| Supply voltage on VDD | -0.3 | +6.5                  | V     |

| Input Voltage         | -0.3 | V <sub>DD</sub> + 0.3 | V     |

| Input Current         | -10  | +10                   | mA    |

| Output Voltage        | GND  | V <sub>DD</sub>       | V     |

| Output Current        | -4.0 | +4.0                  | mA    |

| Operating Temperature | -40  | +85                   | °C    |

| Storage Temperature   | -40  | +85                   | °C    |

|                       |      |                       |       |

#### Table 6 - Absolute Maximum Ratings

### **15.2 DC Characteristics**

Ta =  $25^{\circ}C \pm 5^{\circ}C$  unless otherwise specified.

#### Table 7 - DC Characteristics

| Symbol          | Parameter                | Specification              | Conditions                                                             |

|-----------------|--------------------------|----------------------------|------------------------------------------------------------------------|

| Vdd             | Supply Voltage           | 1.8 V to 5.5 V             | -                                                                      |

| Idd             | Supply Current           | Мах: 5.0 µА<br>Тур: 3.0 µА | V <sub>DD</sub> = 3.0V<br>Excluding external I2C pull-up<br>resistors. |

| V <sub>DR</sub> | Data Retention Voltage   | Min: 1.8 V                 | Required supply voltage to maintain register setting data              |

| VIH             | High Level Input Voltage | Min: V <sub>DD</sub> x 0.9 |                                                                        |

| VIL             | Low Level Input Voltage  | Max: V <sub>DD</sub> x 0.1 |                                                                        |

### 15.3 I<sup>2</sup>C Interface

| Symbol               | Parameter                                              |       | Specification |           |        | Units |

|----------------------|--------------------------------------------------------|-------|---------------|-----------|--------|-------|

|                      |                                                        | Stand | ard Mode      | Fast Mode |        |       |

|                      |                                                        | Min.  | Max.          | Min.      | Max.   |       |

| Fscl                 | SCL Clock Frequency                                    | 0     | 100           | 0         | 400    | KHz   |

| TLOW:SCL             | SCL Low Time                                           | 4.7   | -             | 1.3       | -      | μs    |

| Thigh:scl            | SCL High Time                                          | 4.0   | -             | 0.6       | -      | μs    |

| THOLD:START          | Hold time for Repeated<br>START condition              | 4.0   | -             | 0.6       | -      | μs    |

| TSU:START            | Set-up time for repeated START condition               | 4.7   | -             | 0.6       | -      | μs    |

| THOLD:DATA           | Data hold time                                         | 0(3)  | 3.45(4)       | 0(3)      | 0.9(4) | μs    |

| T <sub>SU:DATA</sub> | Data set-up time                                       | 250   | -             | 100       | -      | ns    |

| TSU:STOP             | Set-up time for STOP condition                         | 4.0   | -             | 0.6       | -      | μs    |

| T <sub>R</sub>       | Rise time of both SDA and SCL signals                  | -     | 1000          | 20        | 300    | ns    |

| T <sub>F</sub>       | Fall time of both SDA and SCL signals                  | -     | 300           | -         | 300    | ns    |

| TBUF                 | Bus free time between a<br>STOP and START<br>condition | 4.7   | -             | 1.3       | -      | μs    |

| Св                   | Capacitive load for each bus line                      |       | 400(2)        |           | 400(2) | pF    |

#### Table 8 - I<sup>2</sup>C Interface

Notes:

(1) The  $I^2C$  bus specifications in Table 8 are based on the VDD and GND level within the supply voltage range.

(2)  $C_B$  is total capacitance of one bus line.

(3) A device must internally provide a hold time of at least 300nsec. For the SDA signal to bridge the undefined region of the falling edge of SCL.

(4) The maximum  $T_{HOLD:DATA}$  has only to be met if the device does not stretch the Low period ( $T_{LOW:SCL}$ ) of the SCL signal.

### **15.4 Sensor Characteristics**

Ta =  $25 \pm 5$  °C unless otherwise specified.

| Symbol | Parameter                             | Specification                                    | Conditions                                                                |

|--------|---------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------|

| Sout   | Signal Output                         | Min: 1200 counts (p-p)<br>Typ: 1800 counts (p-p) | Register Bit [24:25]=11<br>Register Bit [26:28]=000                       |

| Νουτ   | Noise Output                          | Max: 250 counts (p-p)<br>Typ: 100 counts (p-p)   | Register Bit [24:25]=11<br>Register Bit [26:28]=000                       |

| Dres   | Data Output Resolution                | 12 Bit                                           | MSB is sign(+/-) bit                                                      |

| Тсус   | Data Output Data Update<br>Cycle Rate | Typ. 9.5 msec.                                   | _                                                                         |

| TSTAB  | Stability Time                        | Max: 30 sec. (See section 11)                    | After applying V <sub>DD</sub> and after changing digital filter setting. |

| FOV    | Field of View                         | X Axis: 148°<br>Y Axis: 136°                     | See Figure 3                                                              |

| -      | Filter Substrate                      | Silicon                                          |                                                                           |

| λ(5%)  | Cut on Wavelength                     | 5 ±1 μm                                          |                                                                           |

| FT     | Filter Transmittance                  | 70%                                              | Average from 8 µm to 13 µm                                                |

#### **Table 9 - Sensor Characteristics**

### **15.5 Environmental Characteristics**

#### **Table 10 - Environmental Characteristics**

| Symbol             | Parameter                            | Specification  | Conditions |

|--------------------|--------------------------------------|----------------|------------|

| T <sub>OPP</sub>   | Recommended Operating<br>Temperature | -40 to +80 °C  |            |

| T <sub>STORE</sub> | Recommended Storage Temperature      | -40 to +80 °C  |            |

| H <sub>OPP</sub>   | Operating Humidity                   | 95 %RH or less | 30 °C      |

| HSTORE             | Storage Humidity                     | 95 %RH or less | 30 °C      |

### **15.6 RoHS Compliance**

This product conforms to the RoHS Directive in force at the date of issuance of this product specification.

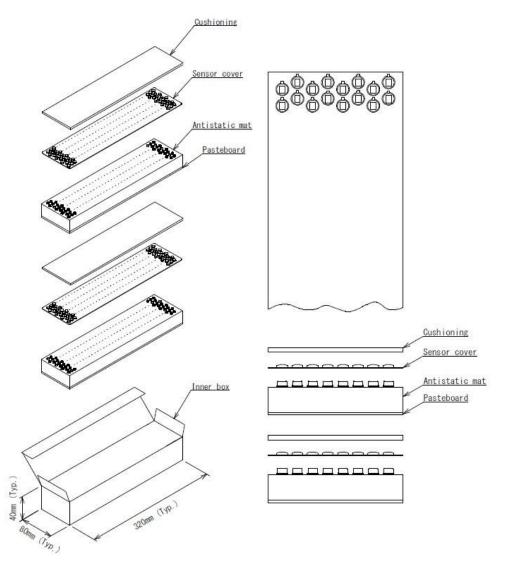

# 16 Packaging

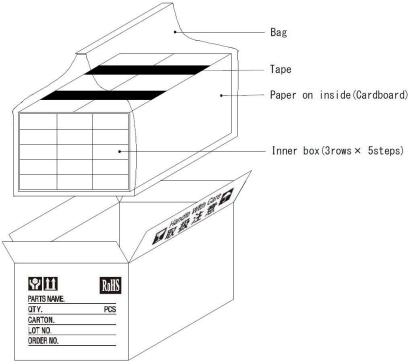

The ZDP323B Digital PIR Sensor is shipped in sheets of 200 pieces, packed in boxes as shown in Figure 18 through Figure 20. The sheets are packed in an inner-box (2 sheets/box = 400 pieces) and 15 inner-boxes are packed in an outer-box for a total of 6,000 pieces per box.

### 16.1 Sheet and Inner-Box Packaging

- 1) Standard sheet quantity: 200 pieces

- 2) Standard inner-box quantity: 2 Sheets (400 pieces)

Figure 18 – Sheet & Inner-Box Packaging

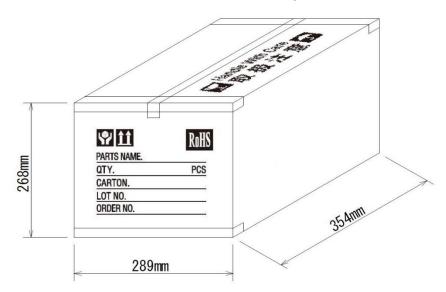

3) Standard Box Quantity: 6,000 pieces (15 Inner-Boxes)

Figure 19 – Outer-Box Packaging

4) The Standard Outer-Box dimensions are shown in Figure 20

Figure 20 - Standard Outer-Box Dimensions

# **17 Usage Restrictions and Precautions**

This section presents restrictions and precautions that apply to Zilog pyroelectric sensors.

#### **17.1 Design Restrictions and Precautions**

If used for outdoor applications, be sure to use a suitable UV optical filter and drip-proof, anti-dew construction. This sensor is designed for indoor use. In cases where secondary accidents due to operational failure or malfunctions can be anticipated, add a failsafe function to the design.

### **17.2 Usage Restrictions and Precautions**

To ensure continued proper operation of the sensor, do not operate it under any of the following conditions:

- Rapid environmental temperature changes

- Strong shocks or vibrations

- In places where there are obstructing materials (glass, fog, etc.) through which infrared rays cannot pass within the detection area

- In fluids, corrosive gases, and sea breezes

- Under continual high-humidity atmospheric conditions

- Exposed to direct sunlight or automobile headlights without appropriate lens filter

- Exposed directly to forced-air currents from a heater or air conditioner

#### **17.3 Handling and Storage Restrictions and Precautions**

To prevent sensor malfunctions, operational failure, appearance damage, or any deterioration of its characteristics, do not expose the sensor to any of the following, or similar, handling and storage conditions:

- Strong shocks or continual vibrations

- Static electricity or strong electromagnetic waves

- High temperature and humidity over extended periods

- Corrosive gases or sea breezes

- Dirty and dusty environments that may contaminate the optical window

- Ultrasonic cleaning

### **17.4 Assembly Restrictions and Precautions**

Use soldering iron with controlled heat when soldering

• Avoid extended durations of heat on the sensors' pins. Exposure to excessive heat may cause deterioration of the sensor performance (e.g., durations beyond 5 seconds at 350°C)

# **18 Related Documents**

The documents associated with the ZDP323B Digital PIR sensor are listed below. Each of these documents, and others can be obtained from the <u>ZMOTION Product Page</u> on the Zilog website: <u>http://www.zilog.com</u>.

| Document Number | Description                      |

|-----------------|----------------------------------|

| PB0266          | Digital PIR Sensor Product Brief |

| PB0263          | PIR Sensor Product Brief         |

| PB0264          | ZMOTION Lens Product Brief       |

#### **Table 11 - Related Documents**

### **19 Customer Support**

To share comments, get your technical questions answered, or report issues you may be experiencing with our products, please visit Zilog's <u>Technical Support</u> page.

This publication is subject to replacement by a later edition. To determine whether a later edition exists, please visit the Zilog website at <u>http://www.zilog.com</u>.