**Application Note**

# Signed Math on the Z8 MCU

# The Z8 Flag Register and Signed Math Instructions

# **Table of Contents**

| Introduction             |

|--------------------------|

| The Application          |

| Schematic                |

| Sample Code              |

| Appendix A 15            |

| Appendix B               |

| References 17            |

| Information Integrity 18 |

| Document Disclaimer      |

# Acknowledgments

Project Lead Engineer Steve Narum System and Code Development: Steve Narum

### Introduction

The Z8 MCU's architecture provides ease-of-use for signed math functions. The CPU's flag register and signed mathematical instructions allow a programmer to work easily with signed values of nearly any length.

In other architectures, there is little or no provision for signed math, programmers must work around this limitation. For example, numbers can be manipulated as unsigned values, with the actual sign stored as a software flag. The flow of the program is then modified according to the sign. This technique adds significant overhead in both execution speed and program memory size. Often the application requires a more expensive processor that has more ROM or hardware math-execution units.

The ability to recognize signed data makes the Z8 MCU valuable for many functions. In a positioning motor control application, the difference between the current and requested positions requires both a magnitude and a sign to indicate the direction the motor should be turning.

# The Application

In this application note, a simple motor-control algorithm is demonstrated using one of the lowest-cost ZiLOG chips—the Z86E02. This small processor has a bare minimum of OTP code memory and only the basic set of peripherals. See the Application Note titled <u>A DC Motor</u> <u>Controller Using the ZiLOG Z86E06 MCU</u>, for a discussion of motor control basics.

The motor control application uses a PWM output to drive the winding of a motor either clockwise or counter-clockwise. The load's absolute position is encoded by a rheostat or similar device that provides a DC voltage output proportional to the position. This voltage is read by an external analog-to-digital converter, and the Z8 uses a microwire interface to read an 8-bit position value. An external microwire input allows the external system to request an exact position for the motor. There are three limit switches that stop the motor if any are closed.

For each cycle of the software, the present position of the motor is read from the ADC and a positional error value is calculated. This error value requires at least nine bits to store the signed value. The requested position and the actual position could be on either end of the range, and require a magnitude of eight bits. The error could be in either direction from the requested position (either positive or negative), and requires one sign bit. This situation causes problems for many processors that cannot provide a simple way of executing signed math. Some processors cannot execute signed math on more than eight bits (7 magnitude bits, plus 1 sign bit). Others do not support signed math at all.

The Z8 processor allows a designer to store the error as a 16-bit signed number and apply mathematical functions to it with ease. Addition and subtraction are provided in the ADD and SUB instructions and are extended to multiple byte values by the ADC and SBC instructions. The sign bits are automatically handled by the Arithmetic Logic Unit (ALU). An example from the software is shown below.

| CLR | ERR_HI      |

|-----|-------------|

| LD  | ERR_LO,POSR |

| SUB | ERR_LO,POSA |

| SBC | ERR_HI,#%00 |

Two 8-bit unsigned numbers, one from the ADC and the other input externally, are subtracted into a 16-bit signed result. Nothing more is required. The Z8's ALU automatically sets the sign flag after the subtraction to the sign of the result. If necessary, a jump statement can follow immediately to perform a different task, depending on the direction of the error. No compare or test instruction is necessary.

Addition works equally well. Both addition and subtraction can be extended to more bytes by adding more ADC or SBC instructions, one per byte.

Multiplication by successive addition is also a common function in software that deals with positioning controls. The basic technique of multiplying two 8-bit unsigned values into an unsigned 16-bit result is shown in <u>Appendix A</u>. The code segment below demonstrates how this idea can be extended to multiplication of a signed 16-bit number (ERR\_HI, ERR\_LO) by an unsigned 8-bit scalar RES\_LO into a signed 24-bit result (RES\_HI, RES\_MD, RES\_LO).

| MULT_8x16s: | LD   | PULSE_CNT,#%08      |  |  |  |  |

|-------------|------|---------------------|--|--|--|--|

|             | CLR  | RES_HI              |  |  |  |  |

|             | CLR  | RES_MD              |  |  |  |  |

|             | RRC  | RES_LO              |  |  |  |  |

| MULT_LOOP:  | JR   | NC,MULT_SHIFT       |  |  |  |  |

|             | ADD  | RES_MD,ERR_LO       |  |  |  |  |

|             | ADC  | RES_HI,ERR_HI       |  |  |  |  |

| MULT_SHIFT: | SRA  | RES_HI              |  |  |  |  |

|             | RRC  | RES_MD              |  |  |  |  |

|             | RRC  | RES_LO              |  |  |  |  |

|             | DJNZ | PULSE_CNT,MULT_LOOP |  |  |  |  |

|             | RET  |                     |  |  |  |  |

After exiting this multiplication loop, the flags reflect the resulting value's sign. Subsequently, decisions can be made without requiring a redundant test.

The Z8 performs signed division by two equally well, and requires only two bytes for the SRA instruction. By chaining the SRA into RRC instructions on the lower bytes, longer values can be divided easily. Following is an example from the code:

|           | LD   | PULSE_CNT,#%04      |

|-----------|------|---------------------|

| DIV_LOOP: | SRA  | RES_HI              |

|           | RRC  | RES_MD              |

|           | RRC  | RES_LO              |

|           | DJNZ | PULSE_CNT, DIV_LOOP |

This code segment demonstrates a 24-bit signed value being divided by 16. When the ALU sets the flags on the last RRC, the DJNZ instruction does not modify the flags. This condition allows the programmer to use the flags in a jump instruction without testing first. Care must be taken, however, since the flags are the result of the most recent operation. The Z flag, for example, would indicate that the lowest byte is 0 after the division; it does not indicate that the entire 24-bit value is 0.

Also, if rounding is necessary, the carry flag can be treated as a half bit. The last RRC instruction shifts a bit into the carry flag only if the prior value was odd. A simple construct automatically rounds the result to the nearest integer value, as in the following example:

. RRC RES\_LO DJNZ PULSE-CNT, DIV\_LOOP ROUND: ADC RES\_LO,#0 ADC RES\_MD,#0 ADC RES\_HI,#0

Performing division on signed numbers by a number that is not a multiple of two is not as straightforward. Unfortunately, the task is complex enough that it becomes simpler to change the sign, perform an unsigned divide, then restore the sign. <u>Appendix B</u> describes a 16 x 8 divider that can be extended to longer values if necessary.

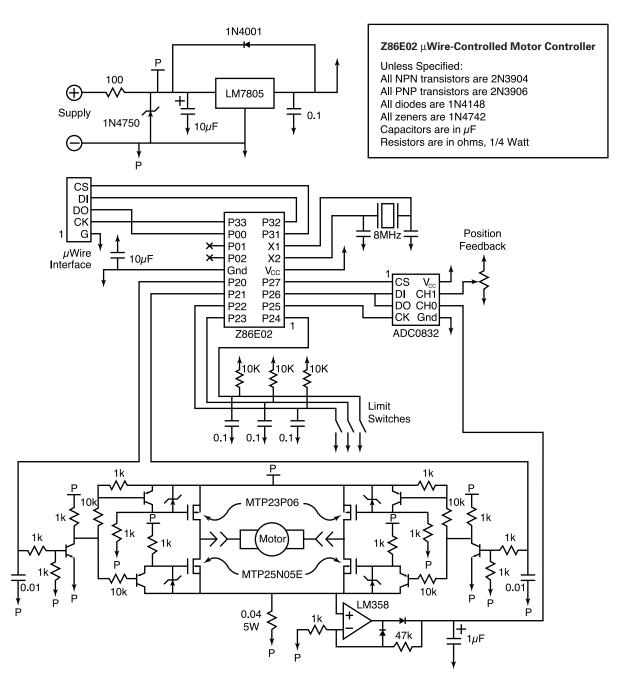

Figure 1 is a schematic of the Z86E02 microwire-controlled motor controller. Following Figure 1 is a signed math demonstration code for the Z86E02 operating at 8 MHz.

# Schematic

Figure 1. Z86E02 µWire-Based Motor Controller

# **Sample Code**

; ; ; Signed math demonstration code on the <code>Z86E02</code> @ <code>8MHz</code> ;

| .INCLUDE     | MACROS.   | H       | ;    | Include some useful macros |

|--------------|-----------|---------|------|----------------------------|

|              |           |         |      |                            |

| ; Macros ind | clude: WD | r, sete | BIT, | CLRBIT, JNZ                |

|              |           |         |      |                            |

| MATH GROUP   | .EQU      | 810     |      |                            |

| BIT CNT      | .EQU      | R0      | ;    | uWire bit counter          |

| PULSE CNT    | .EQU      | R1      | ;    | PWM pulse & math counter   |

| ERR HI       |           |         |      | Error high byte            |

| ERR LO       | .EQU      | R3      | ;    | Error low byte             |

| ERR WORD     | .EQU      | RR2     | ;    | Error as a word            |

| OERR HI      | .EQU      | R4      | ;    | Old error high byte        |

| OERR LO      | .EQU      | R5      | ;    | Old error low byte         |

| RES HIW      | .EQU      | RR6     | ;    | Math result, high word     |

| RES HI       | .EQU      | R6      | ;    | Math result, high byte     |

| RES MD       | .EQU      | R7      | ;    | Math result, mid byte      |

| RES LO       | .EQU      | R8      | ;    | Math result, low byte      |

| ACCUM        | .EQU      | R9      | ;    | Error accumulator          |

| POSR         | .EQU      | R10     | ;    | Requested position         |

| POSA         | .EQU      | R11     | ;    | Actual position            |

| HI TIME      | .EQU      | R12     | ;    | PWM high time              |

| LO TIME      | .EQU      | R13     | ;    | PWM low time               |

| · (snare)    | EOU       | R14     |      |                            |

; (spare) .EQU R14 STATUS .EQU R15 ; Status flags register

; Bit masks for STATUS register

| MOVING | .EQU | 0010000B | ; | Moving/stopped flag     |

|--------|------|----------|---|-------------------------|

| PWM    | .EQU | 0100000B | ; | PWM high/low state flag |

; Port pin bit masks

| outputs (P20,1) |

|-----------------|

| puts (P22,3,4)  |

|                 |

|                 |

| (P27)           |

|                 |

| (P00)           |

| ect (P31)       |

| P32)            |

| (3)             |

|                 |

| ; P2M bit mas               | sks                                  |                                     |                                                                             |                     |                                                                     |

|-----------------------------|--------------------------------------|-------------------------------------|-----------------------------------------------------------------------------|---------------------|---------------------------------------------------------------------|

| MOVECW<br>MOVECCW<br>DATAIN | .EQU<br>.EQU<br>.EQU<br>.EQU<br>.EQU | 000111101<br>000111011<br>010111111 | B ; Disable<br>B ; Enable (<br>B ; Enable (<br>B ; Recv dat<br>B ; Send dat | CW T<br>CCW<br>ta ( | winding<br>on AD_DATA                                               |

| ; Constants                 |                                      |                                     |                                                                             |                     |                                                                     |

| KP<br>KI<br>KD              | .EQU                                 | 802 ; :                             | Integral gai                                                                | in d                | ain constant<br>constant<br>ain constant                            |

| ; Macro defin               | nitions                              |                                     |                                                                             |                     |                                                                     |

| READ_POS                    | .MACRO                               |                                     | Get position<br>Macro READ_H                                                |                     | rom ADC<br>uses the uWire interface to read                         |

| LD                          |                                      | ; ;<br>; ;<br>#%04 ; ;              | position val<br>an external<br>unsigned, PC<br>3 header bit<br>Enable uWire | ADC<br>DSA<br>ts -  | C. The returned value is an 8 bit<br>+ start ADC                    |

| SETBIT                      | P2, AD_DA                            | TA ; ?                              | Send 3 1's                                                                  | (sta                | art, read, ch1)                                                     |

| STARTBITS:                  | DJNZ<br>LD                           | BIT_CNT<br>P2M                      |                                                                             |                     | Check bit counter<br>Make P26 input on last                         |

| SENDBIT:                    | NOP                                  | P2, AD_CLI<br>P2, AD_CLI            | K<br>STARTBITS                                                              | ;;;;;               | Fix bit counter<br>Raise clock<br>Wait<br>Drop clock                |

| GETBIT:                     | RCF<br>SETBIT<br>TM<br>JR            | P2,AD_CLI<br>P2<br>Z                | K<br>#AD_DATA<br>RECV ZERO                                                  | ;                   | Assume zero<br>Raise clock<br>Test data input                       |

| RECV_ZERO:                  | SCF<br>CLRBIT<br>RLC<br>DJNZ         | P2,AD_CLI<br>POSA<br>BIT_CNT        | —                                                                           | ;<br>;              | Nope, it's a one<br>Drop clock<br>Rotate bit into place<br>Next bit |

|                             | SETBIT<br>LD                         | P2,AD_CS<br>P2M                     | #DATAOUT                                                                    |                     | Deselect the ADC<br>P26 back to output                              |

.ENDM

#### ; Calculation macros

| C_ERROR | .MACRO<br>CLR<br>LD<br>SUB<br>SBC<br>.ENDM        | ; Calcul<br>ERR_HI<br>ERR_LO<br>ERR_LO<br>ERR_HI     |                  | ;<br>; | error<br>Stuff 8 bit unsigned into<br>16 bit signed<br>Find difference (POSR - POSA)                                                                      |

|---------|---------------------------------------------------|------------------------------------------------------|------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| C_PROP  | .MACRO<br>LD<br>CALL<br>CALL<br>LD<br>LD<br>.ENDM | RES_LO<br>MULT_8×1<br>DIV_LIMI<br>HI_TIME<br>LO_TIME | Т                | ;;;;   | Calc proportional part<br>Put gain in multiplier<br>ERR is the multiplicand<br>Divide by 16 and limit to +/-100<br>Stuff signed 24 bits<br>into signed 16 |

| C_INT   | .MACRO                                            | EDD IO                                               | EDD IO           |        | Calc integral part<br>(Possible values are FF02h to                                                                                                       |

| 00FFh)  | OR                                                | ERR_LO                                               | ERR_LO           | ,      | (POSSIDIE Values ale Prozin co                                                                                                                            |

| ,       | JR                                                | Ζ                                                    | ADDINT           | ;      | Don't change ACCUM if ERR = 0                                                                                                                             |

|         | OR                                                | ERR_HI                                               | ERR_HI           | ;      | Is ERR + or -?                                                                                                                                            |

|         | JR                                                | MI                                                   | MNS_1            |        |                                                                                                                                                           |

| PLS_1:  | CP                                                | ACCUM                                                | #100             | ;      | $ACCUM \ge 100?$                                                                                                                                          |

|         | JR<br>ADD<br>JR                                   | GE<br>ACCUM<br>ADDINT                                | ADDINT<br>#KI    | ;      | No, ACCUM += KI                                                                                                                                           |

| MNS_1:  | CP<br>JR                                          | ACCUM<br>LE                                          | #-100<br>Addint  | ;      | ACCUM <= -100?                                                                                                                                            |

|         | SUB                                               | ACCUM                                                | #KI              | ;      | No, ACCUM -= KI                                                                                                                                           |

| ADDINT: | ADD<br>ADC<br>.ENDM                               | LO_TIME<br>HI_TIME                                   | ACCUM<br>#%00    | ;      | Add ACCUM into the sum                                                                                                                                    |

| C DIFF  | .MACRO                                            | ; Calc d                                             | ifferential p    | oai    | rt                                                                                                                                                        |

|         | LD                                                | RES HI                                               | ERR HI           | -      | Save ERR                                                                                                                                                  |

|         | LD                                                | RES_LO                                               | ERR_LO           |        |                                                                                                                                                           |

|         | SUB                                               | ERR_LO                                               | OERR_LO          | ;      | Subtract (ERR - OERR)                                                                                                                                     |

|         | SBC                                               | ERR_HI                                               | OERR_HI          |        | Undate OFPD                                                                                                                                               |

|         | LD<br>LD                                          | OERR_LO<br>OERR HI                                   | RES_LO<br>RES HI | ,      | Update OERR                                                                                                                                               |

|         | LD                                                | RES LO                                               | #KD              | ;      | Load multiplier                                                                                                                                           |

|         | CALL                                              | MULT 8x1                                             |                  |        | Take deltaERR * KD                                                                                                                                        |

|         | CALL                                              | DIV_LIMI                                             |                  |        | Divide by 16 and limit to $+/-100$                                                                                                                        |

|         | ADD                                               | RES_LO                                               | LO_TIME          |        | And add the sum into it                                                                                                                                   |

|         | ADC                                               | RES_MD                                               | HI_TIME          | ;      | (RES used in SET_PWM)                                                                                                                                     |

|         | .ENDM                                             |                                                      |                  |        |                                                                                                                                                           |

# Signed Math on the Z8 MCU

| SET PWM     | .MACRO    |              |              |    | Set up PWM and enable windings    |

|-------------|-----------|--------------|--------------|----|-----------------------------------|

| SET_EMM     | CALL      | ттмтт 10     | 0            |    | Limit sum to +/-100               |

|             |           | LIMIT_10     |              |    |                                   |

|             | JR        | PL<br>DDG IG | POS_SUM      |    | RES + or - ?                      |

| NEG_SUM:    | COM       | RES_LO       |              | ;  | Change sign                       |

|             | INC       | RES_LO       |              |    |                                   |

|             | LD        | P2M          | #MOVECCW     | ;  | Enable CCW winding                |

|             | JR        | CALC_PWM     |              |    |                                   |

| POS_SUM:    | LD        | P2M          | #MOVECW      | ;  | Enable CW winding                 |

| CALC PWM:   | LD        | HI TIME      | RES LO       | ;  | PWM high time = RES               |

| —           | LD        | LO TIME      | #100         |    |                                   |

|             | SUB       | LO TIME      | RES LO       | ;  | PWM low time = (100 - RES)        |

|             | JR        | NZ           | СНЕСК НІ     |    |                                   |

|             | INC       | LO TIME      |              |    | If zero, add one                  |

| CHECK HI:   | INC       | _            |              | '  |                                   |

| CHECK_HI.   |           | HI_TIME      | DUM DONE     |    | Zerred                            |

|             | DJNZ      | HI_TIME      | PWM_DONE     |    | Zero?                             |

|             | INC       | HI_TIME      |              | ;  | If zero, add one                  |

| PWM_DONE:   |           |              |              |    |                                   |

|             | .ENDM     |              |              |    |                                   |

|             |           |              |              |    |                                   |

|             |           |              |              |    |                                   |

| ; Interrupt | vector ta | ble          |              |    |                                   |

|             |           |              |              |    |                                   |

|             | .ORG      | 800          |              |    |                                   |

|             |           |              |              |    |                                   |

|             | JR        | Init         |              | ;  | Reset the part                    |

| ; Sacrifice |           |              | set if PC wr |    |                                   |

| ;           | .WORD     | Init         |              |    | IRQ0 (P32f)                       |

| /           | .WORD     |              |              | ΄. | IRQ1 (P33f)                       |

|             |           |              | F            | ΄. |                                   |

|             | .WORD     |              | E.           |    | IRQ2 (P31f)                       |

|             | .WORD     | Init         |              | ;  | IRQ3 (P31r)                       |

|             | .WORD     |              | _            | ;  | IRQ4 (TO)                         |

|             | .WORD     | T1_SERVI     | CE           | ;  | IRQ5 (T1)                         |

|             |           |              |              |    |                                   |

|             | .ORG      | %0C          |              |    |                                   |

|             |           |              |              |    |                                   |

| Init:       | WDT       |              |              |    |                                   |

|             | LD        | SPL          | #%40         | ;  | Stack at end of CO2's RAM         |

|             | LD        | SPH          | #%3F         | ;  | Use SPH as pointer to clear RAM   |

|             | SRP       | #%F0         |              |    | ±                                 |

| CLR REGS:   | CLR       | @R14         |              | :  | Clear a register                  |

| <u> </u>    | DJNZ      | R14          | CLR REGS     | ,  | 01001 0 10910001                  |

|             | DONZ      | 1/1 4        |              |    |                                   |

|             | ТЪ        | DO1M         | # ° ∩ 1      |    | PO is an output                   |

|             | LD        | P01M         | #%04         |    | PO is an output                   |

|             | LD        | P2M          | #NOMOVE      |    | P20-4 = in, P25-7 = out           |

|             | LD        | РЗМ          | #801         | ;  | P3 = digital, P2 = push-pull      |

|             |           |              |              |    |                                   |

|             | LD        | PRE1         | #%06         | ;  | T1 int clk, single shot, div by 1 |

|             | CLR       | TMR          |              | :  | Disable both timers               |

|              | LD<br>CLR<br>EI | IPR<br>IMR | #%01         | ; | IRQ5 > IRQ2                                  |

|--------------|-----------------|------------|--------------|---|----------------------------------------------|

|              | OR              | IMR        | #00100100B   | ; | T1 and P31 only                              |

|              | SRP             | #MATH_GR   | OUP          |   |                                              |

| MAIN:        | WDT             |            |              |   |                                              |

|              | TCM             | P2         | #SWITCHES    | ; | Limit switch closed?                         |

|              | JR              | ΝZ         | MAIN         | ; | Wait until it's opened                       |

| STOPPED:     | OR              | POSR       | POSR         |   | Was stop requested?                          |

|              | JR              | Z          | MAIN         | ; | Wait for new request                         |

| MOVIN:       | ТМ              | STATUS     | #MOVING      |   | Already moving?                              |

|              | JR              | ΝZ         | MAIN         | ; | Wait until done                              |

| CALC_MOVE:   | DI              |            |              | ; | No uWire IRQ during READ_POS                 |

|              | READ_POS        |            |              | ; | Get current position from ADC                |

|              | C_ERROR         |            |              |   | Calculate positional error                   |

|              | EI              |            |              |   | Recv OK while doing the math                 |

|              | C_PROP<br>C INT |            |              |   | Calc proportional part<br>Calc integral part |

|              | C_INI<br>C DIFF |            |              |   | Calc differential part                       |

|              | SET_PWM         |            |              |   | Set up PWM and enable windings               |

| MOVE:        | SETBIT          | STATUS,M   | OVINC        |   | Flag that we're moving                       |

| 110 1 1.     | LD              | PULSE CN   |              |   | (dec) 100 pulses per move                    |

|              | OR              | IRQ        | #%10         |   | Force IRQ4                                   |

|              | JP              | MAIN       |              |   | -                                            |

|              |                 |            |              |   |                                              |

| ; Math subro | utines          |            |              |   |                                              |

| MULT_8x16s:  |                 |            |              |   | Multiply 8 bit unsigned by 16 bit            |

|              |                 |            |              |   | signed.                                      |

|              |                 |            |              |   | 24 bit signed result. 8 bit                  |

|              | LD              | PULSE CN   | Ͳ #⊱∩ጸ       |   | destroyed.<br>Loop 8 times                   |

|              | CLR             | RES HI     | 1 #000       |   | Start with clear sum                         |

|              | CLR             | RES MD     |              | ' | Starte wren erear sam                        |

|              | RRC             | RES LO     |              | ; | Rotate 1st bit into C, save C                |

| MULT_LOOP:   | JR              | NC –       | MULT_SHIFT   |   |                                              |

|              | ADD             | RES_MD     | ERR_LO       | ; | Add in ERR * 256                             |

|              | ADC             | RES_HI     | ERR_HI       |   |                                              |

| MULT_SHIFT:  | SRA             | RES_HI     |              | ; | Divide result by 2                           |

|              | RRC             | RES_MD     |              |   |                                              |

|              | RRC<br>DJNZ     | RES_LO     | ת ∩ר ד תווות |   |                                              |

|              |                 | LOTOF CN   | T MULT_LOOP  |   |                                              |

RET DIV LIMIT: ; Divide signed 24 bit by 16 and ; limit result to +/-100. ; Returns a 16 bit signed with RES HI ; containing garbage. PULSE CNT #%04 ; Four shifts = div by 16 LD RES HI DIV LOOP: SRA ; Divide by 2 RRC RES MD RRC RES LO DJNZ PULSE CNT DIV LOOP LIMIT 100: INCW RES HIW ; See if upper word is FFh Z JR RES NEG DECW RES HIW ; See if upper word was 00h Ζ RES POS JR RES LO #100 ; Limit to 100 LIMIT LO: LD CLR RES MD RES HI ; Should it be + or - ? OR RES HI JR ΡL LIMIT DONE COM res md COM RES LO ; Fix the sign INC RES\_LO LIMIT DONE: RET RES NEG: DECW RES HIW ; Restore sign RES LO RES LO ; See if LO byte is negative OR PL ; If not, actual value is too nega-JR LIMIT LO tive СΡ RES LO #-100 ; If so, test magnitude JR LTLIMIT LO JR LIMIT EXIT ; It's OK, exit RES POS: СΡ RES LO #100 ; Can use LO as unsigned, check mag JR UGT LIMIT LO ; It's OK, exit LIMIT EXIT: OR RES HI RES HI ; Fix the sign flag. CP goofs it up. RET ; Interrupt service routines T1 SERVICE: ; Software PWM timer. TΜ STATUS #PWM ; Which half are we on? JR Z LO PULSE HI PULSE: P2,WINDINGS ; Make windings high SETBIT SETBIT STATUS, PWM ; Flag we're doing high

; And start

LD

AND IRET T1 HI\_TIME

TMR

#%0C

# Signed Math on the Z8 MCU

| LO_PULSE:<br>END_MOVE: | CLRBIT<br>CLRBIT<br>DJNZ<br>LD<br>CLRBIT<br>IRET | STATUS, P<br>PULSE_CN<br>P2M | NGS<br>WM<br>I FIRE_LOW<br>#NOMOVE<br>OVING | ;<br>;<br>; |                                      |

|------------------------|--------------------------------------------------|------------------------------|---------------------------------------------|-------------|--------------------------------------|

| FIRE_LOW:              | LD<br>AND<br>IRET                                | T1<br>TMR                    | LO_TIME<br>#%0C                             |             | Load timer<br>And start              |

| MICROWIRE:<br>catches  |                                                  |                              |                                             |             | Read microwire input. WDT<br>timeout |

|                        | WDT                                              |                              |                                             |             | Start with a fresh WDT count         |

|                        | LD                                               | BIT_CNT                      | #%08                                        | ;           | Get eight bits                       |

| WAIT_DN:               | TM                                               | Р3                           | #MWCLK                                      | ;           | Wait for low uWire clock             |

|                        | JR                                               | NZ                           | WAIT_DN                                     |             | _                                    |

|                        |                                                  | PO,MWXMI                     |                                             |             | Assert ready                         |

| WAIT_UP:               |                                                  | P3                           |                                             | ;           | Wait for high uWire clock            |

|                        | JR                                               | Ζ                            | WAIT_UP                                     |             | -                                    |

|                        | RCF                                              |                              |                                             |             | Assume zero                          |

|                        | TM                                               | P3<br>Z                      | #MWREC                                      | ;           | Get data                             |

|                        | JR<br>SCF                                        | Z                            | NOT_ONE                                     |             | It's a one                           |

| NOT ONE.               |                                                  | DOCD                         |                                             |             |                                      |

| NOT_ONE:               | RLC<br>DJNZ                                      | POSR                         |                                             |             | Rotate it into position<br>Last bit? |

|                        | CLRBIT                                           | PO, MWXMI                    | _                                           |             |                                      |

|                        | INC                                              | PO, MWAMI<br>POSR            | Ţ                                           | '           | Deassert uWire ready                 |

|                        | DJNZ                                             | POSR                         | NOT ZERO                                    |             | See if POSR = 0                      |

|                        | LD                                               |                              |                                             |             | If so, stop the motor next TO        |

| NOT_ZERO:              | IRET                                             | 10101_01                     | - "                                         | ,           |                                      |

# **Appendix A**

The following module illustrates an efficient algorithm for the multiplication of two unsigned 8-bit values, resulting in a 16-bit product. The algorithm repetitively shifts the multiplicand right (using RRC), the result being a shift of the low-order bit into the carry flag. If a 1 is shifted out, the multiplier is added to the high-order byte of the partial product. As the high-order bits of the multiplicand are vacated by the shift, the resulting partial-product bits are rotated in. Thus, the multiplicand and the low byte of the product occupy the same byte. As a result, there is a savings of register space, code, and execution time.

```

; ARITH MODULE

; CONSTANT

; MULTIPLIER = R1

; PRODUCT_LO = R3

; PRODUCT_HI = R2

; COUNT = R0

; GLOBAL

; MULTIPLICATION PROCEDURE

* ******

; Purpose = To perform an 8-bit by 8-bit unsigned binary

multiplication.

;

;

; Input = R1 = multiplier

;

R3 = multiplicand

;

; Output = RR2 = product

R0 = destroyed

;

ENTRY:

ld

COUNT,#09H

;8 bits+1

clr

PRODUCT_HI

;Init High result byte

rcf

; CARRY = 0

LOOP: rrc

PRODUCT_HI

rrc

PRODUCT LO

NC,NEXT

jr

add

PRODUCT_HI,MULTIPLIER

NEXT: djnz

COUNT, LOOP

ret

```

# **Appendix B**

The following module illustrates an efficient algorithm for the division of a 16-bit unsigned value by an 8-bit unsigned value, resulting in an 8-bit unsigned quotient. The algorithm repetitively shifts the dividend left (using RLC). If the high-order bit shifted out is a 1, or if the resulting high-order dividend byte is greater than or equal to the divisor, the divisor is subtracted from the high byte of the dividend. As the low-order bits of the dividend are vacated by the shift left, the resulting partial-quotient bits are rotated in. Thus, the quotient and the low byte of the dividend occupy the same byte. As a result, there is a savings of register space, code, and execution time.

```

; ARITH MODULE

; CONSTANT

; COUNT = R0

; DIVISOR = R1

; DIVIDEND_HI = R2

; DIVIDEND_LO = R3

; GLOBAL

; DIVIDE PROCEDURE

; Purpose = To perform a 16-bit by 8-bit unsigned binary division.

; Input = R1 = 8-bit divisor

RR2 = 16-bit dividend

;

;

; Output = R3 = 8-bit quotient

R2 = 8-bit remainder

;

Carry flag = 1 if overflow

= 0 if no overflow

;

ENTRY:

ld

COUNT, #08H

;Loop counter

;Check if result fits in

;8 bits

DIVISOR, DIVIDEND_HI

ср

jr

UGT,LOOP

;CARRY = 0 FOR RLC)

;Won't fit. Overflow

scf

;CARRY = 1

ret

LOOP:

;Result fits. Go ahead

;with division

rlc

DIVIDEND LO

;DIVIDEND * 2

DIVIDEND_HI

rlc

jr

c,SUBT

DIVISOR, DIVIDEND_HI

ср

jr

UGT,NEXT

;CARRY = 0

SUBT: sub

DIVIDENT HI, DIVISOR

;To be shifted into result

scf

NEXT:

djnz COUNT,LOOP

;No flags affected

ret

```

### References

- 1. Steven Frank, *Intelligent Remote Positioner (Motor Control)*, Microchip Technology, Inc. AN531, DS00531C, 1994.

- 2. ZiLOG, ZiLOG Z8 Microcontroller User's Manual, UM95Z800103, 1995.

- 3. ZiLOG, The Z8 Application Note Handbook, DB96Z8X0100, 1996.

- 4. ZiLOG, *A DC Motor Controller Using the ZiLOG Z86E06 MCU*, AP96DZ80500, 1996.

# **Information Integrity**

The information contained within this document has been verified according to the general principles of electrical and mechanical engineering. Any applicable source code illustrated in the document was either written by an authorized ZiLOG employee or licensed consultant. Permission to use these codes in any form, besides the intended application, must be approved through a license agreement between both parties. ZiLOG will not be responsible for any code(s) used beyond the intended application. Contact the local ZiLOG Sales Office to obtain necessary license agreements.

### **Document Disclaimer**

© 1999 by ZiLOG, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZiLOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES. OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. Except with the express written approval ZiLOG, use of information, devices, or technology as critical components of life support systems is not authorized. No licenses are conveyed, implicitly or otherwise, by this document under any intellectual property rights.

ZiLOG, Inc. 910 East Hamilton Avenue, Suite 110 Campbell, CA 95008 Telephone (408) 558-8500 FAX (408) 558-8300 Internet: http://www.zilog.com