# **Application** Note

# Software UART for the Z86E02

AN004102-0502

ZILOG WORLDWIDE HEADQUARTERS • 910 E. HAMILTON AVENUE • CAMPBELL, CA 95008 TELEPHONE: 408.558.8500 • FAX: 408.558.8300 • <u>WWW.ZILOG.com</u>

This publication is subject to replacement by a later edition. To determine whether a later edition exists, or to request copies of publications, contact:

ZiLOG Worldwide Headquarters

910 E. Hamilton Avenue Campbell, CA 95008 Telephone: 408.558.8500 Fax: 408.558.8300 www.ZiLOG.com

Windows is a registered trademark of Microsoft Corporation.

#### **Information Integrity**

The information contained within this document has been verified according to the general principles of electrical and mechanical engineering. Any applicable source code illustrated in the document was either written by an authorized ZiLOG employee or licensed consultant. Permission to use these codes in any form, besides the intended application, must be approved through a license agreement between both parties. ZiLOG will not be responsible for any code(s) used beyond the intended application. Contact the local ZiLOG Sales Office to obtain necessary license agreements.

#### **Document Disclaimer**

© 2000 by ZiLOG, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZiLOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. Except with the express written approval ZiLOG, use of information, devices, or technology as critical components of life support systems is not authorized. No licenses or other rights are conveyed, implicitly or otherwise, by this document under any intellectual property rights.

# Table of Contents

| General Overview                                                                                              |

|---------------------------------------------------------------------------------------------------------------|

| Discussion                                                                                                    |

| Summary                                                                                                       |

| Technical Support       6         Source Code       6         Flow Charts       15         Schematic       17 |

| Test Procedure18Equipment Used18General Test Setup and Execution18Test Results19                              |

| References                                                                                                    |

| Appendix       20         Setup HyperTerminal       20         OTP Programming Procedure       20             |

# Acknowledgments

## **Project Lead Engineer**

Mathias Loehr

## Application and Support Engineer

Mathias Loehr

## System and Code Development

Mathias Loehr

# Software UART for the Z86E02

# **General Overview**

This Application Note describes how to implement a software-emulated universal asynchronous receiver transmitter (UART) function on the Z86 family of low-cost 8-bit microcontrollers. This particular UART function is half-duplex, event-driven, and supports an 8-N-1 protocol using an RS-232 interface.

Optionally, a ninth data bit can be enabled. Baud rates from 1200 to 57600 are supported. The software features full initialization and a basic application for both a receiver and a transmitter. The primary goals for this software UART are speed and reliability.

# Discussion

#### **Theory of Operation**

The UART protocol is based on the EIA RS-232C standard, published in 1969. That standard was popular with the introduction of personal computers and it is one of the most commonly used serial interfaces. Originally defined as a 25-pin interface with several modem handshake and control signals, the basic interface requires only three lines, Receive (RX), Transmit (TX), and GND. In this constellation, a handshake is executed in software by transmitting special XON and XOFF characters, or by using a ninth data bit as a separator between command and data. In most MCU applications, the half-duplex communication is sufficient, meaning that each side is either a receiver or a transmitter at any given time.

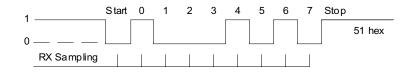

While the transmission speed of the RS-232C cable was formerly limited to 19200 baud for a cable length of 50 feet, advanced specifications and line drivers allow much higher baud rates today. The underlying UART protocol, however, is still the same. Figure 1 illustrates that protocol.

#### Figure 1. Basic 8-bit UART Protocol

2

The TX idle state of the UART is High. A High-to-Low transition of the Start bit initiates the transmission. Eight or nine data bits follow before the Stop bit pulls High again. In the case of 19200 baud, each bit time is approximately 52µs. Asynchronous operation means that the clock is not transmitted. The receiver must operate with the same baud rate, usually derived from a local oscillator. It synchronizes on the falling Start edge and samples the incoming data in their bit middle.

**Note:** The actual signal levels on a PC serial connector are inverted by line drivers on both sides and provide symmetrical levels of around ±12V.

#### **Results of Operation**

The Software UART supports the basic format 8-N-1. That format is 8 data bits, no parity and 1 stop bit. Optionally a 9-bit mode can be enabled to receive or transmit nine data bits. The ninth bit can be used by software as a separator between command or address and data. The achieved baud rates depend on RX or TX mode and the clock frequency, as shown in Table 1.

| RX-4MHz  | 1200 | 2400 | 4800 | 9600 |       |       |       |

|----------|------|------|------|------|-------|-------|-------|

| RX-8MHz  | 1200 | 2400 | 4800 | 9600 | 19200 |       |       |

| RX-12MHZ | 1200 | 2400 | 4800 | 9600 | 19200 | 38400 |       |

| RX-16MHz |      | 2400 | 4800 | 9600 | 19200 | 38400 |       |

| TX-4MHz  | 1200 | 2400 | 4800 | 9600 | 19200 |       |       |

| TX-8MHz  | 1200 | 2400 | 4800 | 9600 | 19200 | 38400 |       |

| TX-12MHz | 1200 | 2400 | 4800 | 9600 | 19200 | 38400 | 57600 |

| TX-16MHz |      | 2400 | 4800 | 9600 | 19200 | 38400 | 57600 |

|          |      |      |      |      |       |       |       |

#### Table 1. Tested Baud Rates for RX and TX Modes vs. Clock Frequencies

Communication is half-duplex. In RX mode, the program waits to receive characters and stores them in a 16-byte RAM buffer. In TX mode, the program continuously sends out an ASCII message string, stored in code memory.

#### Options

Several options at assembly or runtime must be selected to adapt the program to the desired operation. Table 2 contains a list of those options.

3

| Table 2. Options at Assembly and Run Time | Table 2. | Options | at | Assembly | and | Run | Time |

|-------------------------------------------|----------|---------|----|----------|-----|-----|------|

|-------------------------------------------|----------|---------|----|----------|-----|-----|------|

| Name          | Description                                                                                                                                                                                                                         | When          | Where                          |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------------------------|

| XTAL          | Oscillator frequency/1000 in<br>standard mode. Range 4-16<br>MHz, odd values allowed.<br>Default is 8000 (8MHz).                                                                                                                    | Assembly time | CONSTANTS DEF.                 |

| BAUD          | Baud rate: ONE_TWO to<br>FIFTY_SEVEN valid settings<br>depend on mode and<br>frequency shown in Table 1.<br>When XTAL and BAUD are<br>specified, the program<br>selects all the appropriate<br>timings. Default is<br>NINETEEN_TWO. | Assembly time | CONSTANTS_DEF                  |

| RAM_TOP       | Top of RAM for MCU other than Z86E02. Default is 3F.                                                                                                                                                                                | Assembly time | CONSTANTS_DEF                  |

| ROM_TOP       | Top of ROM for MCU other<br>than Z86E02. Default is<br>01FF.                                                                                                                                                                        | Assembly time | CONSTANTS_DEF                  |

| MODE          | RX or TX                                                                                                                                                                                                                            | Run time      | After code label start         |

| NINE_BIT_MODE | ON or OFF                                                                                                                                                                                                                           | Run time      | After code label start         |

| WAIT_STOP     | ON or OFF. Wait for Stop bit,<br>verify it, and set<br>FRAME_ERR accordingly.                                                                                                                                                       | Assembly time | CONDITIONAL<br>ASSEMBLY SWITCH |

Further, there are device options to be selected when the One-Time Programmable (OTP) is programmed or a ROM code is transmitted for mask production. The selection is given in the header of the listing.

#### Initialization

Out of Reset, the program sets P0 to output mode and outputs a High level at P00, which is the TX pin. P2 is set to push-pull output for optional data display. A RAM validation routine checks if three special patterns are still valid. If yes, the following RAM initialization is skipped and all RAM buffers and variables are kept. This routine stores valid information, in the case of spurious undervoltage resets, if  $V_{CC}$  goes below  $V_{BO}$  but not below the RAM retention voltage.

The Stack Pointer is set to the top of RAM, the timers are disabled, and T1 is loaded with BAUD/PBD for the bit time delay. BAUD incorporates the clock frequency and PBD is the T1 prescaler value. These values are computed during assembly time, if BAUD exceeds the value of 255. Finally, the RX interrupt for P31

AN004102-0502

is enabled and the program enters the RX or TX application, depending on the setting of MODE.

#### **Transmit Mode**

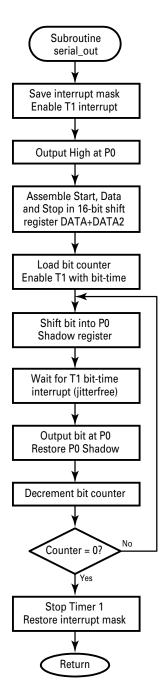

The transmission is realized in the subroutine serial\_out. Before calling the subroutine, the byte to be transmitted must be loaded into DATA. The Technical Support section contains the flowchart for the transmit routine

The routine first saves present interrupts and then enables a Timer 1 interrupt, thereby ensuring that the RX interrupt and other user interrupts are disabled during transmission. The transmit routine assembles the complete bit sequence of Start, Data, and Stop into a 16-bit shift register, made up by DATA and DATA2. This assembly allows the fastest baud rates, because the 9-bit mode decision is kept outside the transmission loop. After bit assembly, the bit counter is set and T1 is started for bit-time delay. The bit is shifted via Carry into a P0 shadow register and the program enters HALT mode to wait for the T1 interrupt. T1 service is just an IRET instruction. After return, the bit is output at P00. This method allows a precise timing without any jitter. After the Stop bit is output, the routine restores the interrupts and returns to main.

The main application in TX mode reads an ASCII message string, stored in code memory at label  $tx\_rom$ . The message string is terminated with Carriage Return and Line Feed for display on a PC monitor. The TX application runs in a loop.

#### **Receive Mode**

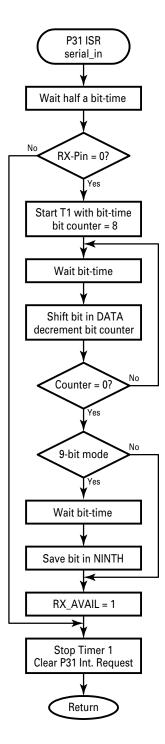

Because the receive event is asynchronous in nature, the Port interrupt pin P31 is used for RX. The appropriate port interrupt service routine (ISR) is diagrammed in the Technical Support section. The ISR first waits for nearly half a bit time. This delay is realized with DJNZ instructions and there is a short-cut for the highest baud rate at a given clock frequency. The RX pin is read to validate the Start bit. If RX is not zero, the program exits after clearing any spurious P31 interrupt requests. If the Start bit is valid, T1 is started with bit-time delay and the bit counter is set to 8. The program polls the T1 IRQ bit for speed reasons. After timeout, RX pin is sampled and shifted into DATA until the complete byte is received. If 9-bit mode is enabled the program waits for another T1 timeout, reads the RX pin and sets NINTH accordingly. The receive character available flag RX\_AVAIL is set to 1, T1 is stopped, and the program returns to main after clearing spurious P31 interrupt requests. User interrupts are inherently disabled during P31 receive service.

The software must continuously check the RX\_AVAIL flag to save a received byte or react on it, before it is overwritten by the next reception. To allow at least a full bit time for check loop plus reaction, the receive routine does not wait for the Stop bit and returns early in the second half of the most recent data bit. This fact must be considered for handshakes and data flow control. For lower baud rates, the

5

early return might not be required, and the user may want to wait for the Stop bit, verify it, and set the flag FRAME\_ERR accordingly. This option is provided by the conditional assembly switch WAIT\_STOP, as described in Table 2.

The RX application stores received bytes in a 16-byte RAM buffer at RX\_BUF. When the buffer is full, it is overwritten from the beginning. Additionally, each received byte is output at P2.

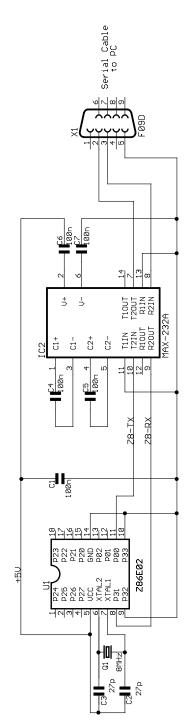

#### Hardware

The software UART can be built using the schematics in the Technical Support section. The schematic shows a single +5V supply setup, where the Z8 is connected by a MAX-232A line driver to a SUBD-9 serial connector. Only RX and TX lines are used. The circuit can be connected to a PC, running a terminal program with setting *no handshake*.

Figure 4, in the Technical Support section, shows a setup without line drivers, which can be used for in-system communication or for transmission via short cables. Both Z8 MCUs must be programmed with the same baud rate, one as transmitter and one as receiver and the RX and TX lines are crossed. Beginning with a cable length of 10cm, wave reflections occur and can result in significant overshoots and undershoots. Because P31 RX input is also used for OTP programming, allowing 12V input levels, P31 RX input does not feature an input protection diode to  $V_{CC}$ . This diode is external, in addition to an RC input filter of 1  $\mu$ s to attenuate possible overshoots.

The oscillator buildup capacitors in both schematics are connected to V<sub>CC</sub> instead of GND. For the targeted frequency range of 4-16MHz, the RF sees no difference between V<sub>CC</sub> and GND. The V<sub>CC</sub> connection allows a short and direct PCB path, resulting in an improved EFT behavior.

#### Summary

#### **Reaffirmation of Results**

The Software UART supports the most common UART protocol 8-N-1 and, optionally, a nine-bit mode. The concentration on the basic format results in efficient code and high baud rates. Special efforts were put into the reliability of the application, such as jitter-free transmission, glitch filter in the receive path, RAM data protection against spurious VBO and ESD, and a PC wraparound protection with SW-Reset. On the hardware side, the connection of the oscillator buildup capacitors to V<sub>CC</sub> help achieve optimal system performance.

# **Technical Support**

# Source Code

| ; *****                         | * * * * * * * * * * * * * * * * * * *                                               | ***************************************                                                                                                                                                                                                                                                                  |

|---------------------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *<br>*<br>*                     | Module Name:<br>Copyright:<br>Date:                                                 | SW-UARTX.ASM V1.2<br>ZILOG (c)1999<br>OCT 7, 1999                                                                                                                                                                                                                                                        |

| *<br>*<br>*<br>*<br>*           | Created by:<br>Modified by:<br>Compiler:<br>Code size:<br>Checksum:<br>Description: | Mathias Loehr - ZILOG Germany<br>ZDS V3.00B1<br>294 bytes<br>59B3 (Project-Settings-Debugger-Pad Memory FF)                                                                                                                                                                                              |

| *<br>*<br>*                     |                                                                                     | erial RS-232 Interface for Z86E02 and higher<br>eration: Receive (RX) or Transmit (TX)                                                                                                                                                                                                                   |

| * * * * * * *                   | Selectable Baud<br>RX-4MHz:<br>RX-8MHz:<br>RX-12MHz:<br>RX-16MHz:                   | <pre>drates:     1200,2400,4800,9600     1200,2400,4800,9600,19200     1200,2400,4800,9600,19200,38400*     2400,4800,9600,19200,38400     *crystal &lt;0.5%</pre>                                                                                                                                       |

| *<br>*<br>*<br>*                | TX-4MHz:<br>TX-8MHz:<br>TX-12MHz:<br>TX-16MHz:                                      | 1200,2400,4800,9600,19200<br>1200,2400,4800,9600,19200,38400<br>1200,2400,4800,9600,19200,38400,57600<br>2400,4800,9600,19200,38400,57600                                                                                                                                                                |

| *<br>*<br>*<br>*                | Format:<br>Operation:                                                               | 1 START bit, 8 DATA bits, optional 9. DATA bit,<br>NO PARITY and 1 STOP bit.<br>T1 in continuous mode is used for bit-time delay<br>Register DATA is used for RX or TX buffer                                                                                                                            |

| *<br>*                          | Target Device:<br>Oscillator:                                                       | Z86E02 and Z86E04/08/30/31/33/34/40/44/733/743<br>4-16MHz crystal or resonator, tolerance max. +-1%                                                                                                                                                                                                      |

| *<br>*<br>*<br>*<br>*<br>*<br>* | Device Options                                                                      | : AUTOLATCHES OFF YES<br>LOW EMI NO<br>32KHZ-OSC NO<br>RC-OSC NO<br>PERMANENT WDT NO<br>TESTMODE DISABLE NO                                                                                                                                                                                              |

| *                               | Defaults:                                                                           | 8MHz XTAL, 19200 Baud TX, 8 DATA, NO PARITY, 1 STOP                                                                                                                                                                                                                                                      |

| *<br>*<br>*                     | Application:                                                                        | RX-Mode - 16 byte receive buffer<br>TX-Mode - Send ROM-message                                                                                                                                                                                                                                           |

| * * * * *                       | Mode Options:                                                                       | <ul> <li>RX/TX operation mode is set by MODE in "start"</li> <li>9-bit mode is enabled by NINE_BIT_MODE in "start"</li> <li>Oscillator Frequency is set by XTAL in CONSTANTS DEF</li> <li>Baudrate is set by BAUD in CONSTANTS DEF</li> <li>Top of MCU RAM is set by RAM_TOP in CONSTANTS DEF</li> </ul> |

| *<br>*<br>*                                                                   |                                         | - Wait for STOF<br>in CONDITIONA<br>: The built-in F<br>RAM data in ca<br>Undervoltage (                 | OM is set by ROM_TOP in CONSTANTS DEF<br>P bit function is set by WAIT_STOP<br>AL ASSEMBLY SWITCHES<br>RAM pattern validation keeps valid<br>se of (spurious) Undervoltage Resets.<br>VBO) Reset can be also caused by ESD. |

|-------------------------------------------------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                               | ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ |                                                                                                          |                                                                                                                                                                                                                             |

| ; 1. HARDWAR                                                                  | E DESCRIP:                              | FION                                                                                                     |                                                                                                                                                                                                                             |

| •                                                                             | ve (RX):<br>mit(TX):                    | P31<br>P00                                                                                               |                                                                                                                                                                                                                             |

| ; Note:<br>10k,100pF)                                                         | Add clar                                | mping diode betw                                                                                         | een P31 and VCC and RC input filter                                                                                                                                                                                         |

|                                                                               | 1, if oper                              | rated without li                                                                                         | ne driver.                                                                                                                                                                                                                  |

| ; 2. CONDITI                                                                  | ONAL ASSEN                              | ABLY SWITCHES:                                                                                           |                                                                                                                                                                                                                             |

|                                                                               | GLOBALS                                 | on                                                                                                       | ;symbols globally available to linker                                                                                                                                                                                       |

| ON<br>OFF<br>WAIT_STOP                                                        | EQU<br>EQU<br>EQU                       | 1<br>O<br>OFF                                                                                            | ;<br>;<br>;ON/OFF. Wait for Stop bit, verify it<br>;and set FRAME_ERR accordingly                                                                                                                                           |

| ; 3. SEGMENT                                                                  | DEFINITIO                               | ONS                                                                                                      |                                                                                                                                                                                                                             |

|                                                                               | DEFINE<br>DEFINE<br>DEFINE              | ram_e02, space=<br>main_e02<br>rollover_e02, c                                                           | rfile, org=04 ;RAM range 04-3F<br>;relocatable ROM 000C-01FA<br>prg=01FB ;non-relocatable ROM 01F<br>;01FF                                                                                                                  |

| ; 4. CONSTAN                                                                  | TS DEFINIT                              | TIONS                                                                                                    |                                                                                                                                                                                                                             |

| XTAL                                                                          | EQU                                     | 8000                                                                                                     | ;SELECT CRYSTAL FREQUENCY HERE!<br>;Range: 4000-16000=4-16MHz (OSC/2 mode)<br>;4MHz Low EMI in OSC/1 mode = 8000                                                                                                            |

| FIFTY_SEVEN                                                                   | EQU                                     | 175*XTAL/8/1000                                                                                          |                                                                                                                                                                                                                             |

| THIRTY_EIGHT<br>NINETEEN_TWO<br>NINE_SIX<br>FOUR_EIGHT<br>TWO_FOUR<br>ONE_TWO | EQU<br>EQU<br>EQU<br>EQU<br>EQU         | 26*XTAL/8/1000<br>52*XTAL/8/1000<br>104*XTAL/8/1000<br>208*XTAL/8/1000<br>416*XTAL/8/1000<br>EQU 833*XTA | );T=208,3us (4800 Baud)                                                                                                                                                                                                     |

| BAUD                                                                          | EQU                                     | NINETEEN_TWO                                                                                             | ;SELECT BAUDRATE HERE!                                                                                                                                                                                                      |

| IF<br>PBD<br>ELSEI                                                            | BAUD > 2<br>EQU<br>F BAUD > 9           | 8                                                                                                        | ;<br>;T1 Prescaler setting for bittime delay                                                                                                                                                                                |

| PBD                                                                |               | EQU                                                                     | 4                                                         |                          |                                                                                                                                                                                                                    |

|--------------------------------------------------------------------|---------------|-------------------------------------------------------------------------|-----------------------------------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                    | ELSEIF        | BAUD > 2                                                                | 255                                                       |                          | ;                                                                                                                                                                                                                  |

| PBD                                                                | ELSE          | EQU                                                                     | 2                                                         |                          | ;                                                                                                                                                                                                                  |

| PBD                                                                | ENDIF         | EQU                                                                     | 1                                                         |                          | ;                                                                                                                                                                                                                  |

| BITO<br>BIT1<br>BIT2<br>BIT3<br>BIT4<br>BIT5<br>BIT6<br>BIT7       |               | EQU<br>EQU<br>EQU<br>EQU<br>EQU<br>EQU<br>EQU                           | %01<br>%02<br>%04<br>%10<br>%20<br>%40<br>%80             |                          | ;Bit 0 mask<br>;Bit 1 mask<br>;Bit 2 mask<br>;Bit 3 mask<br>;Bit 4 mask<br>;Bit 5 mask<br>;Bit 6 mask<br>;Bit 7 mask                                                                                               |

| RAM_TOP<br>RAM_BOT<br>ROM_TOP                                      | -             |                                                                         | EQU<br>EQU<br>EQU                                         | %3F<br>%04<br>%01FF      | ;SELECT TOP OF RAM HERE!<br>;bottom of RAM<br>;SELECT TOP OF ROM HERE!                                                                                                                                             |

| DATA_LE<br>RX<br>TX                                                | ENGTH         | EQU<br>EQU<br>EQU                                                       | 8<br>0<br>1                                               |                          | ;basic data bits (fixed)<br>;RX mode<br>;TX mode                                                                                                                                                                   |

| PATTERN<br>PATTERN<br>PATTERN                                      | 12            | EQU<br>EQU<br>EQU                                                       | %5A<br>%A5<br>%F0                                         |                          | ;RAM validation pattern<br>;RAM validation pattern<br>;RAM validation pattern                                                                                                                                      |

|                                                                    |               | CATABLE I<br>ARIABLES)                                                  |                                                           | , RAM &                  | STATUS REGISTER DEFINITIONS                                                                                                                                                                                        |

| ; user-<br>PORT_GR<br>P0<br>P2<br>BIT_CN<br>DATA<br>DATA2<br>NINTH | ξ₽            | d port &<br>EQU<br>EQU<br>EQU<br>EQU<br>EQU<br>EQU<br>EQU<br>EQU<br>EQU | bank 0 r<br>%00<br>R0<br>R2<br>R3<br>R4<br>R5<br>R6<br>R7 | egister                  | <pre>s (4-bit addressing mode) ;port register group ;Port 0 R/W ;Port 2 R/W ;Port 3 R+W ;serial bit counter ;receive/transmit data ;transmit data 2 ;9. data bit, usable by SW as </pre>                           |

| NINE_B<br>RXH<br>TX_PTR<br>TX_CNT<br>TX_PTR<br>TX_PTR<br>TX_PTR    | Г<br>२<br>२_Н | EQU<br>EQU<br>EQU                                                       | EQU<br>R9<br>EQU<br>EQU<br>R12<br>R13                     | R8<br>R10<br>R11<br>RR12 | ;data/command switch<br>;Nine Bit Mode ON/OFF<br>;used in "ser_in" RX-ISR<br>;receive buffer pointer<br>;transmit byte counter<br>;pointer to transmit table in ROM<br>;MSB at even address<br>;LSB at odd address |

| ; user-<br>CTRL_GR<br>_SIO<br>_TMR<br>T1                           |               | d control<br>EQU<br>EQU<br>EQU<br>EQU<br>EQU                            | l registe<br>%F0<br>R0<br>R1<br>R2                        | rs (4-b)                 | it addressing mode)<br>;control register group<br>;sio register (only on classic Z8)<br>;timer mode register<br>;timer/counter 1                                                                                   |

;port 2 mode register ;port 3 mode register ;port 0/1 mode register

;register pointer ;stack pointer High byte ;stack pointer Low byte

;flag register

; interrupt priority register ; interrupt request register ; interrupt mask register

| P2M      | EOU | R6  |

|----------|-----|-----|

| -P3M     | EOU | R7  |

| PO1M     | EQU | R8  |

| _<br>IPR | EQU | R9  |

| IRQ      | EQU | R10 |

| IMR      | EQU | R11 |

| FLAGS    | EQU | R12 |

|          | EQU | R13 |

| SPH      | EQU | R14 |

| SPL      | EQU | R15 |

; 6. RELOCATABLE RAM DEFINITIONS ; (GLOBAL VARIABLES)

|                                                   | SEGMENT                      | ram_e02               |   | ;general purpose RAM 04-3F                                                                                                                                                                           |

|---------------------------------------------------|------------------------------|-----------------------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIT_CNT<br>DATA<br>DATA2<br>NINTH                 | DS<br>DS<br>DS               | DS<br>1<br>1<br>1     | 1 | ;04 - serial bit counter<br>;05 - receive/transmit data<br>;06 - transmit data 2<br>;07 - 9. data bit, usable by SW as<br>; data/command switch                                                      |

| NINE_BIT_MODE<br>RXH<br>serial out                | DS<br>DS                     | 1<br>1                |   | ;08 - 1=ON, 0=OFF<br>;09 - various use in serial_in and                                                                                                                                              |

| RX_PTR<br>TX_CNT                                  | DS<br>DS<br>BLKW<br>DS<br>DS | 1<br>1<br>1<br>1      |   | ;0A - receive buffer pointer<br>;0B - transmit byte counter<br>;0C - pointer to transmit table in ROM<br>;0E - unused<br>;0F - unused                                                                |

| FRAME_ERR<br>BAUD_SH<br>P0_SH<br>MODE<br>RX_AVAIL | DS<br>DS<br>DS<br>DS         | 1<br>DS<br>1<br>1     | 1 | <pre>;10 - Frame Error Flag, 0=ok, 1=bad<br/>;11 - Baudrate Shadow<br/>;12 - Port 0 Shadow<br/>;13 - RX/TX Operation Mode<br/>;14 - 1 = receive character available<br/>; 0 = no data received</pre> |

| SIGNATURE1<br>SIGNATURE2<br>SIGNATURE3            | DS<br>DS<br>DS<br>DS<br>BLKB | 1<br>1<br>1<br>1<br>7 |   | ;15 - RAM signature<br>;16 - RAM signature<br>;17 - RAM signature<br>;18 - unused<br>;19-1F unused                                                                                                   |

| RX_BUF<br>RX_BUF_END<br>USER_STACK                | BLKB<br>BLKB                 | 16<br>16              |   | ;20-2F Receive Buffer<br>;30<br>;30-3F reserved for stack                                                                                                                                            |

; Max. Stack Depth: 2 Call + 1 INT = 7 bytes ; Top of Stack: RAM\_TOP

; 7. Z8 RESET & INTERRUPT VECTORS

| VECTOR | IRQ0 = dummy isr           | ;P32 int, falling edge   |

|--------|----------------------------|--------------------------|

| VECTOR | IRQ1 = dummy_isr           | ;P33 int, falling edge   |

|        | IRQ2 = serial_in           | ;P31 int, falling edge   |

|        | $IRQ3 = dummy_{isr}$       | ;P32 int, rising edge    |

| VECTOR | IRQ4 = dummy_isr           | ;T0 (not present on E02) |

| VECTOR | $IRQ5 = timer\overline{1}$ | ;T1 int                  |

| ;                                      | VECTOR                                              | RESET = main                                                                                                                                       | ;Reset vector                                                                                                                                                                                     |  |  |  |  |  |

|----------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| ************************************** |                                                     |                                                                                                                                                    |                                                                                                                                                                                                   |  |  |  |  |  |

| main:                                  | SEGMENT                                             | main_e02                                                                                                                                           | ;                                                                                                                                                                                                 |  |  |  |  |  |

|                                        | di<br>srp<br>ld<br>ld<br>ld<br>ld<br>ld<br>cp<br>jr | <pre>#CTRL_GRP<br/>_P3M,#BIT0<br/>P2M,#00000000b<br/>P0_SH,#BIT0<br/>P0,P0_SH<br/>_P01M,#BIT2<br/>SIGNATURE1,#PATTERN1<br/>nz,ram_is_invalid</pre> | ;<br>;select Control register bank<br>;P3 digital inputs<br>;P2 Push-Pull<br>;P2 all outputs<br>;TX=1 (P00 mark state)<br>;output on Port 0<br>;internal stack, P0 output<br>;check RAM pattern 1 |  |  |  |  |  |

| vom ig invol                           | cp<br>jr<br>cp<br>jr                                | SIGNATURE2, #PATTERN2<br>nz,ram_is_invalid<br>SIGNATURE3, #PATTERN3<br>z,ram_is_ok                                                                 | ;check RAM pattern 2<br>;check RAM pattern 3<br>;if RAM is intact skip RAM init                                                                                                                   |  |  |  |  |  |

| <pre>ram_is_inval init ram:</pre>      | ld                                                  | _SPL,#RAM_BOT                                                                                                                                      | ;RAM bottom                                                                                                                                                                                       |  |  |  |  |  |

|                                        | inc<br>cp                                           | @_SPL<br>_SPL<br>_SPL,#RAM_TOP+1<br>nz,init_ram                                                                                                    | ;clear RAM byte<br>;point to next byte<br>;top of RAM exceeded?<br>;leaves SPL at RAM_TOP+1                                                                                                       |  |  |  |  |  |

| ram is ok:                             | ld<br>ld<br>ld                                      | SIGNATURE1, #PATTERN1<br>SIGNATURE2, #PATTERN2<br>SIGNATURE3, #PATTERN3                                                                            | ;write special test patterns<br>;into contiguous RAM locations<br>;                                                                                                                               |  |  |  |  |  |

|                                        | ld<br>clr<br>ld<br>ld<br>ld                         | _SPL,#RAM_TOP+1<br>TMR<br>_PRE1,#PBD<<2+BIT0+BIT1<br>_T1,#BAUD/PBD<br>BAUD_SH,#BAUD/PBD                                                            | ;init stack pointer<br>;disable timers<br>;Modulo-N T1 mode (autoreload)<br>;PSC=PBD. TCLK=SCLK/4<br>;T1 bit-time delay<br>;Baudrate Shadow                                                       |  |  |  |  |  |

|                                        | ld                                                  | _IPR,#%2A                                                                                                                                          | ;int. priority: 3>5>2>0>4>1<br>;reserve IRQ3 for highest int                                                                                                                                      |  |  |  |  |  |

|                                        | ld<br>clr<br>ei                                     | _IMR,#00000100b<br>IRQ                                                                                                                             | ;enable IRQ2 (RX-INT)<br>;clear spurious IRQ´s<br>;enable interrupts globally                                                                                                                     |  |  |  |  |  |

| start:                                 | srp<br>ld<br>ld                                     | #PORT_GRP<br>MODE,#TX<br>_NINE_BIT_MODE,#OFF                                                                                                       | ;Port Register Group<br>;SELECT RX/TX MODE HERE!<br>;SELECT NINE BIT MODE HERE!<br>;ON or OFF                                                                                                     |  |  |  |  |  |

|                                        | cp<br>jr                                            | MODE,#RX<br>z,rx_mode ;                                                                                                                            | ;RX mode?                                                                                                                                                                                         |  |  |  |  |  |

; Transmits a whole message, stored by tewise in ROM at  $\ensuremath{\mathsf{tx\_rom}}$

tx mode: ld \_TX\_CNT, #(tx\_end-tx\_rom) ;rom table length \_TX\_CNT,#(tx\_end-tx\_rom) ;rom table length \_TX\_PTR\_H,#>tx\_rom ;load MSB of register pair \_TX\_PTR\_L,#<tx\_rom ;load LSB of register pair \_DATA,@\_TX\_PTR ;get constant from ROM table \_NINTH,#0 ;optional 9. data bit serial out ;transmit one character ld ld tx\_lp: ldc ld ;transmit one character call ;point to next character ;transmit whole message incw djnz jr start ;

; Inits RX mode, receives 16 bytes and stores in RAM buffer at RX\_BUF. ; Buffer is overwritten when full.

; Received character is also displayed at P2.

rx mode:

| rx_mode:<br>wait rx: | ld                                            | _RX_PTR,#RX_BUF                                                                                                               | ;                                                                                                                                                   |

|----------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| walt_1X.             | cp<br>jr<br>ld<br>ld<br>inc<br>cp<br>jr<br>jr | RX_AVAIL,#1<br>nz,wait_rx<br>RX_AVAIL<br>_P2,_DATA<br>@ RX_PTR,_DATA<br>_RX_PTR<br>_RX_PTR,#RX_BUF_END<br>nz,wait_rx<br>start | <pre>;character received? ; ;reset flag immediately ;save/process data ; within one bit-time ; ;end of buffer exceeded? ;wait for next char ;</pre> |

; SUBROUTINES

|                                         | ************************************** |                  |                                                                                                                   |                                                             |  |  |  |

|-----------------------------------------|----------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--|--|--|

| *<br>*                                  | Returns:                               | none. DA         | ATA and NINTH are destroy                                                                                         | ved.                                                        |  |  |  |

| * * * *                                 | Entry Value:                           | s:               | DATA - byte to be transm<br>NINTH - bit 0 holds the<br>P0_SH - shadow register                                    | optional 9. data bit                                        |  |  |  |

| * *                                     | Description                            |                  | shift register for serial<br>asmitted first.<br>ode to generate the bit-time<br>are disabled during transmission. |                                                             |  |  |  |

| *<br>*<br>*                             | Notes:                                 |                  | jitter-free bit synchronisation to falling START edge by<br>entering HALT and waiting for T1 vector interrupt.    |                                                             |  |  |  |

| *************************************** |                                        |                  |                                                                                                                   |                                                             |  |  |  |

| serial_out:                             |                                        | di<br>push<br>ld | IMR<br>IMR,#BIT5                                                                                                  | ;<br>;save user interrupt mask<br>;enable T1 interrupt only |  |  |  |

|                                | or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | P0 SH,#BIT0                                                         | ;TX=1 (Idle mode = mark level)                                                                          |  |  |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--|--|

|                                | ld                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _P0,P0_SH                                                           | ;output on P00                                                                                          |  |  |

| serial out1:                   | ld<br>cp<br>jr<br>sra<br>rlc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | _DATA2,#1<br>_NINE_BIT_MODE,#ON<br>nz,serial_out1<br>NINTH<br>DATA2 | ;shift in STOP bit<br>;9-bit mode on?<br>;branch, if not<br>;9. bit into Carry<br>;shift in 9. data bit |  |  |

| borrar_outer.                  | rcf<br>rlc<br>rlc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | DATA<br>DATA2                                                       | ;START into Carry<br>;START into LSB, D7 into Carry<br>;now all bits are in                             |  |  |

|                                | ld<br>add<br>ei                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _BIT_CNT, #DATA_LENGTH+2<br>_BIT_CNT, _NINE_BIT_MODE                | ;sync on first T1 interrupt<br>;<br>;                                                                   |  |  |

| send lp:                       | ld                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | TMR,#BIT2+BIT3                                                      | ;load and enable T1                                                                                     |  |  |

|                                | rrc<br>rrc<br>rlc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | DATA2<br>DATA<br>P0_SH                                              | ;LSB into Carry<br>;Carry into MSB, LSB into Carry<br>;get Carry into LSB                               |  |  |

| tx_sync:                       | nop<br>halt<br>ld<br>rrc<br>djnz                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _P0,P0_SH<br>P0_SH<br>_BIT_CNT,send_lp                              | ;<br>;wait on T1 interrupt<br>;output at P00<br>;restore P0_SH<br>;loop delay = 54+40=94 SCLK           |  |  |

|                                | clr<br>di<br>pop<br>ei<br>ret                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | TMR<br>IMR                                                          | ;disable T1<br>;disable interrupts<br>;restore user interrupt mask<br>;<br>;                            |  |  |

|                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                     | *****                                                                                                   |  |  |

| * Receive data<br>*            | a (Interi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | rupt Service)                                                       |                                                                                                         |  |  |

| * Returns:<br>*<br>*<br>*<br>* | -<br>FRAME_EI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                     |                                                                                                         |  |  |

| * Entry Value:                 | s:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | none                                                                |                                                                                                         |  |  |

|                                | Description: Falling START edge causes P31-IRQ2 service.<br>After nearly a half bit-time RX is sampled again to validate<br>the START bit. Immediate exit in case of glitch or noise.<br>Otherwise IRQ5 is enabled and T1 is setup in continous mode<br>for bit-time delay. T1 is polled for timeout and received<br>bits are shifted into DATA.<br>Routine does not wait for the STOP bit and exits in the<br>second half of the last data bit.<br>RX_AVAIL is set, T1 is disabled and IRQ-bit2 is cleared. |                                                                     |                                                                                                         |  |  |

| * Response:                    | P31-IRQ2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2: 26 + 0.5x longest inst:                                          | ruction = 36 +-10 SCLK                                                                                  |  |  |

| <pre>* T1-IRQ5: 2+22/2 = 13 +-11 SCLK * Jitter: Total sampling jitter: +-21 SCLK *</pre> |                                       |                                                                         |                                                                                                                    |  |  |  |  |  |

|------------------------------------------------------------------------------------------|---------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| ***************************************                                                  |                                       |                                                                         |                                                                                                                    |  |  |  |  |  |

| serial_in:                                                                               | cp<br>jr<br>ld                        | BAUD_SH,#66<br>ult,validate_start<br>_RXH,#(BAUD/6)-(120/12)            | ;check BAUD<br>;short cut for fast baudrates<br>;Half-bit delay count in DJNZ                                      |  |  |  |  |  |

| half_bit:                                                                                | djnz                                  | _RXH,half_bit                                                           | ;12 SCLK - execute delay                                                                                           |  |  |  |  |  |

| validate_star                                                                            | tm<br>jr<br>ld                        | P3,#BIT1<br>nz,rx_exit<br>TMR,#BIT2+BIT3                                | ;RX=0?<br>;if zero, START bit is valid!<br>;load and enable T1 (bit time)                                          |  |  |  |  |  |

| rogojuo lp.                                                                              | or<br>clr<br>ld                       | IMR,#BIT5<br>NINTH<br>_BIT_CNT,#DATA_LENGTH                             | ;enable T1 Interrupt (polling)<br>;clear bit 9<br>;number of basic data bits                                       |  |  |  |  |  |

| receive_lp:                                                                              | tcm<br>jr                             | IRQ,#BIT5<br>nz,receive_lp                                              | ;bit-time elapsed - IRQ5=1?<br>;                                                                                   |  |  |  |  |  |

| sample_data:                                                                             | ld<br>rr<br>rr<br>rrc<br>and<br>djnz  | _RXH,_P3<br>RXH<br>RXH<br>DATA<br>IRQ,#~BIT5<br>_BIT_CNT,receive_lp     | ;sample P31<br>;shift right<br>;P31 into Carry<br>;Carry into MSB<br>;reset IRQ5<br>;loop delay: 86+13=99+-11 SCLK |  |  |  |  |  |

| wait bit9:                                                                               | cp<br>jr                              | _NINE_BIT_MODE,#ON<br>nz,rx_ok                                          | ;9-bit mode on?                                                                                                    |  |  |  |  |  |

| _                                                                                        | tcm<br>jr<br>tm<br>jr<br>ld           | IRQ,#BIT5<br>nz,wait_bit9<br>P3,#BIT1<br>z,rx_ok<br>_NINTH,#1           | ;bit-time elapsed - IRQ5=1?<br>;<br>;RX=0?<br>;<br>;set data bit 9                                                 |  |  |  |  |  |

| rx_ok:                                                                                   | ld                                    | -<br>RX_AVAIL,#1                                                        | ;set data available flag                                                                                           |  |  |  |  |  |

| wait_STOP_bit                                                                            |                                       | WAIT_STOP=ON                                                            |                                                                                                                    |  |  |  |  |  |

|                                                                                          | tcm<br>jr<br>tcm<br>jr<br>ld<br>ENDIF | IRQ,#BIT5<br>nz,wait_STOP_bit<br>P3,#BIT1<br>z,frame_ok<br>FRAME_ERR,#1 | ;bit-time elapsed - IRQ5=1?<br>;<br>;STOP=1?<br>;indicate frame error                                              |  |  |  |  |  |

| frame_ok:                                                                                | clr<br>and                            | TMR<br>IMR,#~BIT5                                                       | ;disable T1<br>;disable T1 interrupt                                                                               |  |  |  |  |  |

| rx_exit:                                                                                 | and<br>iret                           | IRQ,#~(BIT2+BIT5)                                                       | ;clear P31 and T1 requests<br>;ok exit                                                                             |  |  |  |  |  |

14

\* Timer 1 Interrupt Service Routine \* \* Execution: 26 (latency) + 14 (IRET) = 40 SCLK \* \* Notes: If this ISR shall be used by other tasks, the T1 interrupt in serial\_out may be changed from vector to polling mode. timer1: iret ; Interrupt Service for unused interrupt vectors dummy\_isr: iret \* Table #1 - TX message string tx rom: .ASCII "SW-UARTX V1.2 (c)1999 ZILOG" DB %OD ;Carriage Return DB 80A ;Newline tx end: ; RELOCATABLE PC ROLLOVER PROTECTION ; recommended SW-Reset to protect from wrap-around opcode fetches into ; interrupt vector table. SEGMENT rollover e02 ;trap routine at the end of ROM ORG ROM TOP- $\overline{4}$ nop ;synchronize nop ;synchronize ;SW-Reset jp main

## **Flow Charts**

Figure 2. Transmit Flow Chart

#### Figure 3. Receive Flow Chart

Schematic

Figure 4. RS-232 SetupFigure 4

# **Test Procedure**

## **Equipment Used**

The following test equipment was used for testing:

- Prototype board according to schematic

- Personal computer with Windows 95

- Z86CCP01ZEM, called CCP emulator

- Digital oscilloscope (required during debug phase)

- Clock generator (required during debug phase)

#### **General Test Setup and Execution**

#### Test with OTP

The board is equipped with an OTP Z86E02, programmed with the CCP emulator and the program defaults 8MHz XTAL, 19200 TX, 9-bit mode Off and WAIT STOP Off. The OTP programming procedure is given in the <u>Appendix</u>.

The board is connected by a 9-pin serial cable to a standard PC running Windows 95. The Windows HyperTerminal is called and setup for *direct* connection via COM1, 19200 baud, 8-N-1 and No Protocol. When the board is supplied with +5V, the line message SW-UARTX V1.2 <sup>©</sup> 1999 ZILOG is displayed across the screen. A complete setup for HyperTerminal is detailed in the <u>Appendix</u>. Other terminal programs may be used as well, if they provide corresponding settings.

#### Test with an Emulator

The CCP emulator is used for the test of all baud rates at clock frequencies of 4MHz, 8MHz and 12MHz (16-MHz operation requires a Z86C50 emulator; selected CCP emulators may also work at 16MHz. The board is connected to the emulator by an ICE cable, and the V<sub>CC</sub> jumper on the emulator is set to supply the board. The software calls the ZiLOG Developer Studio (ZDS), and a project is created for the target MCU. The settings for assembler and linker remain at their default values. A test for different baud rates and clock frequencies can be performed by changing values for the BAUD and XTAL variables. However, please note that the crystal on the emulator must be exchanged accordingly. Because HyperTerminal does not synchronize or error-check the transmission in this setting, a program halt and subsequent recontinuance of program execution may lead to an improper display.

RECEIVE mode is tested in the same setup. MODE, BAUD and XTAL are set before compiling. The ASCII representation for each pressed key becomes visible

in the Z8 RAM buffer, starting at 20h. To test a continuous data stream, a text file with 16 characters can be setup and transmitted from HyperTerminal.

## **Test Results**

All settings according to baud rates and clock frequencies in Table 1 test successfully. A clock tolerance of  $\pm 1\%$  is sufficient for all settings, except 38400 RX @ 12MHz, which requires a tolerance of  $\pm 0.5\%$ .

The basic timing for transmission and reception includes the following variance per bit:

- 1. Clock frequency tolerance, as provided by a crystal or resonator: <1%

- 2. T1 integer value to bit timing deviation: 0.16%

- 3. BAUD integer rounding for odd crystal frequency: <0.8%

These variances are added and multiplied by the number of transmitted bits (for example, 10). The resulting word variance must be <50%, because this variance is the maximum shift from the middle of the bit cell to its margin. In practice, the word variance should be reasonably lower than 50% for the following reasons:

- The transmitter also exhibits a clock variance

- Receiver bit sampling is not exactly in bit middle

- There is jitter in the transmitter and receiver timing

The SW\_UARTX receiver samples in the bit middle (50% of the bit cell) for all baud rates, except for the highest setting at each frequency. 38200 baud at 16MHz and all corresponding baud rates sample at round 60%. 38200 baud at 12MHz samples at approximately 70% of the bit cell. Additionally, there is jitter from P31 interrupt and T1 IRQ polling, resulting in a worst-case measurement of ±21 SCLK. These values were recorded during the debug phase with a frequency generator and a digital scope.

# References

Gilbert Held, Data Communications Networking Devices, John Wiley & Sons, 1993.

Z86C36 Product Specification, ZiLOG, Inc., 1999.

# Appendix

## Setup HyperTerminal

Connect: Direct to COM1 or any available COM port Configure:

| • | Bits per second:  | 19200 |

|---|-------------------|-------|

|   | Bito por occorra. | 10200 |

- Data Bits: 8

- Parity: None

- Stop Bits

- Flow Control: None

#### Settings:

- Function, arrow and control keys act as: Windows Keys

- Emulation: Auto detect

- Back-scroll buffer lines: 0

#### ASCII Setup: ASCII Receiving:

- Force incoming data to 7-bit ASCI

- Wrap lines that exceed terminal width

# **OTP Programming Procedure**

- Install ZDS version 3, and copy SW\_UARTX.ASM and SW\_UARTX.ZWS into the working directory

- IF file zws is not available, create FILE ➤ NEW PROJECT for the Z86E02 and Z86CCP01ZEM emulator

- ELSE navigate to FILE ➤ OPEN PROJECT and answer YES to move the project into the directory path

- BUILD the downloadable file for the debugger

- Navigate to PROJECT ➤ SETTINGS ➤ DEBUGGER ➤ PAD MEMORY, and check value FF for the correct checksum

- Connect the CCP emulator, power up, and click the RESET debug icon

- Click the OTP icon

- Select DEVICE Z86E02 and the corresponding TOPMARK, (for example, SL1925)

- Select the following PROGRAMMING OPTIONS:

- AUTOLATCHES DISABLE: YES

- LOW EMI: NO

- RC-OS: NO

- PERMANENT WDT: NO

- EPROM/TESTMODE DISABLE: NO

- Select SERIALIZATION none

- Insert an empty OTP into the emulator programming socket and perform BLANK CHECK

- PROGRAM the device and note the checksum