### **Application Note**

# Analog-to-Digital Conversion Techniques Using ZiLOG Z8 MCUs

AN004001-Z8X0400

This publication is subject to replacement by a later edition. To determine whether a later edition exists, or to request copies of publications, contact:

### **ZiLOG Worldwide Headquarters**

910 E. Hamilton Avenue Campbell, CA 95008 Telephone: 408.558.8500

Fax: 408.558.8300 www.ZiLOG.com

Windows is a registered trademark of Microsoft Corporation.

### **Information Integrity**

The information contained within this document has been verified according to the general principles of electrical and mechanical engineering. Any applicable source code illustrated in the document was either written by an authorized ZiLOG employee or licensed consultant. Permission to use these codes in any form, besides the intended application, must be approved through a license agreement between both parties. ZiLOG will not be responsible for any code(s) used beyond the intended application. Contact the local ZiLOG Sales Office to obtain necessary license agreements.

#### **Document Disclaimer**

© 2000 by ZiLOG, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZiLOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. Except with the express written approval ZiLOG, use of information, devices, or technology as critical components of life support systems is not authorized. No licenses or other rights are conveyed, implicitly or otherwise, by this document under any intellectual property rights.

### Table of Contents

| General Overview                                                             |

|------------------------------------------------------------------------------|

| Discussion                                                                   |

| Summary                                                                      |

| Technical Support                                                            |

| Test Procedure2Equipment Used2General Test Setup and Execution2Test Results2 |

| References 2                                                                 |

| Appendix                                                                     |

### Acknowledgements

**Project Lead Engineer**

Chip Curtis

**Application and Support Engineer**

Chip Curtis

**System and Code Development**

Chip Curtis

Many applications requiring analog-to-digital conversions can be achieved with 8-bit MCUs without compromising accuracy, speed, or system cost.

### General Overview

Many embedded controller applications require that an analog voltage be measured. Depending on the application, a separate A/D converter (ADC) chip may be required because of the speed and resolution requirements. However, many designs do not require fast conversion speeds, and 8 to 11 bits of resolution is adequate. For instance, a digital thermostat samples the temperature periodically and turns the heater or air conditioner on or off when the temperature hits a trip point. Here, the measurement speed for the voltage across a thermistor is not critical, because the temperature is changing rather slowly. Conversion times on the order of milliseconds are acceptable. Capturing fast-changing signals, such as audio, requires a much faster conversion rate. If the highest audio frequency is 4 KHz coming into the ADC, the sample rate must be at least twice that frequency (8 KHz). Because of the limited processing time between samples (in this case 125 us), the ADC must complete a conversion quickly, giving the MCU time to process the data before the next sample. Because most designs are cost-sensitive, especially in consumer electronics, there may not be the luxury of adding relatively expensive ADC chips to the design. Design engineers must look for a more integrated solution, and ZiLOG has the solution.

### Discussion

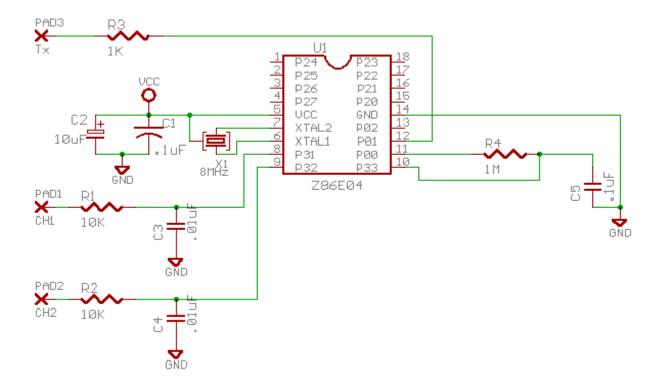

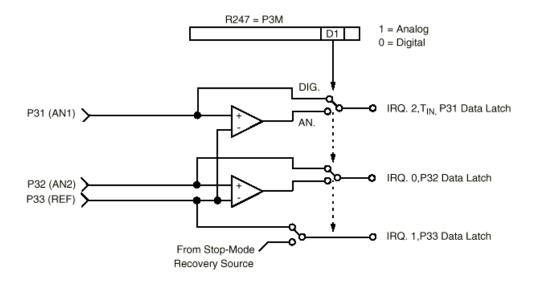

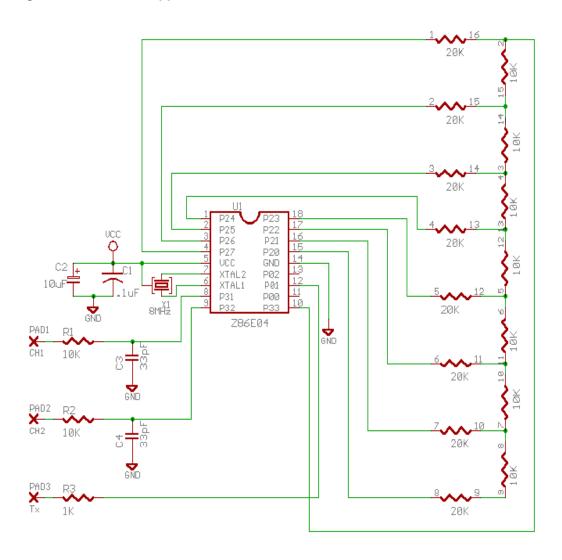

The on-board dual analog comparators, along with one counter/timer, are used to implement the ADC routines. The analog comparators are multiplexed with the digital inputs on port pins P31, P32, and P33. Figure 1 illustrates that configuration. The analog comparators are selected via the P3M register. The comparators share a common reference pin, P33. The input range of the comparators is 0V–4V. The input offset voltage is typically 10 mV with  $V_{cc}$  at 5.0V. The output of the comparators can be examined by a Test under Mask (TM) instruction on port P3. The outputs also generate an interrupt, based on the falling or rising edge of the comparator output. These outputs can connect to the P34 and P37 output pins under software control. The PCON register in the extended register file controls this connection (not available on C04/E04 and C08/E08). The comparators are enabled during HALT mode, but are disabled in STOP mode. Three ADC configurations are presented:

- Successive Approximation ADC

- Duty Cycle ADC

- 8 bit Duty Cycle ADC

The software routines are designed around the Z86E08/C08, but can be adapted for other selected Z8 and Z8Plus<sup>TM</sup> MCUs. The ZiLOG CCP emulator (ZiLOG PN Z86CCP00ZEM) was used to test the routines, and the routines also include a simple serial output to display the ADC output.

Figure 1. Port 3 Configuration

### Theory of Operation

#### Successive Approximation ADC

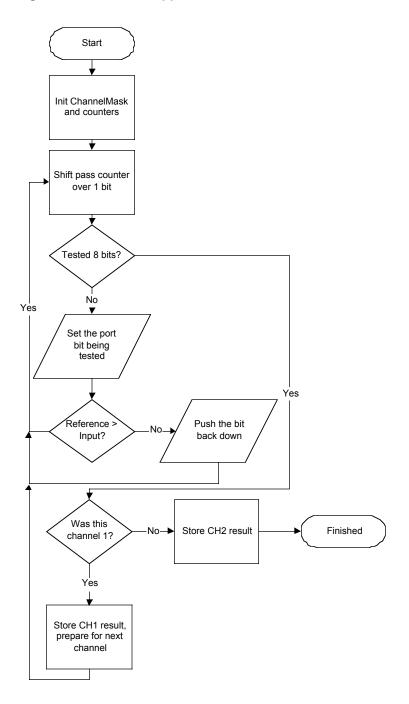

For applications requiring fast conversion times, consider the successive approximation method (Figure 2). This method uses a Digital-to-Analog Converter (DAC) in its feedback loop. The DAC is comprised of an R2R ladder connected to port P2. When a binary value is output at Port 2, a DC voltage proportional to the binary value appears at pin 1 of the ladder network. The DAC completes a binary search on the input voltage. This search is achieved by first setting the most significant bit (MSB) of the DAC and testing the comparator output. If the comparator output is 0, the DAC output for this bit is set to 0. If the comparator output is 1, then the DAC output for this bit is set to 1. The bits from output port 2 are individually tested in ascending order, performing the same test. When all the bits are tested, the conversion is complete. The output from the R2R resistor network becomes the comparator's reference voltage. The analog voltage to be measured

can be connected to either P31 or P32, the non-inverting inputs of the comparators.

To start the conversion, the MSB of P2 is set, resulting in a voltage of 5  $V_{cc}$  at the  $V_{REF}$  input of the comparator. If  $V_{cc}$  is 5V, then the voltage is 2.5V. The non-inverting comparator input is tested. If High, then the analog voltage must be 2.5V–5.0V.

The next bit, P26, is set, and the input port is tested again. If LOW, then bit P26 is reset. The process continues until all bits of P2 are tested. The resultant value at P2 is the digital representation of the analog input. With a crystal frequency of 8 MHz, the conversion time is approximately 110  $\mu$ S. Even more resolution is available from 10- and 12-bit R2R networks. Of course, more resolution requires more port pins.

### **Duty Cycle ADC**

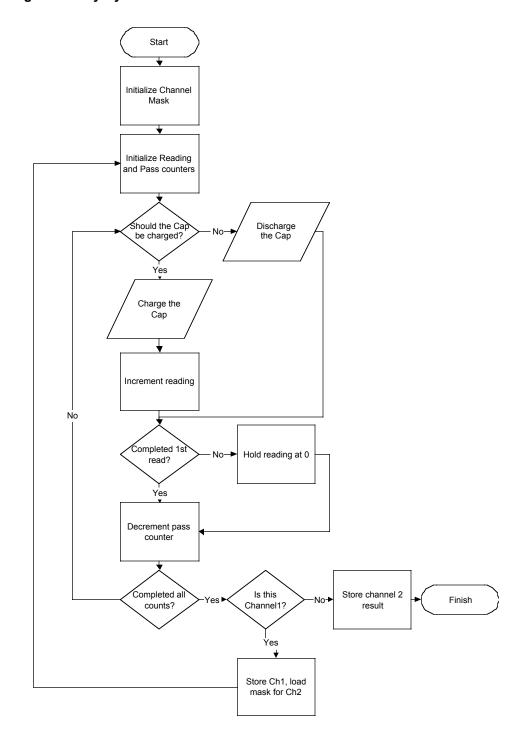

When speed is not important, a Duty Cycle Analog to Digital Converter is the perfect solution. This method works by measuring the time it takes a capacitor to charge up above the input voltage and discharge below the input voltage. Because the charge time is compared to the discharge time, component tolerances have no effect on accuracy, and the reading is linear. In addition to the comparators, only one port pin is required to control the RC network, leaving the balance of the I/O free. This example performs a two-channel, 11 bit conversion.

Because this method is based upon measuring time, the duty cycle ADC requires a stable time base. The stable time base is accomplished using only one interrupt for the timer and ensuring that the software's charge and discharge paths execute in the same amount of time.1

At each timer interrupt period, the capacitor is compared to the input voltage. If the capacitor is greater than the input voltage, than the capacitor is discharged and the pass counter is decremented. If the capacitor is less than the input voltage, the capacitor is charged, the reading is incremented, and the pass counter is decremented. When the pass counter reaches 0 the conversion is complete.

For highest stability, the capacitor must be charged to the input voltage before measurement begins. The easiest way to charge the capacitor to the input voltage is to perform two conversions and discard the first one. Also, the total conversion time must be an even multiple of the line frequency (60Hz or 50Hz). This example is 2048 counts x 130  $\mu$  S = 266mS, approximately 16 cycles at 60 Hz, with a 1M resistor and a.1  $\mu$  F capacitor. Total conversion time for both channels is 1.06S.

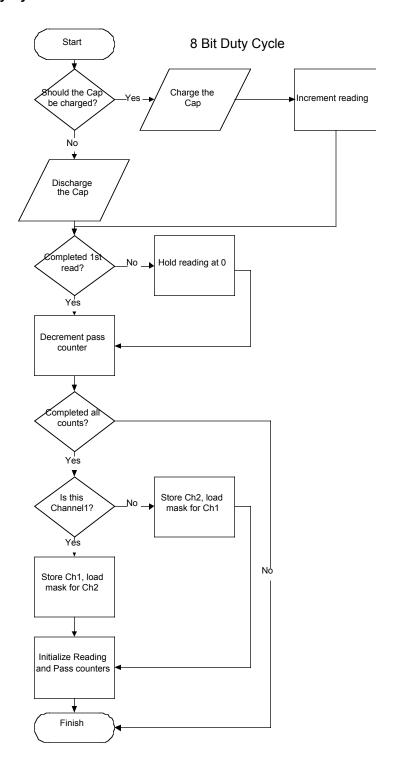

### 8-Bit Duty Cycle

The Duty Cycle conversion can be performed inline if a faster sampling rate is required. In this example, the time base is the code itself, so great care must be taken to ensure that each branch executes in the same number of clock cycles. The code contains a number of dummy instructions and balancing branches to keep all the timing consistent. Again, there can be no interrupts while the conversion is taking place. Because this routine executes faster, a different RC network is required. The value of the RC is not critical and is related to the total measurement period. On 5V systems, a good approximation for determining the time constant is RC=  $\pm/2.75$ , where  $\pm$  is the total number of counts multiplied by the time for one count. This routine takes 108 clock cycles per count, or 27  $\mu$  S on an 8-MHz resonator, for an RC of 2.5 mS (a.1  $\mu$  F capacitor and a 25K resistor). This routine measures both channels in 28 mS

### **Summary**

Applications requiring analog-to-digital conversions can be achieved without compromising accuracy, speed, or system cost. Design engineers can experiment with the routines for performance.

### Technical Support

#### **Source Code**

```

;TimerPorts.inc

Ports************************

;These equates are for addressing individual bits

В0

equ

1b

В1

equ

10b

100b

В2

equ

1000b

В3

equ

10000b

В4

equ

B5

equ

100000b

В6

equ

1000000b

equ

В7

10000000b

Port0

Rint

equ B0

; Integrating resistor for Duty Cycle

equ B1

Tx

;Transmit

__Port1_

;Not available on an 08

Port2

; Port two is used for the succesive approximation ADC, but does

```

| ;not | require | individual | bit | assignments |     |         |   |  |

|------|---------|------------|-----|-------------|-----|---------|---|--|

| ;    |         |            |     | Port3       |     |         |   |  |

|      | Channel | 1 equ      | В1  | ;Mask       | for | channel | 1 |  |

|      | Channel | 2 equ      | В2  | ;Mask       | for | channel | 2 |  |

| ;    |         |            |     | P01M        |     |         |   |  |

|      |         |            |     |             |     |         |   |  |

comment^

Table 1. Init P01M Timer Control Register

| Bit                                           | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

|-----------------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| R/W                                           | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset                                         | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| Note: R = Read, W = Write, X = Indeterminate. |     |     |     |     |     |     |     |     |

| Bit<br>Position | Bit<br>Field    | R/W | Reset<br>Value | Description                                                   |

|-----------------|-----------------|-----|----------------|---------------------------------------------------------------|

| D7-D6           | P04-P07 Mode    | R/W | 00             | P04–P07 Mode<br>00: Output<br>01: Input<br>1X: A12–A15        |

| D5              | External Timing | R/W | 0              | External Timing 0: Normal 1: Extended                         |

| D4-D3           | P10-P17 Mode    | R/W | 00             | P10-P17 00: Byte output 01: Byte input 10: AD0- = AD7 11: HiZ |

| D2              | Internal Stack  | R/W | 0              | 1 Internal Stack                                              |

| D1-D0           | P00-P03 Mode    | R/W | 00             | P00-P03 Mode<br>00: Output<br>01: Input                       |

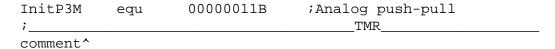

Table 2. Init P3M Timer Control Register

| Bit                                           | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

|-----------------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| R/W                                           | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset                                         | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| Note: R = Read, W = Write, X = Indeterminate. |     |     |     |     |     |     |     |     |

| Bit<br>Position | Bit<br>Field | R/W | Reset<br>Value | Description                                                                                          |

|-----------------|--------------|-----|----------------|------------------------------------------------------------------------------------------------------|

| D7              | Parity       | R/W | 0              | 0: Parity ON<br>1: Parity OFF                                                                        |

| D6              | P30          | R/W | 0              | 0: P30 = Input,P37 = Output<br>1: P30 = Serial in, P37 = Serial out                                  |

| D5              | P31          | R/W | 0              | 0: P31 = Input, P36 = Output<br>1: P31 = DAV2/RDY2, P36 = RDY2/<br>DAV2                              |

| D4 -D3          | P33          | R/W | 00             | 00: P33 = Input<br>11: P33 = DAV1/RDY1, P34 = RDY/<br>DAV1<br>01 or 10: P34 = Out, P33 = In P34 = DM |

| D2              | P32          | R/W | 0              | 0: P32 = Input, P35 = Output<br>1: P32 = DAV0/RDY0, P35 = RDY0/<br>DAV0                              |

| D1              | P3           | R/W | 0              | 0: Digital P3 input<br>1: Analog P3 input                                                            |

| D0              | P2           | R/W | 0              | 0: Open drain P2<br>1: Push-pull P2                                                                  |

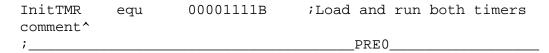

**Table 3. InitTMR Timer Control Register**

| Bit                                           | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

|-----------------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| R/W                                           | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset                                         | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| Note: R = Read, W = Write, X = Indeterminate. |     |     |     |     |     |     |     |     |

| Bit<br>Position | Bit<br>Field     | R/W | Reset<br>Value | Description                                                                                                    |

|-----------------|------------------|-----|----------------|----------------------------------------------------------------------------------------------------------------|

| D7-D6           | T <sub>OUT</sub> | R/W | 00             | 00: No T out<br>01: T0 out<br>10: T1 out<br>11: Internal clock out                                             |

| D4-D5           | CLKIN            | R/W | 00             | 00: External clock input<br>01: Gated input<br>10: Trigger input, no retrigger<br>11: Trigger input, retrigger |

| D3              | T1               | R/W | 0              | 0: Disable T1<br>1: Enable T1                                                                                  |

| D2              | T1               | R/W | 0              | 1: Load T1                                                                                                     |

| D1              | T0               | R/W | 0              | 0: Disable T0<br>1: Enable T0                                                                                  |

| D0              | T0               | R/W | 0              | 1: Load T0                                                                                                     |

\_

Table 4. InitPRE0 Timer Control Register

| R/W                                           | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

|-----------------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Reset                                         | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| Note: R = Read, W = Write, X = Indeterminate. |     |     |     |     |     |     |     |     |

| Bit<br>Position | Bit<br>Field | R/W | Reset<br>Value | Description                         |

|-----------------|--------------|-----|----------------|-------------------------------------|

| D2-D7           | PRE1         | R/W | 00             | Prescaler 1–64 (01h–00h)            |

| D1              | Reserved     | R/W | 0              | Reserved; must be 0                 |

| D0              | Count Mode   | R/W | 0              | Count Mode 0: Single pass 1: Modulo |

\_

InitPRE0 equ 1<<2|1 ;8MHz/2SCLK/4TCLK/;1PRE0 = 1MHz Modulo

InitT0 equ 130 ;1µs\*130 = 130µs

comment^

Table 5. InitPRE1 Timer Control Register

| R/W                                           | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

|-----------------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Reset                                         | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| Note: R = Read, W = Write, X = Indeterminate. |     |     |     |     |     |     |     |     |

\_\_\_\_\_PRE1\_\_\_\_\_

| Bit<br>Position | Bit<br>Field | R/W | Reset<br>Value | Description                                    |

|-----------------|--------------|-----|----------------|------------------------------------------------|

| D2-D7           | PRE1         | R/W | 00             | Prescaler 1-64 (01h - 00h)                     |

| D1              | T1           | R/W | 0              | 0: External T1 source<br>1: Internal T1 source |

| D0              |              | R/W | 0              | 0: Single pass<br>1: Modulo                    |

InitPRE1.equ(4\*4)+3;(2sclk\*4tclk/8MHz)\*4 = 4 $\mu$ s, Int Mod

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

\* Module Name:SDDAC.Asm

AN004001-Z8X0400

| bat<br>Cre                   | byright:(c)21LOG 1999, All Rights Reserved<br>ce:7/27/99<br>eated by:Chip Curtis<br>dified by:                                                                                     |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| t Des                        | scription: This module performs a two channel Succesive Approximation Analog to Digital Conversion When a conversion is complete the ASCII data is transmitted to an RS232 device. |

| *///////////                 | '/////////////////////////////////////                                                                                                                                             |

|                              | clude section                                                                                                                                                                      |

| inclu                        | de "TimerPorts.inc";Timer and port definitions                                                                                                                                     |

|                              | **************                                                                                                                                                                     |

|                              | obal variables<br>************************************                                                                                                                             |

| globa                        | ls on                                                                                                                                                                              |

|                              | n point_ah, point_al, point_bh, point_bl                                                                                                                                           |

| Glc Glc                      | **************************************                                                                                                                                             |

|                              | n Xmit;Transmits conversion                                                                                                                                                        |

| ' Int                        | terrupt Vectors                                                                                                                                                                    |

| vecto:<br>segme:             | **************************************                                                                                                                                             |

| * Mai                        | :*************************************                                                                                                                                             |

| Main:                        |                                                                                                                                                                                    |

| ;                            | Initialization                                                                                                                                                                     |

| clr<br>ld<br>ld<br>clr<br>ld | <pre>imr</pre>                                                                                                                                                                     |

| ;                            | Perform Conversion                                                                                                                                                                 |

| cal                          | LISAADC ; Perform a Conversion                                                                                                                                                     |

|                              | Display                                                                                                                                                                            |

|                              |                                                                                                                                                                                    |

```

clr point_ah ;Only an

ld point_al, channel1 ;Low byte

;Only an 8 bit result

clr

point_bh

;Only an 8 bit result

point_bl, channel2 ;Low byte

;Send out ASCII

callXmit

irMain

;Do another conversion

Function Name: SAADC

Returns: channel1, channel2 loaded with ADC

Entry Values: None

Description: A two channel Successive Approximation Analog to

to digital conversion is performed on P31 and P32

Notes

Depending on your application you may want to dis-

able interrupts upon entry to this routine.

*******************

defineRam, SPACE= RFILE

segmentRam ;Our Ram

; Counter for passes through ADC loop

a2dPass

ds 1

channel1 ds 1 ;Latched reading of channel 1 ;Latched reading of channel 2 channelMaskds 1 ;Mask for addressing channels

segmentcode

Init

SAADC:

ld channelMask, #Channell; Measure channel one first

SAADC40:

clr P2

;Clear the reference

clr a2dPass

;Clear the loop counter

;Seed the counter

scf

Measure

SAADC10:

rrc a2dPass

;Next bit

C, SAADC20

;All eight bits tested

jr

P2, a2dPass ;Set the bit on port 2

call SAADC50

;Dummy call for a delay

P3, channelMask ; Is the reference high or low?

tm

NE, SAADC10 ;Still Low, leave ON, test a new bit

jr

P2, a2dPass ;Clear this bit

xor

; and test a new one

SAADC10

jr

```

### Application Note Analog-to-Digital Conversion Techniques Using ZiLOG Z8 MCUs

| i                                       |                                                                                                                  | Store Measurement                                                                         |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| SAADC20:<br>cp<br>jr                    | channelMask,<br>NE, SAADC30                                                                                      | <pre>#Channel1;Did we finish channel 1? ;Nope</pre>                                       |

| ld<br>ld<br>jr                          | channell, P2<br>channelMask,<br>SAADC40                                                                          | ;Store the result from Port2<br>#Channel2;Read the next channel<br>;Start the measurement |

| SAADC30:<br>ld                          | channel2, P2                                                                                                     | ;Store the result from P2                                                                 |

| SAADC50:<br>ret                         |                                                                                                                  | ;Conversion done                                                                          |

| * Mc * Cc * Da * Cr * Mc * * Mc * * * * | odule Name:Dut<br>opyright:(c)Zi<br>ate:7/27/99<br>reated by:Chip<br>odified by:<br>escription:Thi<br>Dut<br>Whe | LOG 1999, All Rights Reserved                                                             |

| /////////                               | ///////////////////////////////////////                                                                          | //////////////////////////////////////                                                    |

|                                         |                                                                                                                  | ***********                                                                               |

| incl                                    | ude "TimerPo                                                                                                     | orts.inc" ;Timer and port definitions                                                     |

| * G]                                    | lobal variable                                                                                                   | **************************************                                                    |

| glob                                    | als on                                                                                                           |                                                                                           |

| exte                                    | rn point_ah, p                                                                                                   | point_al, point_bh, point_bl                                                              |

| * G]                                    | lobal function                                                                                                   | **************************************                                                    |

| exte                                    | rn Xmit                                                                                                          | ;Transmits conversion                                                                     |

| *****                                   | *****                                                                                                            | ***********                                                                               |

| * Ir                                    | nterrupt Vector                                                                                                  | rs                                                                                        |

```

vector reset = Main

vector irq4 = A2D

Main

******************

Main:

_____Initialization_____

ld spl, #80H

;Initialize the stack.

ld pre0, #InitPRE0 ;Initialize T0 prescaler

ld pre1, #InitPRE1 ;Initialize T1 Prescaler

ld t0, #InitT0 ;Load T0 value

;______Main Loop_____

MainLoop:

clr

ld

; Initialize all port modes too

clr p2m

ld p3m, #InitP3M

_____Conversion Done?_____

MainWait:

a2dPass+1, #Low 4096; Has the pass counter reset?

ср

NE, MainWait ; Nope, wait

jr

a2dPass, #High 4096 ;How about the high byte?

ср

NE, MainWait ; Nope

jr

channelMask, #Channel1; Is it the first channel?

ср

NE, MainWait ; No, keep waiting

jr

_____Display_____

;Serial communication will start

di

point_ah, channel1 ;High byte

ld

point_al, channel1+1 ;Low byte

ld

point_bh, channel2 ;High byte

ld

point_bl, channel2+1 ;Low byte

ld

```

callXmit ;Send out ASCII ;Serial communication finished jrMainLoop ;Do another conversion \*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\* Function Name: InitADC returns: None entry values: None Description: Initializes all ADC registers Notes InitADC: ;Place functions in these sections, starting with init func-;tion.Example function called SysInit. ret \*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\* A2D Routine \*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\* ;This routine performs a two channel A2D conversion by way of a ;timer ISR. The assumption will be made that the Timer and its ; interrupt have already been set-up, and that P3M has been config-;ured as an analog port. As always, you should initialize your RAM ; too. The timing in this routine is critical, so don't mess with ; anything until AFTER the "Timing not critical" comment. ;This routine assumes that the timer is running at 130 µs and that ; you are using a .luF integrating capacitor and a 1M integrating ;resistor. \*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\* defineRam, ALIGN= 2, SPACE= RFILE segmentRam a2dReading dw a2dPass dw ; Counter for passes through ADC loop channel1dw 1 channel2dw 1 ;Latched reading of channel 1 ;Latched reading of channel 2 channelMaskdb 1 ;Mask for addressing channels segmentcode Charge MACRO PO, #Rint ; Change port assignment for your port orMACEND DisCharge MACRO PO, #~Rint ; Change port assignments for your port and MACEND

```

A2D:

tm

P3, channelMask ;10Cy Is the capacitor charged up?

jr

NE, A2D10 ;10/12Cy Nope, still counting, keep

; charging

__Discharge Path__

;6Cy Delay so paths are equal

nop

nop

;6Cy Delay so paths are equal

DisCharge

;32Cy Total, Discharge the capacitor

____Timing Not Critical__

A2D30:

a2dPass, #HIGH 2048; Are we still settling the capaci

;tor?

ULT, A2D20

;No, we are counting

jr

a2dReading+1

clr

;Hold the reading at zero

A2D20:

decw a2dPass

;Next pass

NE, A2DX

;We aren't done yet

channelMask, #Channel1; Is this Channel1?

NE, A2D40 ; Nope, do channel two

jr

a2dPass, #channel1; We'll use this as a pointer

ld

channelMask, #Channel2; Now the other mask

ld

;Reload

jr

A2D50

A2D40:

ld a2dPass, #channel2

channelMask, #Channel1 ; Now read channel one again

A2D50:

@a2dPass, a2dReading ;Store the HB

ld

inc

a2dPass ; and

ld

@a2dPass, a2dReading+1 ;the LB

clr

a2dReading

;Get ready to start all over

a2dReading+1

clr

a2dPass, #HIGH 4096 ;2 passes of 2048 counts

a2dPass+1, #LOW 4096

A2DX:

iret

_____Charge Path_____

A2D10:

incw a2dReading

;10Cy We have a reading

;32Cy Total, Charge Cap

Charge

A2D30

;Rejoin common path

jr

*******************

Module Name: DutyCycle8.Asm

```

```

Copyright: (c) ZiLOG 1999, All Rights Reserved

Date:7/27/99

Created by: Chip Curtis

Modified by:

Description: This is an example of a two channel 8 bit

Duty Cycle Analog to Digital Conversion.

When a conversion is complete the ASCII data

is transmitted to an RS-232 device.

Include section

********************

include

"TimerPorts.inc"

;Timer and port definitions

*******************

Global variables

*******************

globals on

extern point_ah, point_al, point_bh, point_bl

Global function declarations

extern Xmit

;Transmits conversion

Interrupt Vectors

vector reset = Main

segmentcode

Main

Main:

Initialization

clr

imr

;No IRQs on, just in case

clr

;Reset rp just in case

rp

spl, #80H

ld

;Initialize the stack. It should be

p01m, #InitP01M ;empty at the top of the Main loop

ld

;Initialize all port modes too

clr

p2m

p3m, #InitP3M

ld

ld

pre1, #InitPRE1 ;Initialize T1 Prescaler

```

|              |                                         | Perfo           | rm Conve         | ersion          |                                         |         |                  |

|--------------|-----------------------------------------|-----------------|------------------|-----------------|-----------------------------------------|---------|------------------|

| call.        | A2D                                     | ;P              | erform a         | a Conversi      | on                                      |         |                  |

|              |                                         | Dis             | play             |                 |                                         |         | _                |

| clr<br>ld    | <pre>point_ah point_al, ch</pre>        | annel1          | ;Only<br>;Low by | an 8 bit<br>⁄te | result                                  |         |                  |

| clr<br>ld    | <pre>point_bh point_bl, ch</pre>        | annel2          |                  | an 8 bit<br>te  | result                                  |         |                  |

| call         | Xmit                                    |                 | ;Send            | out ASCII       | -<br>-                                  |         |                  |

| jrMa<br>**** | in<br>******                            | * * * * * * *   |                  | nother con      |                                         | *****   |                  |

| **           | Module Na                               | ame:            |                  | Xmit.asm        |                                         |         |                  |

| *            | Copyright                               | :               |                  | (c)ZiLOG        | 1999, All R                             | ights   |                  |

| Reser        | rved                                    |                 |                  |                 |                                         |         |                  |

| *            | Date:                                   |                 |                  | 7/27/99         |                                         |         |                  |

| *            | Created by                              | γ:              |                  | Chip Curt       | is                                      |         |                  |

| *            | Modified 1                              | by:             |                  |                 |                                         |         |                  |

| *            |                                         |                 |                  | _               |                                         |         |                  |

| *            | Description                             | on:This         | module i         | s used to       |                                         |         | tra <b>as</b> ba |

| seria<br>*   | 11                                      |                 |                  | ,               |                                         |         |                  |

| *            |                                         | _               |                  | _               | two binary                              |         |                  |

| *            |                                         |                 | _                |                 | e routine,                              | лсаті   | F                |

| and t        | hen                                     | CO CITE         | e routin         | e, conver       | ted to BCD,                             | ASCII   | L                |

| *            | .11611                                  | transr          | mitted.          |                 |                                         |         |                  |

| *            |                                         | cransi          | iii ccca.        |                 |                                         |         |                  |

| ****         | *****                                   | * * * * * * *   | *****            | *****           | ******                                  | *****   |                  |

| *////        | /////////////////////////////////////// | ////////        | ////////         | /////////       | /////////////////////////////////////// | /////// |                  |

| *////<br>/   | /////////////////////////////////////// | ////////        | ////////         | /////////       | /////////////////////////////////////// | /////// |                  |

| ****         | *****                                   | *****           | *****            | *****           | ******                                  | *****   |                  |

| **           | Include :                               |                 |                  |                 |                                         |         |                  |

| ****         | *****                                   | * * * * * * * * | *****            | *****           | *****                                   | *****   |                  |

| inclu<br>*   | ude "TimerPo                            | orts.ind        | C "              | ;Timer ar       | _                                       |         |                  |

| ****         | *****                                   | *****           | *****            | *****           | ******                                  | *****   |                  |

| *            | _                                       |                 |                  |                 |                                         |         |                  |

| *            | Global var                              | riables         |                  |                 |                                         |         |                  |

| * * * * * * * * *    | ****                                                                                                                                        | *********                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      | globals                                                                                                                                     | on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| _                    | _                                                                                                                                           | e= RFILE;Ports are absolute ;Anywhere else                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| segment<br>ds 4      | Bank0                                                                                                                                       | ;Skip over ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| unctions<br>ways con | using wor                                                                                                                                   | re used for passing arguments<br>king register addressing.Their<br>mporary much like a multiple<br>must reside in Bank0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                      |                                                                                                                                             | purpose word high byte<br>Purpose word low byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                      |                                                                                                                                             | purpose word high byte<br>Purpose word low byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ds 1<br>ds 1         |                                                                                                                                             | purpose single byte<br>purpose loop counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| it                   |                                                                                                                                             | **************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| segment              | code                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                      |                                                                                                                                             | ;Save all the data to transmit;at a later time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                      | SendM                                                                                                                                       | essage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ld poi<br>call Se    | nt_bl, #Lo<br>ndMsg<br>Convert<br>n2BCD                                                                                                     | ;Print it<br>Measurement<br>;Make it BCD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                      | k0, org= Ram, Sp segment ds 4 wing ass unctions ways con or proce ds 1 ds 1 ds 1 ds 1 ds 1 ds 1 ds point ld point ld point ld point call Se | globals  k0, org= 00H, Space Ram, Space= RFILE segment Bank0 ds 4  wing assignments as unctions using workways considered teleor processor. They ds 1 ; General ds 1 ; Gene |

| ;Send Messag                                  | re                               |

|-----------------------------------------------|----------------------------------|

| ld R point_bh, #High                          |                                  |

|                                               | ;ofline                          |

| ld.R point_bl, #Low                           | Ch2Msg;message                   |

| call SendMsg                                  |                                  |

|                                               |                                  |

| ;Convert Me                                   | asurement                        |

| pop point_al                                  | Grab the other                   |

| pop point_ai                                  | ;channel's data                  |

| pop point_ah                                  | that was on the stack            |

| pop point_an                                  | renae was on the seach           |

| call Bin2BCD                                  | ;Convert it                      |

| call SendASCII                                | ;and send that too               |

| Call Schapell                                 | rand send that too               |

|                                               |                                  |

| ld .R point_bh, #Hig                          | h EOLMsg ;Send the end of ;line  |

| ld .R point_bl, #Low                          | EOLMsg ;message call             |

| call SendMsg                                  |                                  |

|                                               |                                  |

| ret                                           |                                  |

|                                               |                                  |

|                                               |                                  |

| ***********                                   | *******                          |

| *                                             |                                  |

|                                               |                                  |

| Ch1Msg:                                       |                                  |

| .asciz "Ch1: "                                | Channel 1 prompt                 |

|                                               |                                  |

| ******                                        |                                  |

| *                                             | ******                           |

|                                               |                                  |

| * Ch2Msg ************************************ | <b>+++++++++++++++++++++++++</b> |

| *                                             |                                  |

| "                                             |                                  |

| Ch2Msg:                                       | • 672                            |

| .asciz Ch2: "                                 | ;Channel 2 prompt                |

| *                                             |                                  |

|                                               |                                  |

| * EOLMsg ************************************ | ****                             |

| *                                             |                                  |

|                                               |                                  |

| EOLMsg:                                       |                                  |

```

CR, LF and terminator

db 13,10,0

*****************

*****************

* Function Name: Bin2BCD

* Returns

:Result in pointb

* Entry Values :16 bit binary number in pointa

* Description :Converts a 16 binary number to a 4

:digit BCD number

* Notes

:points and loop are destroyed in :the

process

Bin2BCD:

clr point_bh ;Clear the destination

clr point bl

ld

.R loop, #16 ;Sixteen bits

Bin2BCD10:

rlc point_al ;Shift the LB over one

point_ah

;and the HB, carry now

rlc

; has the bit

adc .R point_bl, .R point_bl ;add the result

; on itself

;for a X2

point bl

da

adc .R point_bh, .R point_bh ; and the HB

point_bh

djnz.R loop, Bin2BCD10 ;Loop until done

ret

* Function Name:

SendMsq

* Returns

:None

* Entry Values :point_b points at asciz message

* Description : Uses SendChr to send an asciz

```

|            |             | : m        | essage      |             |           |                                         |

|------------|-------------|------------|-------------|-------------|-----------|-----------------------------------------|

| *          |             |            |             |             |           |                                         |

| * Notes    | · * * * * · | :<br>***** | *****       | *****       | ****      | *****                                   |

| *          |             |            |             | ^ ^ ^ ^ ^ ^ | ^ ^ ^ ^ ^ |                                         |

| SendMsg:   |             |            |             |             |           |                                         |

| Bellanby.  | ldc         | .R t.e     | mp. @.      | iog RR      | nt. bh    | Grab a character                        |

|            |             | temp,      | _           | FOT         |           | ;Is it The                              |

|            | -           |            |             |             |           | ;Terminator?                            |

|            | jr          | NZ, S      | endMsg<br>t | 10          |           | ;No, I'll be back                       |

| SendMsg10  |             |            |             |             |           |                                         |

| Sendinsgro | call        | Send       | Chr         |             | ;Tran     | smit the character                      |