## **Z90255 ROM and Z90251 OTP**

# 32 KB Television Controller with OSD

Product Specification PS001301-0800

ZiLOG WORLDWIDE HEADQUARTERS • 910 E. HAmilton Avenue • Campbell, CA 95008 Telephone: 408.558.8500 • Fax: 408.558.8300 • www.ZiLOG.com

This publication is subject to replacement by a later edition. To determine whether a later edition exists, or to request copies of publications, contact

ZiLOG Worldwide Headquarters

910 E. Hamilton Avenue Campbell, CA 95008 Telephone: 408.558.8500 Fax: 408.558.8300 www.ZiLOG.com

Windows is a registered trademark of Microsoft Corporation.

#### **Document Disclaimer**

© 2000 by ZiLOG, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZiLOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. Except with the express written approval ZiLOG, use of information, devices, or technology as critical components of life support systems is not authorized. No licenses or other rights are conveyed, implicitly or otherwise, by this document under any intellectual property rights.

### Z90255 ROM and Z90251 OTP 32 KB Television Controller with OSD

## Table of Contents

| 1 | Overv<br>1.1<br>1.2<br>1.3                                                  | view 1<br>Pin Assignment and Descriptions<br>Single-Purpose Pin Descriptions<br>Multiplexed Pin Descriptions                                                                                                                                                 | 7                                                      |

|---|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| 2 | Memo<br>2.1<br>2.2<br>2.3                                                   | ory Description<br>Standard Register File<br>Expanded Register File<br>Program Memory                                                                                                                                                                        | . 10<br>. 11                                           |

| 3 | Watc                                                                        | h-Dog Timer (WDT)                                                                                                                                                                                                                                            | . 15                                                   |

| 4 | Stop<br>4.1<br>4.2<br>4.3                                                   | Mode and Halt Mode Operation<br>Power-Down Halt-Mode Operation<br>Stop Mode Operation<br>STOP Mode Recovery Register                                                                                                                                         | . 16<br>. 17                                           |

| 5 | On-S<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10 | creen Display<br>OSD Position<br>Second Color Feature<br>Mesh and Halftone Effect<br>OSD Fade<br>Inter-Row Spacing<br>Character Generation<br>Character Size and Smoothing Effect<br>Fringing Effect<br>Display Attribute Control<br>HV Interrupt Processing | . 22<br>25<br>28<br>33<br>36<br>37<br>39<br>40<br>. 40 |

| 6 | Z902                                                                        | 55 I2C Master Interface                                                                                                                                                                                                                                      | . 53                                                   |

| 7 | Input/<br>7.1<br>7.2<br>7.3                                                 | /Output Ports<br>Port 4 Pin-Out Selection Register<br>Port 5 Pin-Out Selection Register<br>Port 6 Data Register                                                                                                                                              | 59<br>. 62                                             |

| 8 | Infrar                                                                      | ed Interface                                                                                                                                                                                                                                                 | . 65                                                   |

| 9  | Pulse                  | Width Modulators                   | 68 |

|----|------------------------|------------------------------------|----|

|    | 9.1                    | PWM Mode Register                  | 68 |

|    | 9.2                    | PWM1 through PWM11                 | 70 |

|    | 9.3                    | Digital/Analog Conversion with PWM | 79 |

| 10 | Analo                  | og-to-Digital Converter            | 80 |

| 11 | Elect                  | rical Characteristics              | 83 |

|    | 11.1                   | Absolute Maximum Ratings           | 83 |

|    | 11.2                   | DC Characteristics                 |    |

|    | 11.3                   | AC Characteristics                 | 85 |

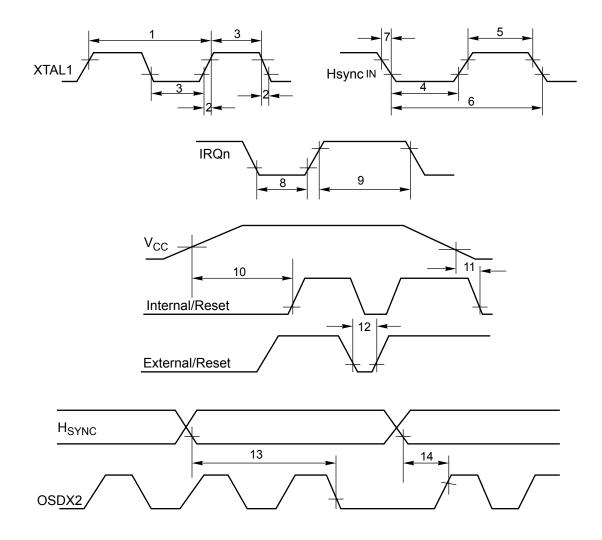

|    | 11.4                   | Timing Diagram                     | 86 |

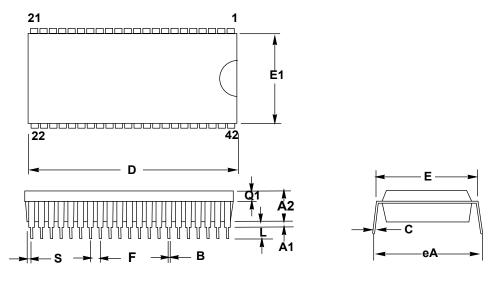

| 12 | Pack                   | aging                              | 87 |

|    | Orde                   | ring Information                   | 88 |

|    | ROM                    | Code Submission                    | 88 |

|    | Customer Feedback Form |                                    |    |

## List of Figures

| 1  | Z90255-Based TV System Application                    | 2    |

|----|-------------------------------------------------------|------|

| 2  | Z90255 Block Diagram                                  |      |

| 3  | Z90255 and Z90251 Pin Assignments                     |      |

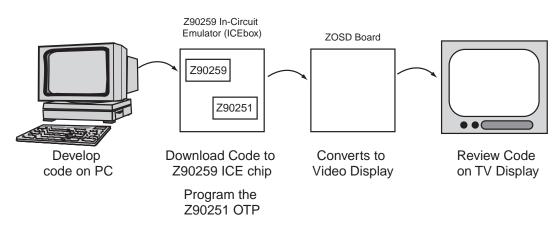

| 4  | Code Development Environment                          | . 10 |

| 5  | Register File Map                                     |      |

| 6  | Program Memory Map                                    |      |

| 7  | Stop Mode Recovery Source/Level Select                |      |

| 8  | Positive and Negative Sync Signals                    |      |

| 9  | Second Color Display                                  |      |

| 10 | Mesh On                                               |      |

| 11 | Video Fade (Example)                                  | 34   |

| 12 | Character Pixel map in CGROM                          |      |

| 13 | Example of a Multiple Character Icon                  | 38   |

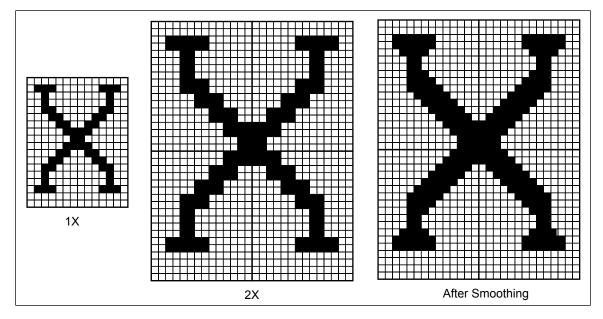

| 14 | Smoothing Effect on 2X Character Size                 | . 39 |

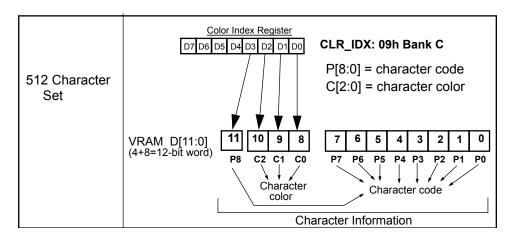

| 15 | VRAM Data Path for 512 Character Set                  |      |

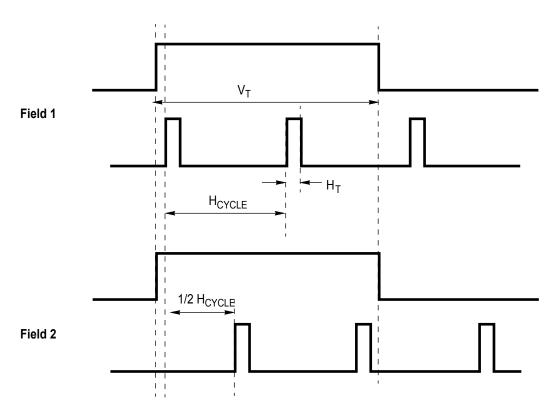

| 16 | H <sub>SYNC</sub> and V <sub>SYNC</sub> Specification | . 52 |

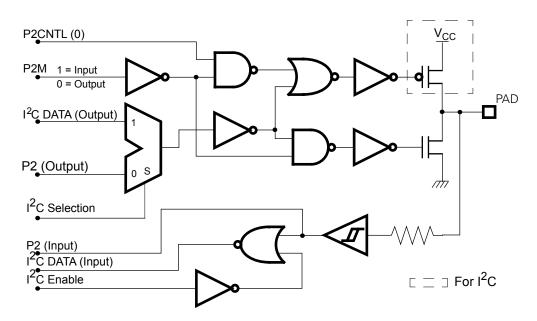

| 17 | Bidirectional Port Pin Pad Multiplexed with I2C Port  | 53   |

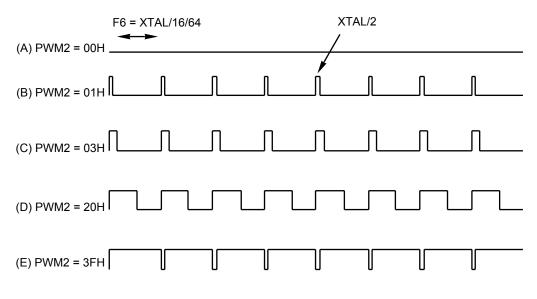

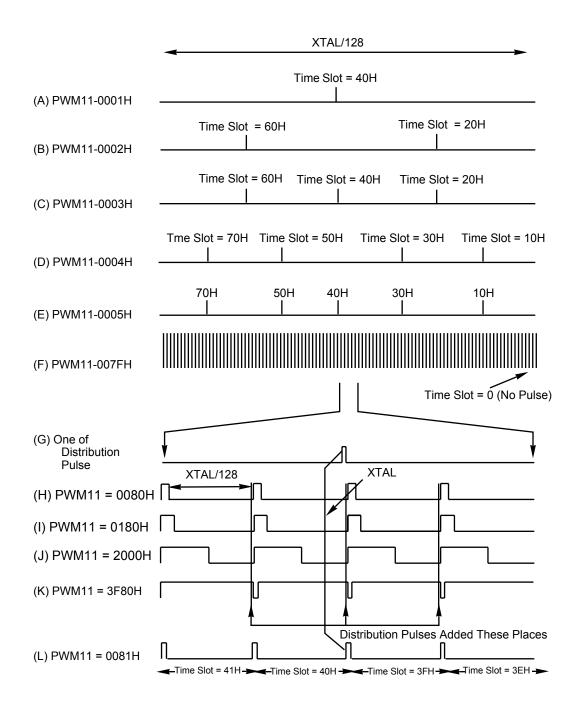

| 18 | Pulse Width Modulator Timing Diagram, 6 Bit           | .71  |

| 19 | Pulse Width Modulator Timing Diagram, 14-Bit          | .72  |

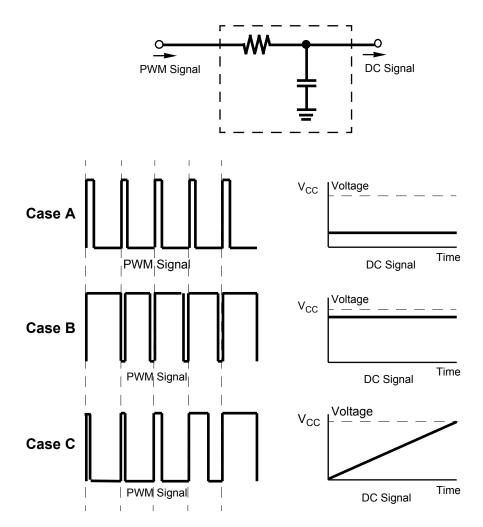

| 20 | Analog Signals Generated from PWM Signals             | .79  |

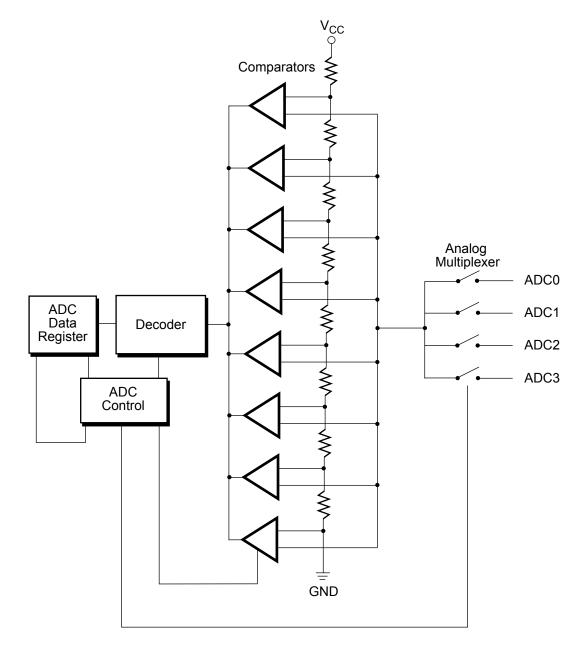

| 21 | ADC Block Diagram                                     | .82  |

| 22 | Timing Requirements of External Inputs                | 86   |

| 23 | 42-Lead Shrink Dual-in-line Package (SDIP)            | 87   |

|    |                                                       |      |

Z90255 ROM and Z90251 OTP 32 KB Television Controller with OSD

## List of Tables

| 1  | Z90255 Production Device Pin Assignment                 | 6  |

|----|---------------------------------------------------------|----|

| 2  | Single-Purpose Pin Descriptions                         | 7  |

| 3  | Multiplexed Pin Descriptions                            | 8  |

| 4  | Register File Map                                       | 13 |

| 5  | Watch-Dog Timer Mode Register 0Fh: Bank F               | 15 |

| 6  | Stop Mode Recovery (SMR) Register 0Bh: Bank F (SMR)     | 19 |

| 7  | Stop Mode Recovery Source                               |    |

| 8  | OSD Control Register 00h:Bank A (OSD_CNTL)              | 22 |

| 9  | Vertical Position Register 01h:Bank A (VERT_POS)        | 24 |

| 10 | Horizontal Position Register 02h:Bank A (HOR_POS)       | 25 |

| 11 | Second Color Control Register 07h:Bank A (SNDCLR_CNTRL) | 26 |

| 12 | Second Color Register 08h:Bank A (SNDCLR)               | 26 |

| 13 | Mesh Column Start Register 04h: Bank F (MC_St)          | 29 |

| 14 | Mesh Column End Register 05h: Bank F (MC_End)           | 30 |

| 15 | Mesh Row Enable Register 06h: Bank F (MR_En)            | 30 |

| 16 | Mesh Control Register 07h: Bank F (MC_Reg)              | 31 |

| 17 | BGR Mesh Colors                                         | 33 |

| 18 | Fade Position Register 1 05h: Bank A (FADE_POS1)        | 35 |

| 19 | Fade Position Register 2 06h: Bank A (FADE_POS2)        | 35 |

| 20 | Row Space Register 04h: BankA (ROW_SPACE)               | 36 |

| 21 | RGB Colors                                              | 40 |

| 22 | Display Attribute Register 03h: Bank A (DISP_ATTR)      | 41 |

| 23 | VRAM Structure and Memory Map                           | 43 |

| 24 | Color Palette Selection Bits                            | 45 |

| 25 | Color Index Register 09h: Bank C (CLR_IDX)              | 45 |

| 26 | Color Palette 0 Register 09h: Bank A (CLR_P0)           | 46 |

| 27 | Color Palette 1 Register 0Ah: Bank A (CLR_P1)           | 46 |

| 28 | Color Palette 2 Register 0Bh: Bank A (CLR_P2)           | 47 |

| 29 | Color Palette 3 Register 0Ch: Bank A (CLR_P3)           | 47 |

| 30 | Color Palette 4 Register 0Dh: Bank A (CLR_P4)           | 47 |

| 31 | Color Palette 5 Register 0Eh: Bank A (CLR_P5)           | 48 |

| 32 | Color Palette 6 Register 0Fh: Bank A (CLR_P6)           | 48 |

| 33 | Row Attribute Register (ROW_ATTR)                       | 49 |

| 34 | HV Interrupt Status Register 07h: Bank C (INT_ST)       | 50 |

| 35 | Master I2C Control Register 0Ch: Bank C (I2C_CNTL)      | 54 |

| 36 | Master I2C Command Register 0Bh: Bank C (I2C_CMD)       | 55 |

| 37       | Master I2C Data Register 0Ah: Bank C (I2C_DATA) 55                               |

|----------|----------------------------------------------------------------------------------|

| 38       | Master I <sup>2</sup> C Bus Interface Commands                                   |

| 39       | Port configuration Register 00h: Bank F (PCON)                                   |

| 40       | Port 2 Mode Register F6h: P2M                                                    |

| 40<br>41 | Port 2 Data Register 02h: P2                                                     |

| 41       | Port 4 Pin-Out Selection Register 08h: Bank C (PIN_SLT)                          |

| 42<br>43 | Port 4 Data Register 05h: Bank C (PRT4 DTA)                                      |

| 43<br>44 | Port 4 Data Register 05h. Bank C (PRT4_DTA)                                      |

| 44<br>45 | PWM Mode Register 0Dh: Bank B (P_MODE)                                           |

| 45<br>46 | Port 5 Data Register 0Ch: Bank B (PRT5_DTA)                                      |

| 40<br>47 | Port 5 Direction Control Register 0Eh: Bank B (PRT5_DTA)                         |

| 47<br>48 | Port 6 Data Register 03h: Bank F (PRT6_DTA)                                      |

| 40<br>49 | Port 6 Direction Control Register 02h: Bank F (PRT6_DTA)                         |

| 49<br>50 | Timer Control Register 0 01h: Bank C (TCR0)                                      |

| 50<br>51 | Timer Control Register 1 02h: Bank C (TCR0)                                      |

| 52       | IR Capture Register 0 03h: Bank C (IR_CP0)                                       |

|          | IR Capture Register 1 04h: Bank C (IR_CP0)                                       |

| 53<br>54 | PWM Mode Register 0Dh: Bank B (P_MODE)                                           |

| 54<br>55 |                                                                                  |

|          | Port 4 Pin-Out Selection Register 08h: Bank C (PIN_SLT)                          |

| 56<br>57 |                                                                                  |

| 57<br>58 | PWM 2 Data Register 03h: Bank B (PWM2)73PWM 3 Data Register 04h: Bank B (PWM3)73 |

| 50<br>59 | PWM 3 Data Register 041. Bank B (PWM3)                                           |

|          | <b>3</b>                                                                         |

| 60<br>61 | PWM 5 Data Register 06h: Bank B (PWM5)                                           |

| 61<br>62 | PWM 6 (6-bit)Data Register 07h: Bank B (PWM6)                                    |

| 62<br>63 | PWM 7 Data Register 001. Bank B (PWM7)                                           |

|          | PWM 8 Data Register 091. Bank B (PWM8)                                           |

| 64<br>65 | PWM 9 Data Register 0An. Bank B (PWM9)                                           |

| 66       | PWM 10 Data Register 0Bh. Bank B (PWM10)                                         |

| 67       | PWM 6 (14-bit) High Data Register 00h: Bank F (PWM6h)                            |

| 68       | PWM 0 (14-bit) Low Data Register 091. Bank P (PWM0L)                             |

| 69       | PWM 11 Low Data Register 01h: Bank B (PWM11L)                                    |

| 70       | 3-Bit ADC Data Register 00h: Bank C (3ADC_DTA)                                   |

| 70       | 4-Bit ADC Data Register 01h: Bank C (SADC_DTA)                                   |

| 72       | Operational Limits                                                               |

| 73       | DC Characteristics                                                               |

| 73<br>74 | AC Characteristics                                                               |

| 74<br>75 | Package Dimensions                                                               |

| 75       | ר מנהמשב שווובווטוטוט 01                                                         |

## **Z90255 ROM and Z90251 OTP 32 KB TV Controller with On-Screen Display**

## 1 Overview

The Z90255 and Z90251 are the ROM and OTP versions of a Television Controller with On-Screen Display (OSD) that contains 32 KB of program memory.

- The **Z90251** is the one-time programmable (OTP) controller used to develop code or prototypes for specific television applications or initial limited production. Program ROM and Character Generation ROM (CGROM) in the Z90251 are both programmable.

- The **Z90255** incorporates the ROM code developed by the customer with the Z90251. Customer code is masked into both program ROM and CGROM.

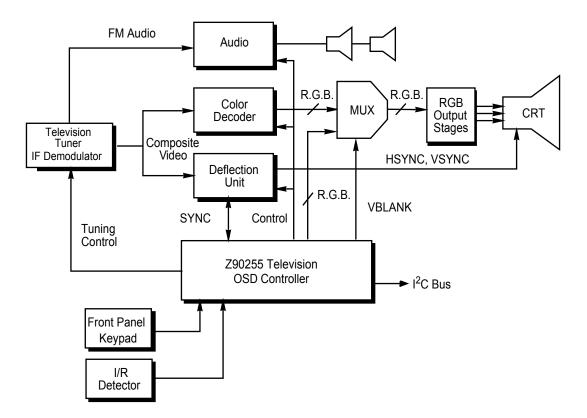

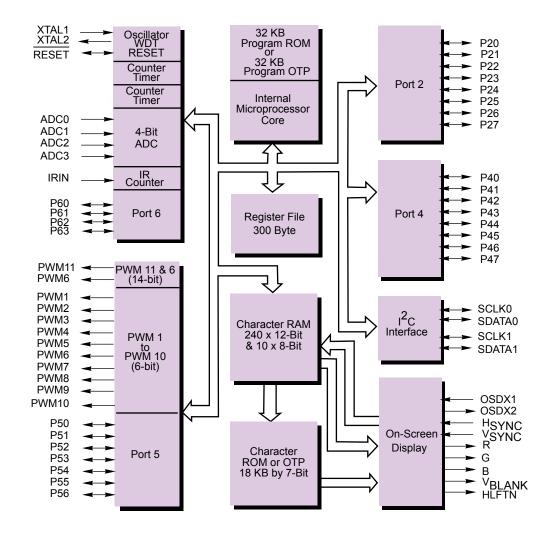

An application-specific controller designed to provide complete audio and video control of television receivers and video recorders, the Z90255 provides advanced OSD features. Figure 1 illustrates a typical TV system application using the Z90255. Figure 2 is a block diagram of the Z90255 architecture.

## Z90255 ROM and Z90251 OTP 32 KB Television Controller with OSD

Figure 1 Z90255-Based TV System Application

#### Z90255 ROM and Z90251 OTP 32 KB Television Controller with OSD

Note: PWM 6 can be either a 6-bit or 14-bit output.

The Z90255 takes full advantage of Zilog's Z8 expanded register file space to offer greater flexibility in creating a user-friendly On-Screen Display (OSD).

Three basic addressing spaces are available: Program memory, Video RAM (VRAM) and the Register file. The register file is composed of 300 bytes of general-purpose registers, 16 control and status registers, one I/O port register and three reserved registers.

The OSD module supports 10 rows by 24 columns of characters. Each character color can be specified. There are eight foreground colors and eight background colors. When the foreground and background colors are the same, the background is transparent.

If Row, Second color and Character set are defined, an analog bar line can be displayed for volume control, signal levels, and tuning.

The OSD can display four character sizes:

- 1X (14 x 18 pixels)

- 2X (28 x 36 pixels)

- Double width (28 x 18 pixels)

- Double height (14 x36 pixels)

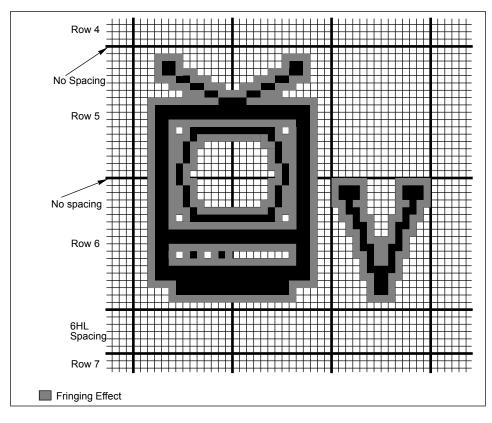

Inter-row spacing can be programmed within 0 to 15 Horizontal scan lines. Using multiple characters with zero inter-row spacing allows the creation of large psuedo icons.

A 14-bit Pulse Width Modulator (PWM) port provides necessary voltage resolution for a voltage synthesizer tuning system. Ten 6-bit PWM ports are used to control audio (base, treble, balance and volume) and video (contrast, brightness, color, tint and sharpness) signal levels.

There are 27 I/O pins grouped into four ports. These I/O pins can be configured through software to provide timing, status signals, serial and parallel input and output.

For real-time events, such as counting, timing and data communication, two onchip counter/timers are implemented. The Z90255 is packaged in a 42-pin SDIP and provides an ideal, reliable solution for high-volume consumer television applications.

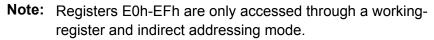

## 1.1 Pin Assignment and Descriptions

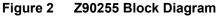

Figure 3 shows the pin numbers for production and OTP device format.

- **Notes:** 1 The pins on the Z90255 and Z90251 are assigned to perform the functions identified in Tables 1, 2 and 3.

- 2 PWM 6 can be either 6-bit or 14-bit PWM outputs.

- 3 All signals with an overbar are active Low.

| Name                    | Pin Function                                                             | Package 42-Pin SDIP              | Direction | POR   |

|-------------------------|--------------------------------------------------------------------------|----------------------------------|-----------|-------|

| V <sub>CC</sub>         | +5 Volts                                                                 | 34                               | Power     | Power |

| GND, AGND               | 0 Volts                                                                  | 30, 13                           | Power     | Power |

| IRIN                    | Infrared Remote Capture Input                                            | 36                               | I         | I     |

| PWM11                   | 14-bit Pulse Width Modulator Output                                      | 1                                | 0         | N/A   |

| PWM10-PWM1 <sup>1</sup> | 6-Bit Pulse Width Modulator Output                                       | 20, 19, 18, 17, 2, 3, 4, 5, 6, 7 | 0         | N/A   |

| P5 (6-0)                | Bit Programmable I/O Ports                                               | 1, 2, 3, 4, 5, 6, 7              | I/O       | I     |

| P2 (7-0)                | Bit-Programmable I/O Ports                                               | 42, 41, 40, 39, 38, 37, 35, 21   | I/O       | I     |

| HLFTN                   | Halftone Output                                                          | 21                               | 0         | N/A   |

| SDATA0, SDATA1          | I <sup>2</sup> C Data, Bidirectional (Send/Receive)<br>Serial Data Lines | 40, 42 <sup>2</sup>              | I/O       | N/A   |

| SCLK0, SCLK1            | I <sup>2</sup> C Clock                                                   | 39, 41 <sup>2</sup>              | I/O       | N/A   |

| P6 (3-0)                | Bit-Programmable I/O Ports                                               | 16, 12, 10, 9                    | I/O       | I     |

| P4 (7-0)                | Bit-Programmable I/O Ports                                               | 20, 19, 18, 17, 15, 14, 11, 8    | I/O       | I     |

| XTAL1                   | Crystal Oscillator Input                                                 | 31                               | I         | I     |

| XTAL2                   | Crystal Oscillator Output                                                | 32                               | 0         | 0     |

| OSDX1                   | Dot-Clock Oscillator Input                                               | 28                               | I         | I     |

| OSDX2                   | Dot-Clock Oscillator Output                                              | 29                               | 0         | 0     |

| H <sub>SYNC</sub>       | Horizontal Synchronization                                               | 26                               | I         | I     |

| V <sub>SYNC</sub>       | Vertical Synchronization                                                 | 27                               | I         | I     |

| VBLANK                  | Video Blanking                                                           | 25                               | 0         | 0     |

| R,G,B                   | Video Red, Green, Blue                                                   | 24, 23, 22                       | 0         | 0     |

| ADC3-ADC0               | 4-Bit Analog-to-Digital Converter Input                                  | 9, 10, 11, 12                    | AI        | I     |

| RESET                   | System Reset                                                             | 33                               | I/O       | I     |

#### Table 1 Z90255 Production Device Pin Assignment

Note: 1 PWM 6 can be either 6-bit or 14-bit PWM outputs.

2 When Pins 39-42 are configured for  $\rm I^2C,$  pins 39 and 40 comprise one channel, and pins 41 and 42 comprise another channel

## 1.2 Single-Purpose Pin Descriptions

Table 2 lists the single-purpose pin acronyms, pin names, and descriptions.

|                   | <b>U</b> .                                 | •                                                                                                                                                                                                                                                                                                                                |

|-------------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Acronym           | Pin Name(s)                                | Description                                                                                                                                                                                                                                                                                                                      |

| AGND              | Analog Ground                              | Analog Ground                                                                                                                                                                                                                                                                                                                    |

| В                 | Blue                                       | CMOS output of the blue video signal B. Video blue can be programmed for either polarity.                                                                                                                                                                                                                                        |

| G                 | Green                                      | CMOS output of the green video signal G. Video green can be programmed for either polarity.                                                                                                                                                                                                                                      |

| GND               | Ground                                     | Ground                                                                                                                                                                                                                                                                                                                           |

| H <sub>SYNC</sub> | Horizontal Sync                            | Input pin for external horizontal synchronization signal                                                                                                                                                                                                                                                                         |

| IRIN              | IR Capture Input                           | Infrared Remote capture input                                                                                                                                                                                                                                                                                                    |

| OSDX1, OSDX2      | On-Screen Display Dot<br>Clock Oscillators | These oscillator input and output pins for on-screen<br>display circuits are connected to an inductor and two<br>capacitors to generate the character dot clock. The dot<br>clock frequency determines the character pixel width and<br>phase synchronized to HSYNC                                                              |

| P21, P22, P23     | Port 2 bits 1 - 3                          | Bidirectional digital port, configured to read digital data or to send output to an attached device.                                                                                                                                                                                                                             |

| P40, P42, P43     | Port 4 bit 0, bits 2 and 3                 | Bidirectional digital port, configured to read digital data or to send output to an attached device.                                                                                                                                                                                                                             |

| P63               | Port 6 bit 3                               | P63 input can be read directly at 03H. A negative edge<br>event is latched to IRQ3. An IRQ3-vectored interrupt<br>occurs if appropriately enabled. A typical application<br>places the device in Stop mode when P63 goes Low<br>(IRQ3 interrupt routine). When P63 subsequently goes<br>High, a Stop-Mode Recovery is initiated. |

| R                 | Red                                        | CMOS output of the red video signal R. Video red can be programmed for either polarity.                                                                                                                                                                                                                                          |

| RESET             | System Reset                               | System reset                                                                                                                                                                                                                                                                                                                     |

|                   |                                            |                                                                                                                                                                                                                                                                                                                                  |

#### Table 2 Single-Purpose Pin Descriptions

| Acronym            | Pin Name(s)                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|--------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| V <sub>BLANK</sub> | Video Blank                   | CMOS output, programmable polarity. This pin is used as<br>a super-impose control port to display characters from<br>video RAM. The signal controls Y-signal output of CRTs<br>and turns off the incoming video display while the<br>characters in video RAM are super-imposed on the<br>screen. The output ports of color data directly drive three<br>electron guns on the CRT; at the same time VBLANK<br>output turns off the Y signal. |  |

| V <sub>CC</sub>    | Power Supply                  | Power supply                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| V <sub>SYNC</sub>  | Vertical Sync                 | Input pin for external vertical synchronization signal.                                                                                                                                                                                                                                                                                                                                                                                     |  |

| XTAL1, XTAL2       | Time-Based<br>Input<br>Output | These pins connect to the internal parallel-resonant clock crystal oscillator circuit with two capacitors to GND. XTAL1 can be used as an external clock input.                                                                                                                                                                                                                                                                             |  |

#### Table 2 Single-Purpose Pin Descriptions (Continued)

## 1.3 Multiplexed Pin Descriptions

Table 3 lists the Multiplexed Pin acronyms, pin names, and descriptions.

#### Table 3 Multiplexed Pin Descriptions

| Acronym                 | Pin Name(s)                                                                     | Description                                                                                                                           |

|-------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| P20/HLFTN               | Port 2 bit 0 or Halftone Output                                                 | Port 2 bit 0 can be programmed as an input or output line.                                                                            |

| P24/SCLK0               | Port 2 bit 4 or I <sup>2</sup> C Clock                                          | Port 2 bit 4 or I <sup>2</sup> C Clock                                                                                                |

| P25/SDATA0              | Port 2 bit 5 or I <sup>2</sup> C Data                                           | Port 2 bit 5 or I <sup>2</sup> C Data                                                                                                 |

| P26/SCLK1<br>P27/SDATA1 | Port 2 bit 6 or I <sup>2</sup> C Clock<br>Port 2 bit 7 or I <sup>2</sup> C Data | Port 2 bit 6 or I <sup>2</sup> C Clock<br>Port 2 bit 7 or I <sup>2</sup> C Data                                                       |

| P62/ADC0                | Port 6 bit 2 or<br>Analog-to-Digital Converter<br>Channel 0                     | P62 can be read directly. A negative edge event is latched into IRQ2 to initiate an IRQ2-vectored interrupt if appropriately enabled. |

| P60/ADC3                | Port 6 bit 0 or<br>Analog-to-Digital Converter<br>Channel 3                     | Port 6 bit 0 can be programmed as an input or output line.                                                                            |

| Acronym   | Pin Name(s)                                                 | Description                                                                                                                             |

|-----------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| P61/ADC2  | Port 6 bit 1 or<br>Analog-to-Digital Converter<br>Channel 2 | Port 6 bit 1 can be programmed as an input or output line.                                                                              |

| P41/ADC1  | Port 4 bit 1 or<br>Analog-to-Digital Converter<br>Channel 1 | Port 4 bit1 can be programmed as an input or output line.                                                                               |

| P44/PWM7  | Port 4 bit 4 or Pulse Width<br>Modulator 7                  | These port pins can be programmed as input or output ports. Each PWM channel has 6-bit resolution.                                      |

| P45/PWM8  | Port 4 bit 5 or Pulse Width<br>Modulator 8                  |                                                                                                                                         |

| P46/PWM9  | Port 4 bit 6 or Pulse Width<br>Modulator 9                  |                                                                                                                                         |

| P47/PWM10 | Port 4 bit 7 or Pulse Width<br>Modulator 10                 |                                                                                                                                         |

| PWM11/P56 | Pulse Width Modulator 11 or<br>Port 5 bit 6                 | The PWM signal-generator channel has 14-bit resolution. Port 5 bit 6 and port 5 bit 5 can be programmed as inputs or outputs.           |

| PWM6/P55  | Pulse Width Modulator 6 or<br>Port 5 bit 5                  |                                                                                                                                         |

| PWM6/P55  | Pulse Width Modulator 6 or<br>Port 5 bit 5                  | These port pins can be programmed as input or output ports. Each PWM signal-generator channel has 6-bit resolution.                     |

| PWM5/P54  | Pulse Width Modulator 5 or<br>Port 5 bit 4                  |                                                                                                                                         |

| PWM4/P53  | Pulse Width Modulator 4 or<br>Port 5 bit 3                  |                                                                                                                                         |

| PWM3/P52  | Pulse Width Modulator 3 or<br>Port 5 bit 2                  |                                                                                                                                         |

| PWM2/P51  | Pulse Width Modulator 2 or<br>Port 5 bit 1                  | The PWM signal-generator channel has 6-bit resolution<br>Port 5 bit 1 and Port 5 bit 0 can be programmed as an<br>input or output port. |

| PWM1/P50  | Pulse Width Modulator 1 or<br>Port 5 bit 0                  | The PWM signal-generator channel has 6-bit resolution<br>Port 5 bit 0 can be programmed as an input or output<br>port.                  |

|           | be either 6-bit or 14-bit output.                           |                                                                                                                                         |

#### Table 3 Multiplexed Pin Descriptions (Continued)

The Z90251 requires Zilog's Z90259ZEM Emulator with its proprietary Zilog Developmental Studio (ZDS) software for programming. To view how code is working, the emulator uses a ZOSD board which connects directly to a television screen. Refer to Figure 4.

Figure 4 Code Development Environment

## 2 Memory Description

A total of 300 bytes of general purpose register memory is implemented in the Z90255. These registers are composed of 236 registers from the standard register file and 64 registers from the expanded register file.

## 2.1 Standard Register File

The Z90255 Standard Register File consists of two I/O port registers (02h and 03h), 236 general purpose registers (04h-EFh) and 15 (F1h-FFh) control and status registers. Registers 00h, 01h, and F0h are reserved. Figure 5 is the register file map. Instructions can access registers directly or indirectly with an 8-bit address field. This also allows short 4-bit addressing using the Register Pointer. In the 4-bit mode, the register file is divided into sixteen working register groups. The upper nibble of the Register Pointer (FDh) addresses the starting location of the active working-register group.

## 2.2 Expanded Register File

The register file has been expanded to provide additional system control registers, additional general purpose registers, and expanded mapping of peripheral devices and I/O ports in the register address area.

The lower nibble of the Register Pointer (FDh) addresses the Expanded Register File (ERF) Bank. The 0h value in the lower nibble identifies the Standard Register File to be addressed. Any other value from 1h to Fh selects an ERF Bank. When an ERF Bank is selected, register addresses from 00h to 0Fh access the sixteen ERF Bank registers, which in effect replace the first sixteen locations of the Z90255 Standard Register File. Only ERF Bank 4, ERF Bank 5, ERF Bank 6, ERF Bank 7, ERF Bank A, ERF Bank B, ERF Bank C and ERF Bank F are implemented in the Z90255 controller (Table 4).

## 2.3 Program Memory

The Z90255 has 32KB of program memory. Refer to Figure 6. The first 12 bytes of the program memory are reserved for the interrupt vectors. These locations contain six 16-bit vectors that correspond to interrupt and program control routine addresses which are passed to the specified vector address. The IRQ0 vector is permanently assigned to the IR interrupt request. The IRQ1 vector is permanently assigned to the V<sub>SYNC</sub> and H<sub>SYNC</sub> interrupt request. Program memory starts at address 000Ch after being reset.

### Z90255 ROM and Z90251 OTP 32 KB Television Controller with OSD

**Reset Condition**

#### D7 D6 D5 D4 D3 D2 D1 D0 Register %FF SPL х х х х х х х х SPH %FE х х х х х х х х %FD RP 0 0 0 0 0 0 0 0 **Register Pointer** %FC FLAGS х х х х х х х х D7 D6 D5 D4 D3 D2 D1 D0 %FB IMR 0 х х х х х х х %FA IRQ 0 0 0 0 0 0 0 0 Working Register Group Pointer Expanded Register **Bank Pointer** IPR %F9 х х х х х х х х %F8 P01M 1 1 1 1 1 1 1 1 %F7 P2CNTL 0 0 0 0 0 0 0 1 %F6 P2M 1 1 1 1 1 1 1 1 %F5 PRE0 0 х х х х х х х %F4 Т0 х х х х х х х х Z8 Register File %F3 PRE1 0 0 х х х х х х %FF %F2 T1 х х х х х х х х %F0 %F1 TMR 0 0 0 0 0 0 0 0 %F0 Reserved Register Bank (F) Expanded Register **Reset Condition** %(F)0F WDTMR 1 х х х х х х х %(F)0E Reserved %(F)0D Reserved %7F %(F)0C Reserved %(F)0B SMR 0 0 1 0 0 0 0 0 %(F)0A Reserved %(F)09 PWM6H 0 0 0 0 0 0 х х %(F)08 PWM6L 0 0 0 0 0 0 0 0 `(C) ́а (В) %(F)07 MC\_Reg 0 0 0 0 0 0 0 0 %0F %(F)06 MR\_En 0 0 0 0 0 0 0 0 (A) (7) %00 %(F)05 MC\_End 0 0 0 0 0 х х х (6) %(F)04 MC\_St 0 0 0 (5) х 0 0 х х (4) %(F)03 PRT6\_DTA 1 1 1 1 1 1 1 1 %(F)02 PRT6\_DRT 1 1 1 1 1 1 1 1 %(F)01 4ADC\_DTA 0 0 0 0 х х х х %(F)00 PCON 1 1 1 1 1 1 0 1 **Reserved Expanded Reset Condition** Register Register %(0)03 Reserved %(0)02 P2 х х х х х х х х x = undefined %(0)01 Reserved

%(0)00

Reserved

#### Figure 5 Register File Map

PS001301-0800

12

#### Table 4 Register File Map

| BANK 4                 | BANK 5                 | BANK 6                 | BANK 7                 |  |

|------------------------|------------------------|------------------------|------------------------|--|

| Address Description    | Address Description    | Address Description    | Address Description    |  |

| 00h-0Fh Gen. Pur. Reg. |  |

| BANK                | BANK A BANK B                                  |         |                                     |  |  |

|---------------------|------------------------------------------------|---------|-------------------------------------|--|--|

| Address Description |                                                |         | Address Description                 |  |  |

| 00h                 | OSD Control Register(OSD_CNTL)                 | 00h     | PWM11-High Data Register(PWM11H)    |  |  |

| 01h                 | Vertical Position Register(VERT_POS)           | 01h     | PWM11-Low Data Register(PWM11L)     |  |  |

| 02h                 | Horizontal Position Register(HOR POS)          | 02h     | PWM1 Data Register(PWM1)            |  |  |

| 03h                 | Display Attribute Register(DISP_ATTR)          | 03h     | PWM2 Data Register(PWM2)            |  |  |

| 04h                 | Row Space Register (ROW_SPACE)                 | 04h     | PWM3 Data Register(PWM3)            |  |  |

| 05h                 | Fade Position1 Register(FADE_POS1)             | 05h     | PWM4 Data Register(PWM4)            |  |  |

| 06h                 | Fade Position2 Regisiter(FADE_POS2)            | 06h     | PWM5 Data Register(PWM5)            |  |  |

| 07h                 | Second Color Control<br>Register(SNDCLR_CNTRL) | 07h     | PWM6(6-bit) Data Register(PWM6_6)   |  |  |

| 08h                 | Second Color Position<br>Register(SNDCLR_POS)  | 08h     | PWM7 Data Register(PWM7)            |  |  |

| 09h                 | Color Palette0 Register(CLR_P0)                | 09h     | PWM8 Data Register(PWM8)            |  |  |

| 0Ah                 | Color Palette1 Register(CLR_P1)                | 0Ah     | PWM9 Data Register(PWM9)            |  |  |

| 0Bh                 | Color Palette2 Register(CLR_P2)                | 0Bh     | PWM10 Data Register(PWM10)          |  |  |

| 0Ch                 | Color Palette3 Register(CLR_P3)                | 0Ch     | Port 5 Data Register(PRT5_DTA)      |  |  |

| 0Dh                 | Color Palette4 Register(CLR_P4)                | 0Dh     | PWM Mode Register(P_MODE)           |  |  |

| 0Eh                 | Color Palette5 Register(CLR_P5)                | 0Eh     | Port 5 Direction Register(PRT5_DRT) |  |  |

| 0Fh                 | Color Palette6 Register(CLR_P6)                | 0Fh     |                                     |  |  |

| BANK                | С                                              | BANK F  |                                     |  |  |

| Address             | Description                                    | Address | Description                         |  |  |

| 00h                 | 3-bit ADC Data Register(3ADC_DTA)              | 00h     | Port Configuration Register(PCON)   |  |  |

| 01h                 | Timer Control Register0(TCR0)                  | 01h     | 4-bit ADC Data Register (4ADC_DTA)  |  |  |

| 02h                 | Timer Control Register1(TCR1)                  | 02h     | Port6 Direction Register(PRT6_DRT)  |  |  |

| 03h                 | IR Capture Register0(IR_CP0)                   | 03h     | Port6 Data Register (PRT6_DTA)      |  |  |

| 04h                 | IR Capture Register1(IR_CP1)                   | 04h     | Mesh Column Start Register(MC_ST)   |  |  |

| 05h                 | Port4 Data Register(PRT4_DTA)                  | 05h     | Mesh Column End Register(MC_END)    |  |  |

| 06h                 | Port4 Direction Register(PRT4_DRT)             | 06h     | Mesh Row Enable Register(MR_EN)     |  |  |

| 07h                 | Interrupt Status Register(INT_ST)              | 07h     | Mesh Control Register(MC_REG)       |  |  |

| 08h                 | Port4 Pin_out Selection Register(PIN_SLT)      | 08h     | PWM6 High Data Register(PWM6H_14)   |  |  |

| 09h                 | Color Index Register(CLR_IDX)                  | 09h     | PWM6 Low Data Register (PWM6L_14)   |  |  |

| 0Ah                 | I2C Data Register(I <sup>2</sup> C_DATA)       | 0Ah     |                                     |  |  |

| 0Bh                 | I2C Command Register(I <sup>2</sup> C_CMD)     | 0Bh     | Stop Mode Register(SMR)             |  |  |

| 0Ch                 | I2C Control Register(I <sup>2</sup> C_CNTL)    | 0Ch     |                                     |  |  |

| 0Dh                 |                                                | 0Dh     |                                     |  |  |

| 0Eh                 |                                                | 0Eh     |                                     |  |  |

| 0Fh                 |                                                | 0Fh     | WDT Mode Register(WDTMR)            |  |  |

Z90255 ROM and Z90251 OTP 32 KB Television Controller with OSD

Figure 6 Program Memory Map

## 3 Watch-Dog Timer (WDT)

The Watch-Dog Timer (WDT) is driven by an internal RC oscillator. Therefore accuracy is dependent on the tolerance of the RC components. Table 5 describes the Watch-Dog Timer Mode register bits.

Table 5 Watch-Dog Timer Mode Register 0Fh: Bank F

| Bit   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|---|---|---|---|---|---|---|

| R/W   | W | W | W | W | W | W | W | W |

| Reset | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 |

Note: R = Read W = Write X = Indeterminate

| Dit      |               |                     |                                                                                                                                                                                                  |

|----------|---------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Position | R/W           | Value               | Description                                                                                                                                                                                      |

| 7-4      | W             | 0                   | Must be 0                                                                                                                                                                                        |

| 3        | W             | 0                   | Off                                                                                                                                                                                              |

|          |               | 1                   | On POR                                                                                                                                                                                           |

| 2        | W             | 0                   | Off                                                                                                                                                                                              |

|          |               | 1                   | On POR                                                                                                                                                                                           |

| 1, 0     | W             | 00                  | 6 msec                                                                                                                                                                                           |

|          |               | 01                  | 12 msec POR                                                                                                                                                                                      |

|          |               | 10                  | 24 msec                                                                                                                                                                                          |

|          |               | 11                  | 96 msec                                                                                                                                                                                          |

| -        | 7-4<br>3<br>2 | PositionR/W7-4W3W2W | Position         R/W         Value           7-4         W         0           3         W         0           2         W         0           1, 0         W         00           01         10 |

#### WDT During Halt Mode (T2)

Bit 2 determines if the WDT is active during Halt Mode. A 1 value indicates active during Halt. The default is 1. A WDT timeout during Halt Mode resets control registers and ports to their default reset conditions.

Bit 3 determines if the WDT is active during Stop mode. A 1 value indicates active during Stop mode. A WDT timeout during Stop mode resets control registers and ports to their default reset conditions.

Bits 4, 5, 6 and 7 are reserved and must be cleared to 0.

The WDTMR register is accessible only during the first 60 processor cycles from the execution of the first instruction after Power-On Reset, Watch-Dog Reset, or a

Stop-Mode Recovery. After this point, the register cannot be modified by any means, intentional or otherwise.

The WDT is permanently enabled after Reset. To ensure that the WDT is set properly, use the following instructions as the first two instructions:

DI WDT

The Watch-Dog timer must then be constantly refreshed within the required timeout by executing the WDT Instruction.

**Note:** Executing the WDT instruction affects the Z (zero), S (sign), and V (overflow) flags.

A system reset overrides all other operating conditions and puts the <u>micro-</u> controller into a known state. To initialize the chip's internal logic, the Reset input must be held Low for at least 5 XTAL clock cycles. The contr<u>ol regi</u>sters and ports are reset to default conditions after a POR, a reset from the Reset pin, or a WDT timeout while in Run Mode and Halt Mode. The control registers and ports are not reset to their default conditions after Stop Mode Recovery and WDT timeout while in Stop Mode.

The program counter is loaded with 000Ch. I/O ports and control registers are configured to their default reset states.

Resetting the microcontroller does not Affect the contents of the general-purpose registers.

The Watch-Dog Timer (WDT) is a retriggerable, one-shot timer that resets the microcontroller if it reaches its terminal count. When operating in th<u>e Run</u>, Halt or Stop Modes, a WDT reset is functionally equivalent to a hardware POR reset.

## 4 Stop Mode and Halt Mode Operation

## 4.1 Power-Down Halt-Mode Operation

The Halt Mode suspends instruction execution and turns off the internal CPU clock. The on-chip oscillator circuit remains active so the internal clock continues to run and is applied to the counter/timer(s) and interrupt logic.

To enter the Halt Mode, the instruction pipeline must be flushed first to avoid suspending execution in mid-instruction. To do this, the application program must

execute a NOP instruction (opcode = FFh) immediately before the Halt instruction (opcode 7Fh), that is,

- FF NOP ;clear the instruction pipeline

- 7F Halt ;enter Halt Mode

The Halt Mode is exited by interrupts, generated either externally or internally. When the interrupt service routine is completed, the user program continues from the instruction after Halt.

The Halt Mode can also be exited via a POR/Reset activation or a Watch-Dog Timer (WDT) timeout. In this case, program execution restarts at the reset-restart address 000Ch.

To reduce power consumption further in the Halt Mode, the Z90255 and Z90251 allow dynamic internal clock scaling. Clock scaling can be accomplished on the fly by reprogramming bit 0 and/or bit 1 of the Stop-Mode Recovery register (SMR).

### 4.2 Stop Mode Operation

•

The Stop Mode provides the lowest possible device standby current. This instruction turns off the on-chip oscillator and internal system clock.

To enter the Stop Mode, the instruction pipeline must be flushed first to avoid suspending execution in mid-instruction. To do this, the application program must execute a NOP instruction (opcode=FFh) immediately before the Stop instruction (opcode=6Fh), that is,

- FF NOP ;clear the instruction pipeline

- 6F Stop ;enter Stop Mode

The Stop Mode is exited by any one of the following resets: Power-On Reset activation, WDT timeout, or a Stop-Mode Recovery source. When reset is generated, the processor always restarts the application program at address 000Ch.

POR/Reset activation is present on the Z90255 and Z90251 and is implemented as a reset pin and/or an on-chip power on reset circuit.

When the WDT is configured to run during Stop mode, the WDT timeout generates a Reset ending Stop Mode.

**Note:** Stop-Mode Recovery (SMR) by the WDT increases the Stop Mode standby current (ICC2). This is because the internal RC oscillator is running to support this recovery mode.

The Z90255 and Z90251 have Stop-Mode Recovery (SMR) circuitry. Two SMR methods are implemented, a single-fixed input pin or a flexible, programmable set of inputs. The Z8-base product specification should be reviewed to determine the SMR options available.

In simple cases, a Low level applied to input pin P27 triggers an SMR. To use this mode, pin P27 (I/O Port 2, bit 7) must be configured as an input before entering Stop Mode. The Low level on P27 must meet a minimum pulse width TWSM. Some microcontrollers provide multiple SMR input sources. The SMR source is selected via the SMR Register.

**Note:** Using specialized SMR modes (P27 input or SMR register based) or the WDT timeout (only when in the Stop Mode) provides a unique reset operation. Some control registers are initialized differently for a SMR/WDT triggered POR than a standard reset operation.

**Note:** The Stop Mode current (ICC2) is minimized when

- $V_{CC}$  is at the low end of the device operating range

- WDT is Off in Stop Mode

- Output current sourcing is minimized

- All inputs (digital and analog) are at the low or high rail voltages

#### 4.3 STOP Mode Recovery Register

5

The STOP Mode Recovery Register register selects the clock divide value and determines the mode of Stop Mode Recovery. All bits are Write-Only, except bit 7 which is Read-Only. Bit 7 is a flag bit that is hardware set in a Stop Mode Recovery condition, and reset by a power-on cycle. Bit 6 controls whether a Low level or a High level is required from the recovery source. Bit 5 controls the reset delay after recovery. Bits 2, 3, and 4, of the SMR register, specify the source of the Stop-Mode Recovery signal. Bits 0 and 1 control internal clock divider circuitry. The SMR is located in bank F of the expanded register file at address 0Bh.

Table 6 contains Stop Mode Recovery (SMR) Register bit descriptions.

| Bit           | 7           | 6             | 5             | 4   |        | 3           | 2        | 1 | 0 |

|---------------|-------------|---------------|---------------|-----|--------|-------------|----------|---|---|

| R/W           | R           | W             | W             | W   |        | W           | W        | W | W |

| Reset         | 0           | 0             | 1             | 0   |        | 0           | 0        | 0 | 0 |

| Note: R = F   | Read W = W  | /rite X = Ind | determinat    | e   |        |             |          |   |   |

| Bit/<br>Field |             |               | it<br>osition | R/W | Value  | e Des       | cription |   |   |

| Stop flag     |             |               | 7             | R   | 0<br>1 | POF<br>Stop | Recovery | , |   |

| Stop Reco     | overv level |               | 6             | W   | 0      | Low         | POR      |   |   |

#### Table 6 Stop Mode Recovery (SMR) Register 0Bh: Bank F (SMR)

| Bit/<br>Field               | Bit<br>Position | R/W | Value                                                | Description                                                                                                         |

|-----------------------------|-----------------|-----|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Stop flag                   | 7               | R   | 0<br>1                                               | POR<br>Stop Recovery                                                                                                |

| Stop Recovery level         | 6               | W   | 0                                                    | Low POR<br>High                                                                                                     |

| Stop Delay                  | 5               | W   | 0<br>1                                               | Off<br>On POR                                                                                                       |

| Stop Mode Recover<br>Source | 4-2             | W   | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | POR and /or External Reset<br>P63<br>P62<br>Must NOT be used<br>Must NOT be used<br>P27<br>P2 NOR 0-3<br>P2 NOR 0-7 |

| External Clock Divide by 2  | 1               | W   | 0<br>1                                               | SCLK/TCLK = XTAL/2 POR<br>SCLK/TCLK = XTAL                                                                          |

| SCLK/TCLK Divide by 16      | 0               | W   | 0<br>1                                               | Off POR<br>On                                                                                                       |

#### SCLK/TCLK Divide-by-16 Select (bit O)

This bit controls a divide-by-16 prescaler of SCLK/TCLK. The purpose of this control is to reduce device power consumption selectively during normal processor execution (SCLK control) and/or Halt Mode (where TCLK sources counter/timers and interrupt logic).

| External Clock Divide-by-Two<br>(bit 1)      | This bit can eliminate the oscillator divide-by-<br>two circuitry. When this bit is 0, the System<br>Clock (SCLK) and Timer Clock (TCLK) are<br>equal to the external clock frequency divided by<br>two. The SCLK/TCLK is equal to the external<br>clock frequency when this bit is set (D1=1).<br>Using this bit together with D7 of PCON helps<br>lower EMI (D7 (PCON) =0, D1 (SMR) =1). The<br>default setting is zero. |

|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Stop-Mode Recovery Source (bits 2, 3, and 4) | These three bits specify the wake-up source of the Stop-Mode recovery.                                                                                                                                                                                                                                                                                                                                                     |

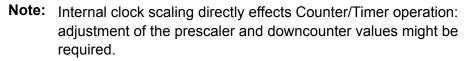

Figure 7 illustrates Stop Mode Recovers Source/Level Select.

|   | Bits |   | Operation                           |

|---|------|---|-------------------------------------|

| 4 | 3    | 2 | Description of Action               |

| 0 | 0    | 0 | POR and/or external reset recovery  |

| 0 | 0    | 1 | P63 transition                      |

| 0 | 1    | 0 | P62 transition (not in Analog Mode) |

| 1 | 0    | 1 | P27 transition                      |

| 1 | 1    | 0 | Logical NOR of P20 through P23      |

| 1 | 1    | 1 | Logical NOR of P20 through P27      |

Table 7

Stop Mode Recovery Source

## Stop Mode Recovery Delay Select (bit 5)

This bit, if High, enables the  $T_{POR}$  Reset delay after Stop Mode Recovery. The default configuration of this bit is 1. If the fast wake up is selected, the Stop Mode Recovery source is kept active for at least 5 TpC.

Stop Mode Recovery Level A 1 in this bit position indicates that a High level on any one of the recovery sources wakes the microcontroller from Stop Mode. A 0 indicates Low-level recovery. The default is 0 on POR.

Cold or Warm Start (bit 7)

This bit is set by the device when Stop Mode is entered. A 0 in this bit (cold) indicates that the device reset by POR/WDT Reset. A 1 in this bit (warm) indicates that the device awakens by a SMR source.

Figure 7 Stop Mode Recovery Source/Level Select

)

**Note:** If P62 is used as an SMR source, the digital mode of operation must be selected before entering Stop Mode.

## 5 On-Screen Display

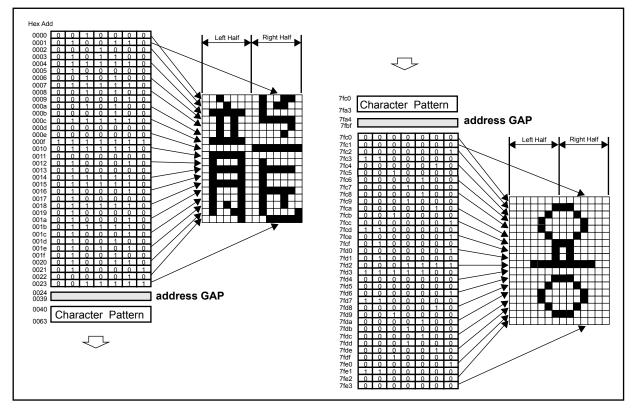

The On-Screen Display (OSD) module generates and displays a 10 row by 24 columns of 512 characters at 14 x 18-dots resolution. The color of each character can be specified independently.

The televison OSD controller uses  $H_{SYNC}$  and  $V_{SYNC}$  signals to synchronize its internal circuitry to the video signal, then outputs RGB and Video Blank (VBLANK) signals. The VBLANK signal is used to multiplex the OSD signal and video signal onto the screen. The result is that the On-Screen Display is superimposed over the TV picture.

The display results from the successful timing of several components:

- OSD Positioning

- Second Color Feature

- Mesh and Halftone Effect

- OSD Fade

- Inter-Row Spacing

- Character Generation

#### 5.1 OSD Position

OSD Positioning is controlled by programming the following registers:

- OSD Control Register (Table 8)

- Vertical Position Register (Table 9)

- Horizontal Position Register (Table 10)

#### **OSD Control Register**

#### Table 8 OSD Control Register 00h:Bank A (OSD\_CNTL)

| Bit              | 7                                          | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|------------------|--------------------------------------------|-----|-----|-----|-----|-----|-----|-----|--|

| R/W              | R/W                                        | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Reset            | 0                                          | x   | x   | x   | x   | x   | х   | х   |  |

| Note: P - Read V | Note: P = Pead W = Write Y = Indeterminate |     |     |     |     |     |     |     |  |

Note: R = Read W = Write X = Indeterminate

| Bit/                      | Bit      |       |       |                           |

|---------------------------|----------|-------|-------|---------------------------|

| Field                     | Position | ו R/W | Value | Description               |

| OSD Blank                 | 7        | R/W   | 0     | Enable OSD - POR default  |

|                           |          |       | 1     | Disable OSD               |

| VRAM Mode                 | 6, 5     | R/W   | 00    | Select 10-row buffer mode |

|                           |          |       | 01    | Reserved                  |

|                           |          |       | 10    | Select 2-row buffer mode  |

|                           |          |       | 11    | Reserved                  |

| Sync Polarity             | 4        | R/W   | 0     | Positive                  |

|                           |          |       | 1     | Negative                  |

| Character Size            | 3        | R/W   | 0     | 1X                        |

|                           |          |       | 1     | 2X                        |

| Vertical Retrace Blanking | 2, 1, 0  | R/W   |       | Retrace Blanking          |

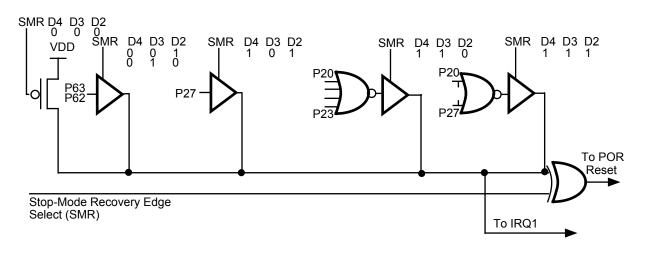

Bit 4, Sync Polarity, provides the polarity of the  $H_{SYNC}$  and  $V_{SYNC}$  signals.  $H_{SYNC}$  and  $V_{SYNC}$  must have the same polarity (see Figure 8). This feature is designed to provide flexibility for TV chassis designers.

Figure 8 Positive and Negative Sync Signals

Bit 3, Character Size, sets the size of the characters that are displayed. Character sizes 1X, 2X, double width and double height are supported. The default value is 1x.

To change the size of the characters in a row, alter the value of the bit during the previous horizontal interrupt. The character size of the first row is programmed during vertical interrupt ( $v_{SYNC}$ ) processing. Character size is a row attribute.

Bits 2, 1, and 0, Vertical Retrace Blanking, set a time period when the OSD is disabled while the electron gun returns from the bottom to the top of the screen, and all VBLANK and RGB output are disabled. The blanking period is determined by counting horizontal pulses according to the following formula:

```

Blanking Period=(4 x (Vertical Retrace Blanking)+2) x THL

```

THL: one horizontal period

The retrace blanking bits,  $OSD\_CNTL$  (2,1,0) must be set to deactivate the electron guns during the retrace period.

#### **Vertical Position Register**

The Vertical Position Register (Table 6) sets the vertical placement of the OSD on the screen. The unit of measure for placement is the number of scan lines from the top of the TV field.

| Bit   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-----|-----|-----|-----|-----|-----|-----|

| R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

#### Table 9 Vertical Position Register 01h:Bank A (VERT\_POS)

Note: R = Read W = Write X = Indeterminate

| Bit/                    | Bit         |     |       |                                                                        |

|-------------------------|-------------|-----|-------|------------------------------------------------------------------------|

| Field                   | Position    | R/W | Value | Description                                                            |

| reserved                | 7           | R   | 0     | Return 0                                                               |

|                         |             | W   | 1     | No effect                                                              |

| Character double height | 6           | R/W | 0     | Normal when bit 3 of OSD_CNTL is 0.<br>2X when bit 3 of OSD_CNTL is 1. |

|                         |             |     | 1     | Double height when bit 3 of OSD_CNTL is 0.                             |

|                         |             |     |       | Double width when bit 3 of OSD_CNTL is 1.                              |

| Vertical Position       | 5,4,3,2,1,0 | R/W |       | Vertical position control                                              |

The value required for this register can be computed using the following equation:

$VERT\_POS = (V_{POS} - 6) / 4$

VERT\_POS represents the contents of bits 5,4,3,2,1,0 of the Vertical Position Register (VERT\_POS). The default value is 0. When the value is 0, the OSD is at the top-most OSD position on the screen, with an offset of 06h scan lines above the OSD area.

<code>VERT\_POS</code> is the number of scan lines from the V<sub>SYNC</sub> to the OSD start position. V<sub>POS</sub> must be a positive integer with a minimum value of Ah incrementing by 4.

#### **Horizontal Position Register**

The Horizontal Position Register sets the horizontal start position of the OSD (Table 7). The unit of measure for placement is the number of pixels from the left of the display screen.

| Bit   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-----|-----|-----|-----|-----|-----|-----|

| R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0   | 1   | 0   | 0   | 0   | 0   | 1   | 1   |

#### Table 10 Horizontal Position Register 02h:Bank A (HOR\_POS)

Note: R = Read W = Write X = Indeterminate

| Register Field      | Bit Position | R/W    | Data   | Description                               |

|---------------------|--------------|--------|--------|-------------------------------------------|

| Progressive mode    | 7            | R/W    | 0<br>1 | Normal<br>Support progressive sync inputs |

| Reserved            | -6           | R<br>W |        | Return 1<br>No effect                     |

| Horizontal position | 5,4,3,2,1,0  | R/W    |        | Horizontal position control               |

When working with Progressive mode, fringing does not work with 2X mode or double height mode, nor does Mesh work the same way as in Interlace mode.

The value required for this register can be computed using the following equation:

$HOR\_POS = (H_{POS} - 1) / 4$

HOR\_POS represents the contents of bits 5,4,3,2,1,0 of the Horizontal Position Register (HOR\_POS). The default value is 3h. When the value is 3h, the OSD is at the left-most OSD position on the screen.

$H_{POS}$  is the number of pixels from the left of the screen to the OSD start position.  $H_{POS}$  must be a positive integer with a minimum value of 5 incrementing by 4.

### 5.2 Second Color Feature

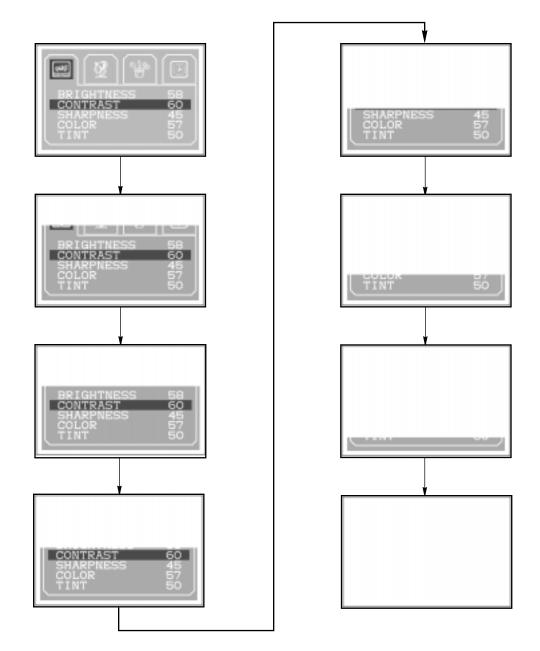

Second Color feature is the logical division of each column into two parts along each row for changing foreground color. The number of each half-column is called the Second Color Position.

The Second Color feature can be used to implement an analog bar for volume control, tuning, etc. The change step for color is half the character size. Refer to Tables 8 and 9.

#### **Second Color Control Register**

The Second Color Position is the place where the foreground color changes to the color defined in the Second Color Control Register.

| Table 11 | Second Color Co | trol Register 07h:Bank | A (SNDCLR_CNTRL) |

|----------|-----------------|------------------------|------------------|

|----------|-----------------|------------------------|------------------|

| Bit   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-----|-----|-----|-----|-----|-----|-----|

| R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

Note: R = Read W = Write X = Indeterminate

| Bit/<br>Field       | Bit<br>Position | R/W | Value  | Description                                                                                                |

|---------------------|-----------------|-----|--------|------------------------------------------------------------------------------------------------------------|

| Second Color Enable | 7               | R/W | 0<br>1 | Disables the second color feature<br>Enables the second color feature                                      |

| Second Color        | 6, 5, 4         | R/W |        | R, G, B respectively. Defines the second color after the second color position defined in SNDCLR register. |

| Row Address         | 3, 2, 1, 0      | R/W |        | Defines one of the 10 rows (from 0, the first row, to 9, the 10th row).                                    |

#### **Second Color Register**

Table 12 Second Color Register 08h:Bank A (SNDCLR)

| Bit                                        | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| R/W                                        | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset                                      | х   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| Note: R = Read W = Write X = Indeterminate |     |     |     |     |     |     |     |     |

| Bit/<br>Field                       | Bit<br>Position | R/W | Value | Description                                                       |

|-------------------------------------|-----------------|-----|-------|-------------------------------------------------------------------|

| Reserved                            | 7               | R   | 0     | Return 1                                                          |

|                                     |                 | W   | 1     | No effect                                                         |

| HV <sub>SYNC</sub> Interrupt Option | 6               | R/W | 0     | Interrupt Pending Disabled                                        |

|                                     |                 |     | 1     | Interrupt Pending Enabled                                         |

| Second Color Position               | 5,4,3,2,1,0     | R/W |       | Specifies start position of the color change to the second color. |

**Note:** Column increment is 0.5. Offset is 03h. System software requires that the offset be added to the increment for the second color in the bar display. The bar position must be defined before the second color is enabled.

Bit 6,  $HV_{SYNC}$  Interrupt Option, defines the procedure for processing when a second interrupt is issued before the first interrupt has completed processing. If bit 6 is set to 0, bit 6 is not pending the other interrupt ( $H_{SYNC}$  or  $V_{SYNC}$ ) while one is in service. If bit 6 is set to 1, bit 6 is pending the other interrupt ( $H_{SYNC}$  or  $V_{SYNC}$ ) while one is in service.

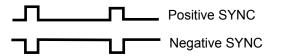

Figures 9 is an example of second color display in the eighth row of the OSD. Each of the small grid squares represents one pixel. Each column has two areas for second color display. In this example, the second color is at Position 6. The second color position for the first column has a value of 3 because the OSD is offset from the left of the TV screen at a distance equal to 03h. Each column is the size of one display character. Each Second color column is a half character column. The screen position offset is added to Second color position. Because the offset is 0.3h, the Second color positions begin with 3 = (3+0), 4 = (3+1), 5 = (4+1), and so forth.

Z90255 ROM and Z90251 OTP 32 KB Television Controller with OSD

Figure 9 Second Color Display

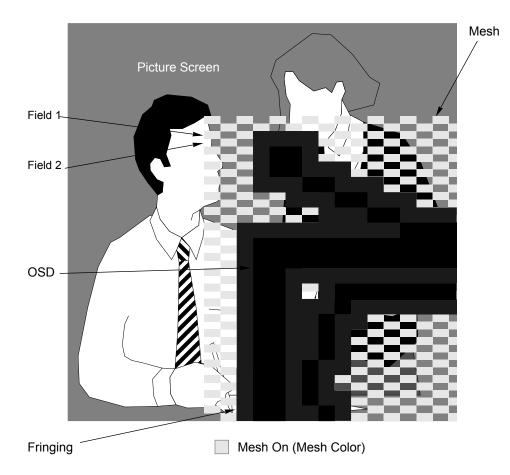

## 5.3 Mesh and Halftone Effect

Mesh is a grid-like area that contains an alternating pixel display of OSD and transparent zones. See Figure 10. The transparent zones allow the TV signal display to appear in part while the mesh display is active.

Halftone effect is a transparent area that appears slightly darker than the regular picture carried by the TV signal.

Mesh and halftone effects both serve as backgrounds for menus, action bars, and other On-Screen Displays. The mesh feature is only for interlaced-mode video systems.

Mesh can be controlled in two ways: through hardware or through software for alternating pixel display in different fields.

Z90255 ROM and Z90251 OTP 32 KB Television Controller with OSD

#### Figure 10 Mesh On

General descriptions of the registers used to control the mesh are contained in Tables 13 through 16.

| Table 13 | Mesh Column | Start Register 04h: | Bank F (MC_St) |

|----------|-------------|---------------------|----------------|

|----------|-------------|---------------------|----------------|

| Bit   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-----|-----|-----|-----|-----|-----|-----|

| R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | х   | х   | х   | 0   | 0   | 0   | 0   | 0   |

| Bit/<br>Field     | Bit<br>Position | R/W    | Value | Description                                            |

|-------------------|-----------------|--------|-------|--------------------------------------------------------|

| Reserved          | 7, 6, 5         | R<br>W |       | Return 1<br>No effect                                  |