# Z80230/Z85230/L

# **Enhanced Serial Communications Controller**

**Product Specification**

PS005309-0515

Warning:

DO NOT USE IN LIFE SUPPORT

#### LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

#### As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

#### **Document Disclaimer**

©2015 by Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

Z8 is a registered trademark of Zilog, Inc. All other product or service names are the property of their respective owners.

# **Revision History**

Each instance in Revision History reflects a change to this document from its previous revision. For more details, refer to the corresponding pages and appropriate links in the table below.

| Date           | Revision<br>Level |                                                               |                                  |  |  |

|----------------|-------------------|---------------------------------------------------------------|----------------------------------|--|--|

| May 2015       | 09                | Minor update to page 36 Minor update to Copywrite Information | 36                               |  |  |

| June 2009      | 08                | Removed Security Watermark from pages                         | all                              |  |  |

| May 2009       | 07                | Minor update to page 107                                      | 107                              |  |  |

| May 2009       | 06                | system update change only - no technical content revised      | n/a                              |  |  |

| Mar 2009       | 05                | Updated document to add 3V product information                | Misc                             |  |  |

|                |                   | Removed ISO/BSI certification information                     | ii                               |  |  |

|                |                   | Figure 1, 7 and 23 changed 5V to Vcc                          | <u>2</u> , <u>13</u> , <u>76</u> |  |  |

|                |                   | Added Z8523L DC Characteristics                               | <u>78</u>                        |  |  |

|                |                   | Updated Read and Write AC Characteristics                     | <u>90</u>                        |  |  |

|                |                   | Updated System Timing Characteristics                         | <u>98</u>                        |  |  |

|                |                   | Updated General Timing Diagram                                | <u>94</u>                        |  |  |

|                |                   | Ordering Information updated                                  | <u>107</u>                       |  |  |

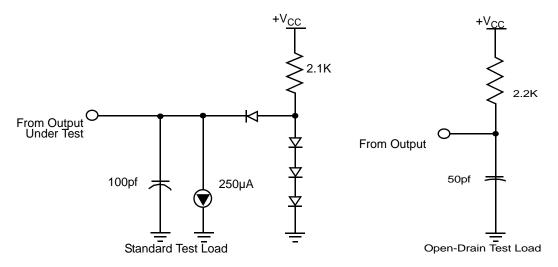

|                |                   | Updated Standard Test Conditions                              | <u>75</u>                        |  |  |

|                |                   | Updatred Table 43                                             | <del>78</del>                    |  |  |

|                |                   | Updated Table 49 - min value                                  | <u>98</u>                        |  |  |

| June 2008      | 04                | Updated as per new template and Style Guide.                  | All                              |  |  |

|                |                   | Updated Figure 4.                                             | 3                                |  |  |

| September 2007 | 03                | Updated Figure 38 and Implemented Style Guide                 | All                              |  |  |

| November 2002  | 02                | Editorial Updates                                             | All                              |  |  |

| August 2001    | 01                | Original Issue                                                | All                              |  |  |

PS005309-0515 Revision History

# **Table of Contents**

| Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | İİİ                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| Table of Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | iν                                                             |

| Pin Descriptions  Pins Common to Both Z85230/L and Z80230  Pin Descriptions Exclusive to the Z85230/L  Pin Descriptions Exclusive to the Z80230                                                                                                                                                                                                                                                                                                                                                                     | 4                                                              |

| Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9                                                              |

| Z80230/Z85230/L Enhancements4-Byte Transmit FIFO Buffer8-Byte Receive FIFOWrite Register 7 PRIME (WR7')CRC Reception in SDLC ModeTxD Forced High in SDLC with NRZI Encoding When Marking IdleImproved Transmit Interrupt HandlingDPLL Counter Tx Clock SourceRead Register 0 Status Latched During Read CycleSoftware Interrupt AcknowledgeFast SDLC Transmit Data Interrupt ResponseSDLC FIFO Frame Status EnhancementFIFO Enable/DisableFIFO Read OperationFIFO Write OperationSDLC Status FIFO Anti-Lock Feature | 22<br>23<br>26<br>26<br>27<br>27<br>28<br>28<br>30<br>30<br>31 |

| Programming Initializing Write Registers Read Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 32<br>32<br>53                                                 |

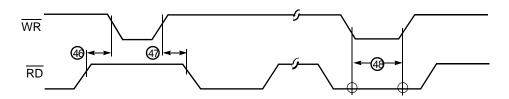

| Z80230 Interface Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 70<br>71<br>71<br>72                                           |

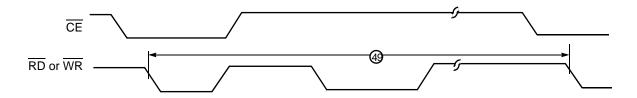

| Z85230/L Read Cycle Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 73                                                             |

PS005309-0515 Table of Contents

# Z80230/Z85230/L Product Specification

| Z85230/L Write Cycle Timing                   | . 73 |

|-----------------------------------------------|------|

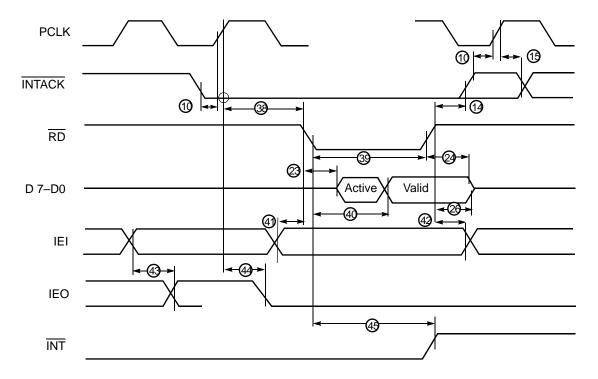

| Z85230/L Interrupt Acknowledge Cycle Timing   | . 74 |

| Electrical Characteristics                    | . 75 |

| Absolute Maximum Ratings                      | . 75 |

| Standard Test Conditions                      | . 75 |

| Capacitance                                   | . 76 |

| Miscellaneous                                 | . 76 |

| DC Characteristics                            | . 77 |

| AC Characteristics                            | . 78 |

| Z85230/L AC Characteristics                   | . 87 |

| Z80230/Z85230/L Errata                        | 99   |

| IUS Problem Description                       |      |

| IUS Problem Solutions                         |      |

| RTS Problem Description                       | 101  |

| RTS Problem Solutions                         | 102  |

| Automatic TxD Forced High Problem Description | 102  |

| Automatic TxD Forced High Problem Solutions   | 103  |

| SDLC FIFO Overflow Problem Description        | 103  |

| SDLC FIFO Overflow Problem Solution           | 103  |

| Default RR0 Value Problem Description         | 103  |

| Default RR0 Value Problem Solution            | 103  |

| Default RR10 Value Problem Description        |      |

| Default RR10 Value Problem Solution           |      |

| CRC Problem Description                       | 104  |

| CRC Problem Solution                          | 104  |

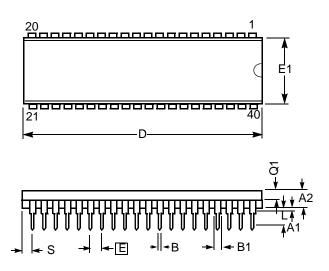

| Package Information                           | 105  |

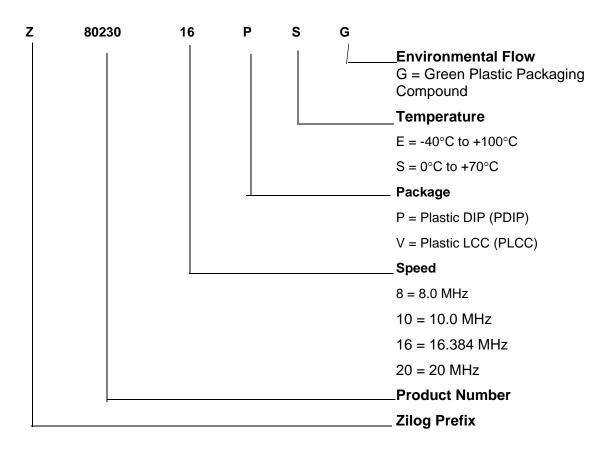

| Ordering Information                          | 107  |

| Z8523L (3.3V)                                 | 107  |

| Z85230 (5V)                                   | 107  |

| Part Number Suffix Designation                | 108  |

| Customer Support                              | 112  |

| Index                                         | 108  |

PS005309-0515 Table of Contents

# **Pin Descriptions**

The Enhanced Serial Communication Controller (ESCC) pins are divided into seven functional groups:

- 1. Address/Data

- 2. Bus Timing and Reset

- 3. Device Control

- 4. Interrupt

- 5. Serial Data (both channels)

- 6. Peripheral Control (both channels)

- 7. Clocks (both channels)

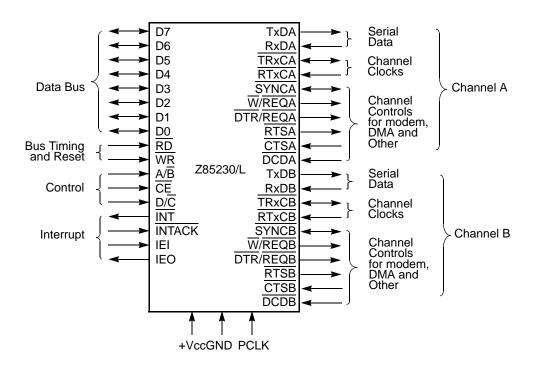

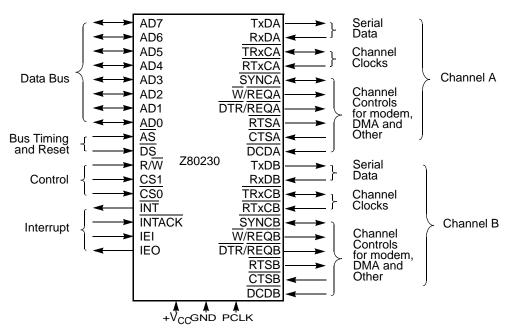

Figure 1 on page 2 and Figure 2 on page 2 display the pins in each functional group for both the Z80230 and Z85230/L. The pin functions are unique to each bus interface version in the Address/Data group, Bus Timing and Reset group, and Device Control group.

The Address/Data group consists of the bidirectional lines used to transfer data between the CPU and the ESCC (addresses in the Z80230 are latched by  $\overline{AS}$ ). The direction of these lines depends on whether the operation is a Read or a Write operation.

The Timing and Control groups designate the type of transaction to occur and the timing of the occurrence. The interrupt group provides inputs and outputs for handling and prioritizing interrupts. The remaining groups are divided into Channel A and Channel B groups for:

- Serial Data (Transmit or Receive)

- Peripheral Control (such as DMA or modem)

- Input and Output Line for the Receive and Transmit Clocks

Figure 1. Z85230/L Pin Functions

Figure 2. Z80230 Pin Functions

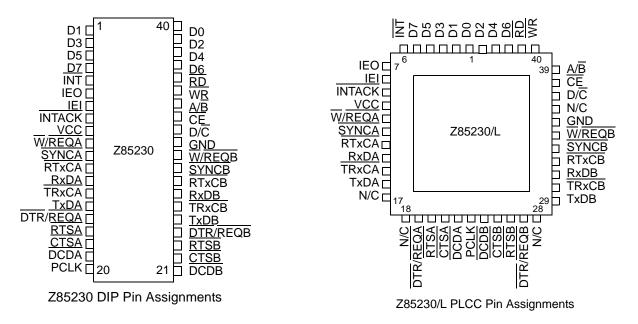

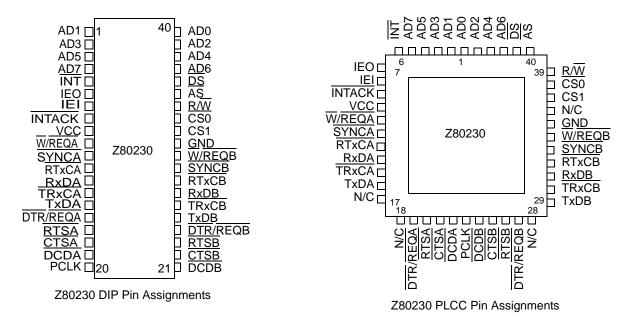

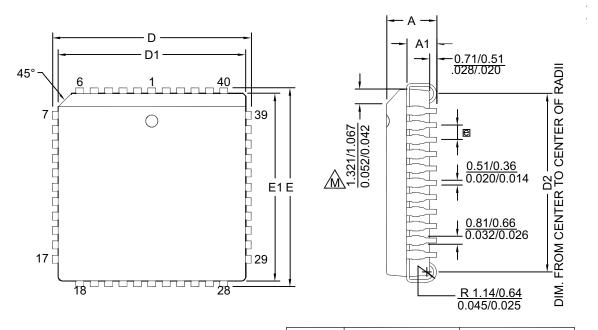

Figure 3 displays the Z85230/L DIP and PLCC pin assignments, respectively. Figure 4 displays the Z80230 DIP and PLCC pin assignments.

Figure 3. Z85230/L Pin Assignments

Figure 4. Z80230 Pin Assignments

## Pins Common to Both Z85230/L and Z80230

The pin descriptions for pins common to both Z85230/L and Z80230 are provided below:

CTSA, CTSB (Clear To Send (Inputs, Active Low))—These pins function as transmitter enables if they are programmed for AUTO ENABLE (WR3 bit 5 is 1), in which case a Low on each input enables the respective transmitter. If not programmed as AUTO ENABLE, the pins may be used as general-purpose inputs. These pins are Schmitt-trigger buffered to accommodate slow rise-time inputs. The ESCC detects pulses on these pins and may interrupt the CPU on both logic level transitions.

DCDA, DCDB (Data Carrier Detect (Inputs, Active Low))—These pins function as receiver enables if they are programmed for AUTO ENABLE (WR3 bit 5 is 1); otherwise, they are used as general-purpose input pins. The pins are Schmitt-trigger buffered to accommodate slow rise-time signals. The ESCC detects pulses on these pins and may interrupt the CPU on both logic level transitions.

RTSA, RTSB (Request To Send (Outputs, Active Low))—The RTS pins can be used as general-purpose outputs or with the AUTO ENABLE feature. When AUTO-ENABLE is off, these pins follow the inverse state of WR5 bit 1. When used with the AUTO-ENABLE feature in ASYNCHRONOUS mode, this pin immediately goes Low when WR5 bit 1 is 1. When WR5 bit 0 is 0, this pin remains Low until the transmitter is empty.

In Synchronous Data Link Control (SDLC) mode, the  $\overline{RTS}$  pins can be programmed to be deasserted when the closing flag of the message clears the TxD pin, if WR7' bit 2 is 1, WR10 bit 2 is 0, and WR5 bit 1 is 0.

SYNCA, SYNCB (Synchronization (Inputs Or Outputs, Active Low))—These pins can act either as inputs, outputs, or as part of the crystal oscillator circuit. In the ASYNCHRONOUS RECEIVE mode (crystal oscillator option not selected), these pins are inputs similar to  $\overline{\text{CTS}}$  and  $\overline{\text{DCD}}$ . In this mode, transition on these lines affect the state of the SYNC/HUNT status bits in Read Register 0 but have no other function.

In EXTERNAL SYNCHRONIZATION mode, with the crystal oscillator not selected, these lines also act as inputs. In this mode,  $\overline{SYNC}$  is driven Low, two Rx clock cycles after the last bit of the  $\overline{SYNC}$  character is received. Character assembly begins on the rising edge of the receive clock immediately preceding the activation of  $\overline{SYNC}$ .

In the INTERNAL SYNCHRONIZATION mode (MONOSYNC and BISYNC) with the crystal oscillator not selected, these pins act as outputs. These outputs go Low each time a SYNC pattern is recognized, regardless of character boundaries. In SDLC mode, pins switch from input to output when MONOSYNC, BISYNC, or SDLC is programmed in WR4 and SYNC modes are enabled.

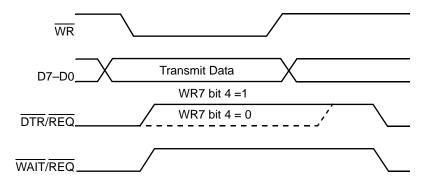

#### DTR/REQA, DTR/REQB (Data Terminal Ready/Request (Output, Active Low))—

These pins can be programmed (WR14 bit 2) to serve either as general-purpose outputs or as DMA Request lines. When programmed for DTR function (WR14 bit 2 is 0), these outputs follow the inverse of the DTR bit of Write Register 5 (WR5 bit 7). When programmed for REQUEST mode these pins serve as DMA Requests for the transmitter.

When used as DMA Request line (WR14 bit 2 is 1), the timing for the deactivation request can be programmed in Write Register 7' (WR7') bit 4. If this bit is 1, the  $\overline{DTR}/\overline{REQ}$  pin is deactivated with the same timing as the  $\overline{W}/\overline{REQ}$  pin. If 0, the deactivation timing of  $\overline{DTR}/\overline{REQ}$  pin is four clock cycles, the same as in the Z80C30/Z85C30.

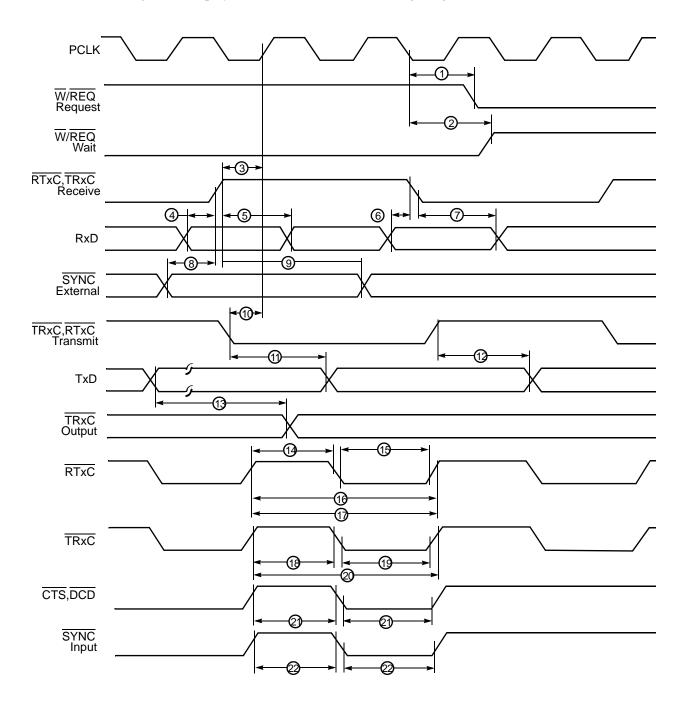

W/REQA, W/REQB (Wait/request (Output, Open-drain When Programmed For WAIT Function, Driven High And Low When Programmed For Request Function))—These dual-purpose outputs may be programmed as REQUEST lines for a DMA controller or as WAIT lines to synchronize the CPU to the ESCC data rate. The reset state is WAIT.

**RxDA**, **RxDB** (Receive Data (inputs, active High))—These inputs receive serial data at standard Transistor-Transistor Logic (TTL) levels.

RTxCA, RTxCB (Receive/Transmit Clocks (Input, Active Low))—These pins can be programmed to several modes of operation. In each channel, RTxC may supply the following:

- Receive clock and/or the transmit clock

- Clock for the baud rate generator (BRG)

- Clock for the Digital Phase-Locked Loop

These pins can also be programmed for use with the respective SYNC pins as a crystal oscillator. The receive clock may be 1, 16, 32, or 64 times the data rate in ASYNCHRONOUS modes.

TxDA, TxDB (Transmit Data (Output, Active High))—These output transmit serial data at standard TTL levels.

TRxCA, TRxCB (Transmit/Receive Clocks (Input or Output, Active Low))—These pins can be programmed in several different modes. When configured as an input, the TRxC may supply the receive clock and/or the transmit clock. When configured as an output, TRxC can echo the clock output of the Digital Phase-Locked Loop, the crystal oscillator, the BRG or the transmit clock.

**PCLK (Clock (Input))**—This clock is the master ESCC clock used to synchronize internal signals. PCLK is a TTL level signal. PCLK is not required to have any phase relationship with the master system clock.

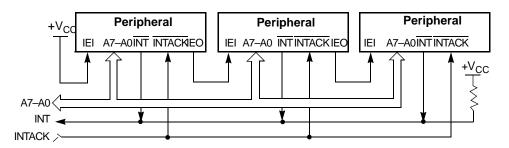

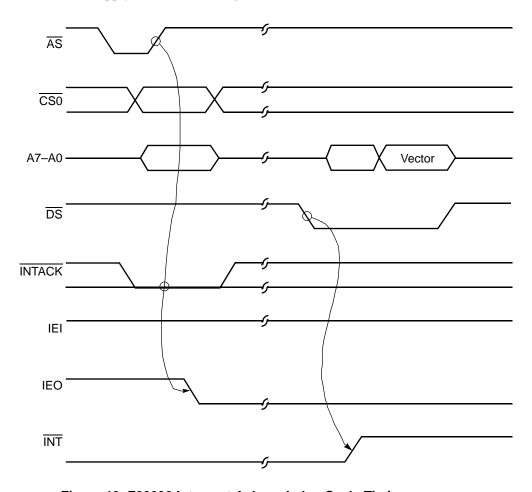

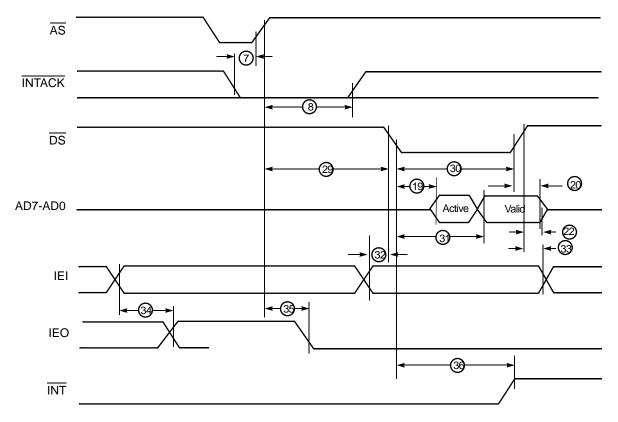

**IEI** (Interrupt Enable In (Input, Active High))—IEI is used with IEO to form an interrupt daisy chain when there is more than one interrupt-driven device. A High IEI indicates that no higher priority device has an Interrupt Under Service (IUS) or is requesting an interrupt.

**IEO** (Interrupt Enable Out (Output, Active High))—IEO is High only if IEI is High and the CPU is not servicing an ESCC interrupt. During an Interrupt Acknowledge Cycle, IEO is also driven Low if the ESCC is requesting an interrupt. IEO can be connected to the next lower priority device's IEI input, and in this case inhibits interrupts from lower priority devices.

**INT** (Interrupt (Output, Open-Drain, Active Low))—This pin activates when the ESCC requests an interrupt. The  $\overline{\text{INT}}$  is an open-drain output.

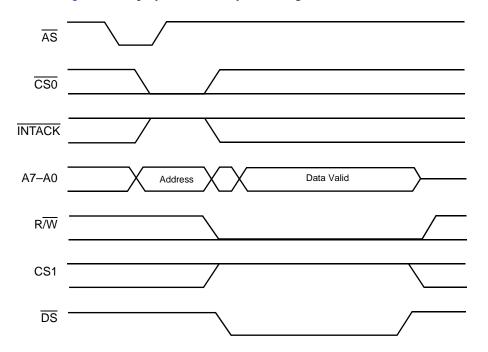

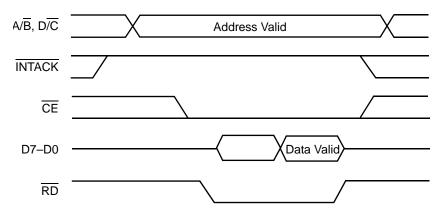

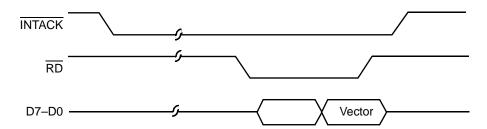

INTACK (Interrupt Acknowledge (Input, Active Low))—This pin is a strobe which indicates that an Interrupt Acknowledge Cycle is in progress. During this cycle, the ESCC interrupt daisy chain is resolved. The device can return an interrupt vector that may be encoded with the type of interrupt pending. During the acknowledge cycle, if IEI is High, the ESCC places the interrupt vector on the data bus when  $\overline{\text{RD}}$  goes active for the Z85230/L, or when  $\overline{\text{DS}}$  goes active for the Z80230.  $\overline{\text{INTACK}}$  is latched by the rising edge of PCLK.

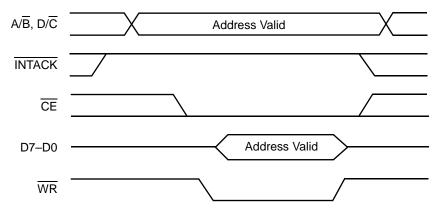

# Pin Descriptions Exclusive to the Z85230/L

The pin description for pins exclusive to Z85230/L is provided below:

**Pins D7–D0 (Data Bus (Bidirectional, tristate))**—These pins carry data and commands to and from the Z85230/L.

**CE** (Chip Enable (Input, Active Low))—This pin selects the Z85230/L for a Read or Write operation.

**RD** ((Read (input, Active Low))—This pin indicates a Read operation and, when the Z85230/L is selected, enables the Z85230/L's bus drivers. During the Interrupt Acknowledge cycle,  $\overline{\text{RD}}$  gates the interrupt vector onto the bus if the Z85230/L is the highest priority device requesting an interrupt.

**WR (Write (Input, Active Low))**—When the Z85230/L is selected, this pin denotes a Write operation, which indicates that the CPU writes command bytes or data to the Z85230/L write registers.

**Note:**  $\overline{WR}$  and  $\overline{RD}$  going Low simultaneously is interpreted as a Reset.

A/B (Channel A/Channel B (Input))—This pin selects the channel in which the Read or Write operation occurs. A High selects Channel A and a Low selects Channel B.

**D/C (Data/Control Select (Input))**—This signal defines the type of information transferred to or from the Z85230/L. A High indicates data transfer and a Low indicates a command transfer.

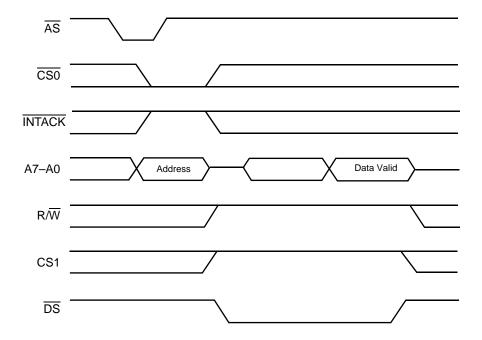

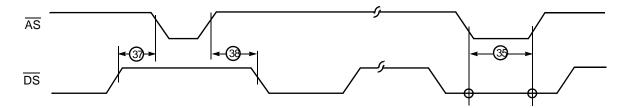

# Pin Descriptions Exclusive to the Z80230

The pin description for pins exclusive to Z80230 is provided below:

**AD7–AD0 (Address/Data Bus (Bidirectional, Active High, tristate))**—These multiplexed lines carry register addresses to the Z80230 as well as data or control information to and from the Z80230.

R/W (Read/Write (Input, Read Active High))—This pin specifies if the operation to be performed is a Read or Write operation.

**CS0 (Chip Select 0 (Input, Active Low))**—This pin is latched concurrently with the addresses on A7-A0 and must be Low for the intended bus transaction to occur.

**CS1 (Chip Select 1 (Input, Active High))**—This second chip select pin must be High before and during the intended bus transaction.

**DS (Data Strobe (Input, Active Low))**—This pin provides timing for the transfer of data into and out of the Z80230. If  $\overline{AS}$  and  $\overline{DS}$  are both Low, this condition is interpreted as a RESET.

AS (Address Strobe (Input, Active Low))—Addresses on A7-A0 are latched by the rising edge of this signal.

# **Functional Description**

The architecture of the ESCC is described based on its functionality as a:

- Data communications device, which transmits and receives data in a wide variety of protocols

- Microprocessor peripheral, in which the ESCC offers valuable features such as vectored interrupts and DMA support

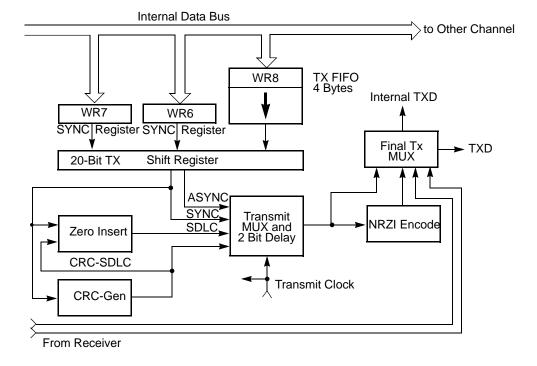

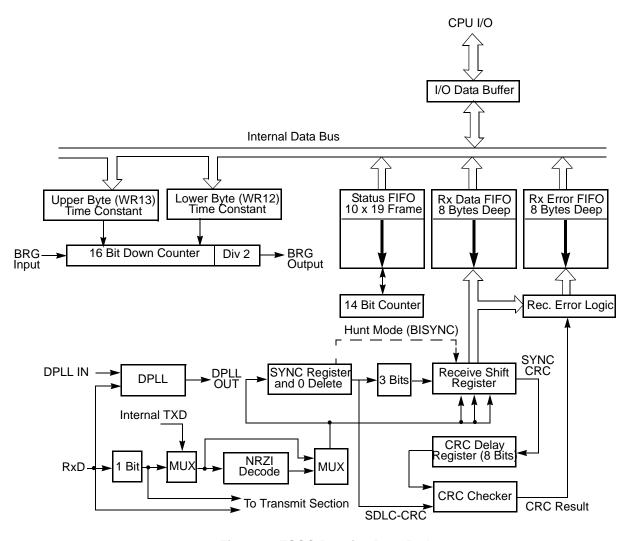

The details of the communication between the receive and transmit logic of the system bus are displayed in Figure 5 and Figure 6 on page 9. The features and data path for each of the ESCC A and B channels are identical. For more information on SCC/ESCC and ISCC Family of Products, refer to the respective User Manuals available for download from <a href="https://www.zilog.com">www.zilog.com</a>.

Figure 5. ESCC Transmit Data Path

Figure 6. ESCC Receive Data Path

# **Input/Output Capabilities**

System communication to and from the ESCC is accomplished using the ESCC register set. There are 17 Write registers and 16 Read registers. Many of the features on the ESCC are enabled through a new register in the ESCC: Write Register 7 Prime (WR7'). This new register can be accessed if bit 0 or WR15 is set to 1. Table 1 on page 10 lists the Write registers and a brief description of their functions. Table 2 on page 11 lists the Read Registers.

Note:

Throughout this document the Write and Read registers are referenced with the notations WR for Write Register and RR for Read Register. For example:

WR4A – Write Register 4 for Channel A

RR3 – Read Register 3 for either or both channels

**Table 1. ESCC Write Registers**

| Write Register | Functions                                                                                                                  |  |  |  |  |  |

|----------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| WR0            | Command Register; Select Shift Left/Right Mode, Cyclic Redundancy Check (CRC) Initialization, and Resets for Various Modes |  |  |  |  |  |

| WR1            | Interrupt Conditions, Wait/DMA Request Control                                                                             |  |  |  |  |  |

| WR2            | Interrupt Vector, Accessed Through Either Channel                                                                          |  |  |  |  |  |

| WR3            | Receive and Miscellaneous Control Parameters                                                                               |  |  |  |  |  |

| WR4            | Transmit and Receive Parameters and Modes                                                                                  |  |  |  |  |  |

| WR5            | Transmit Parameters and Controls                                                                                           |  |  |  |  |  |

| WR6            | SYNC Character or SDLC Address Field                                                                                       |  |  |  |  |  |

| WR7            | SYNC Character or SDLC Flag                                                                                                |  |  |  |  |  |

| WR7'           | SDLC Enhancements Enable, Accessible if WR15 bit D0 is 1                                                                   |  |  |  |  |  |

| WR8            | Transmit FIFO, 4-Bytes Deep                                                                                                |  |  |  |  |  |

| WR9            | Reset Commands and Master INT Enable, Accessible Through Either Channel                                                    |  |  |  |  |  |

| WR10           | Miscellaneous Transmit and Receive Controls                                                                                |  |  |  |  |  |

| WR11           | Clock Mode Control                                                                                                         |  |  |  |  |  |

| WR12           | Lower Byte of BRG Time Constant                                                                                            |  |  |  |  |  |

| WR13           | Upper Byte of BRG Time Constant                                                                                            |  |  |  |  |  |

| WR14           | Miscellaneous Controls and Digital Phase-Locked Loop (DPLL) Commands                                                       |  |  |  |  |  |

| WR15           | External Interrupt Control                                                                                                 |  |  |  |  |  |

**Table 2. ESCC Read Registers**

| Register Name | Functions                                                                  |  |  |  |  |

|---------------|----------------------------------------------------------------------------|--|--|--|--|

| RR0           | Transmit, Receive, and External Status                                     |  |  |  |  |

| RR1           | Special Receive Condition Status Bits                                      |  |  |  |  |

| RR2A          | Unmodified Interrupt Vector                                                |  |  |  |  |

| RR2B          | Modified Interrupt Vector                                                  |  |  |  |  |

| RR3A          | Interrupt Pending Bits                                                     |  |  |  |  |

| RR4           | WR4 Mirror, if WR7' bit D6 equals 1                                        |  |  |  |  |

| RR5           | WR5 Mirror, if WR7' bit D6 equals 1                                        |  |  |  |  |

| RR6           | SDLC Frame LSB Byte Count, if WR15 bit D2 equals 1                         |  |  |  |  |

| RR7           | SDLC Frame 10 X 19 FIFO Status and MSB Byte Count, if WR15 bit DS equals 1 |  |  |  |  |

| RR8           | Receive Data FIFO, 8 Bits Deep                                             |  |  |  |  |

| RR9           | WR9 Mirror, if WR7' bit D6 Equals 1                                        |  |  |  |  |

| RR10          | Miscellaneous Status Bits                                                  |  |  |  |  |

| RR11          | WR11 Mirror, if WR7' bit D6 Equals 1                                       |  |  |  |  |

| RR12          | Lower Byte of BRG Time Constant                                            |  |  |  |  |

| RR13          | Upper Byte of BRG Time Constant                                            |  |  |  |  |

| RR14          | WR14 Mirror, if WR7' bit D6 Equals 1                                       |  |  |  |  |

| RR15          | WR 15 Mirror, if WR7' bit D6 Equals 1                                      |  |  |  |  |

There are three modes used to move data into and out of the ESCC:

- 1. POLLING

- 2. INTERRUPT (vectored and non-vectored)

- 3. BLOCK TRANSFER

The BLOCK TRANSFER mode can be implemented under CPU or DMA control.

#### **POLLING**

When POLLING, data interrupts are disabled, three registers in the ESCC are automatically updated whenever any function is performed. For example, end-of-frame (EOF) in SDLC mode sets a bit in one of these status registers. The purpose of POLLING is for the CPU to periodically read a status register until the register contents indicate the need that data requires transfer. RR0 is the only register that must be read to determine if data needs to be transferred. An alternative to polling RR0 for each channel is to poll the Interrupt

Pending register. Status information for both channels resides in one register. Only one register may be read. Depending on its contents, the CPU performs one of the three operations listed below:

- 1. Write data

- 2. Read data

- 3. Continues processing

Two bits in the register indicate the requirement for data transfer.

#### **INTERRUPT**

The ESCC INTERRUPT mode supports vectored and nested interrupts. The fill levels at which the transmit and receive FIFOs interrupt the CPU are programmable, allowing the ESCC requests for data transfer to be tuned to the system interrupt response time.

Nested interrupts are supported with the interrupt acknowledge ( $\overline{INTACK}$ ) feature of the ESCC. It allows the CPU to acknowledge the occurrence of an interrupt, and re-enable higher priority interrupts. Since an  $\overline{INTACK}$  cycle releases the  $\overline{INT}$  pin from the active state, a higher priority ESCC interrupt or another higher priority device can interrupt the CPU. When an ESCC responds to  $\overline{INTACK}$  signal from the CPU, it can place an interrupt vector on the data bus. This vector is written in WR2 and may be read in RR2. To increase the interrupt response time, the ESCC can modify 3 bits in this vector to indicate status. If the vector is read in Channel A, status is not included. If it is read in Channel B, status is included.

Each of the six sources of interrupts in the ESCC (Transmit, Receive, and External/Status interrupts in both channels) has 3 bits associated with the interrupt source as listed below:

- 1. Interrupt Pending (IP)

- 2. Interrupt Under Service (IUS)

- 3. Interrupt Enable (IE)

If the IE bit is set for a given interrupt source, then that source can request interrupts. However, when the Master Interrupt Enable (MIE) bit in WR9 is reset, no interrupts can be requested. The IE bits are write-only. The other two bits are related to the interrupt priority chain (see Figure 7 on page 13). The ESCC can request an interrupt only when no higher priority device is requesting an interrupt (that is, when IEI is High). If the device in question requests an interrupt, it pulls down  $\overline{\text{INT}}$ . The CPU then responds with  $\overline{\text{INTACK}}$ , and the interrupting device places a vector on the data bus.

Figure 7. ESCC Interrupt Priority Schedule

The ESCC can also execute an Interrupt Acknowledge cycle using software. Sometimes it is difficult to create the INTACK signal with the necessary timing to acknowledge interrupts and allow the nesting of interrupts. In such cases, interrupts can be acknowledged with a software command to the ESCC. For more information, Z80230/Z85230/L Enhancements on page 22

Interrupt Pending (IP) bits signal a need for interrupt servicing. When an IP bit is 1 and the IEI input is High, the INT output is pulled Low, requesting an interrupt. In the ESCC, if an IE bit is not set, then the IP for that source is never set. The IP bits are read in RR3A.

The Interrupt Under Service (IUS) bits signal that an interrupt request is serviced. If IUS is set to 1, all interrupt sources of low priority in the ESCC and external to the ESCC are prevented from requesting interrupts. The internal interrupt sources are inhibited by the state of the internal daisy chain, while lower priority devices are inhibited by setting IEO Low for subsequent peripherals. An IUS bit is set during an Interrupt Acknowledge cycle if there are no higher priority devices requesting interrupt.

There are three type of interrupts as listed below:

- 1. Transmit

- 2. Receive

- 3. External/Status

Each interrupt type is enabled under program control with Channel A having higher priority than Channel B, and with Transmit, Receive, and External/Status interrupts prioritized in that order within each channel. When the Transmit interrupt is enabled (WR1 bit 1 is 1), the occurrence of the interrupt depends on the state of WR7' bit 5. If WR7' bit 5 is 0, the CPU is interrupted when the top byte of the transmit First In First Out (FIFO) becomes empty. If WR7' bit 5 is 1, the CPU is interrupted when the transmit FIFO becomes completely empty. The transmit interrupt occurs when the data in the exit location of the Transmit FIFO loads into the Transmit Shift Register and the Transmit FIFO becomes completely empty. This condition means that there must be at least one character written to the Tx FIFO for it to become empty.

When the receiver is enabled, the CPU is interrupted in one of the following three methods:

- 1. Interrupt on First Receive Character or Special Receive Condition

- 2. Interrupt on All Receive Characters or Special Receive Conditions

- 3. Interrupt on Special Receive Conditions Only

If WR7' bit 3 is 1, and the Special Receive Condition is selected, the Receive character occurs when there are four bytes available in the Receive FIFO. This is most useful in synchronous applications as the data is in consecutive bytes. Interrupt on First Character or Special Condition and Interrupt on Special Condition Only are typically used with the BLOCK TRANSFER mode. A special Receive Condition consists of one of the following:

- Receiver Overrun

- Framing error in ASYNCHRONOUS mode

- EOF in SDLC mode

- Parity error (optional)

The Special Receive Condition interrupt is different from an ordinary receive character available interrupt only by the status placed in the vector during the Interrupt Acknowledge cycle. In Receive Interrupt on First Character or Special Condition mode, an interrupt occurs from Special Receive Conditions any time after the first receive character interrupt.

The primary function of the External/Status interrupt is to monitor the signal transitions of the  $\overline{CTS}$ ,  $\overline{DCD}$ , and  $\overline{SYNC}$  pins. However, an External/Status interrupt is also caused by any of the following:

- A Transmit Underrun condition

- A zero count in the BRG

- A detection of a Break (ASYNCHRONOUS mode)

- An ABORT (SDLC mode)

- An End Of Poll (EOP) sequence in the data stream (SDLC LOOP mode)

The interrupt caused by the ABORT or EOP sequence has a special feature that allows the ESCC to interrupt when the ABORT or EOP sequence is detected or terminated. This feature facilitates the proper termination of the current message, correct initialization of the next message, and the accurate timing of the ABORT condition by external logic in SDLC mode. SDLC LOOP mode allows secondary stations to recognize the primary station and regain control of the loop during a poll sequence.

#### CPU/DMA BLOCK TRANSFER

The ESCC provides a BLOCK TRANSFER mode to accommodate CPU/DMA controller. The BLOCK TRANSFER mode uses the WAIT/REQUEST output in conjunction with the WAIT/REQUEST bits in WR1. The WAIT/REQUEST output can be defined as a WAIT line in the CPU BLOCK TRANSFER mode or as a REQUEST line in the DMA BLOCK TRANSFER mode.

To a DMA controller, the ESCC REQUEST output indicates that the ESCC is ready to transfer data to or from memory.

To the CPU, the  $\overline{WAIT}$  line indicates that the ESCC is not ready to transfer data, thereby requesting the CPU to extend the I/O cycle.

The DTR/REQUEST line allows full-duplex operation under DMA control. The ESCC can be programmed to deassert the DTR/REQUEST pin with the same timing as the WAIT/REQUEST pin if WR7' bit 4 is 1.

# **ESCC Data Communications Capabilities**

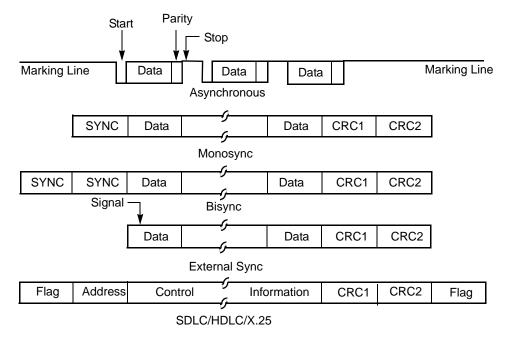

The ESCC provides two independent full-duplex programmable channels for use in any common ASYNCHRONOUS or SYNCHRONOUS data communication protocols (see Figure 8). The channels have identical features and capabilities.

Figure 8. Various ESCC Protocols

#### **ASYNCHRONOUS Mode**

The ESCC has significant improvements over the standard Serial Communications Controller (SCC). The addition of the deeper data FIFOs provide greater protection against underruns and overruns as well as more efficient use of bus bandwidth. The deeper data FIFOs are accessible regardless of the protocol used and they need not be enabled. For information on these improvements, see Z80230/Z85230/L Enhancements on page 22

Send and Receive allow 5 to 8 bits per character, plus optional Even or Odd parity. The transmitters can supply 1, 1.5, or 2 stop bits per character and can provide break indication. The receiver break-detection logic interrupts the CPU both at the start and at the end of a received break. Reception is protected from spikes by start-bit validation that delays the signal for a length of time equal to one half the time period required to process 1 bit of data after a Low level is detected on the receive data input (RxDA or RxDB pins). If the Low level does not persist (that is, a transient), the character assembly process does not start.

Framing errors and overrun errors are detected and buffered together with the character at which they occur. Vectored interrupts allow fast servicing of error conditions. Furthermore, a built-in checking process avoids the interpretation of a framing error as a new start bit. A framing error results in the addition of a delay of one half the amount of time required to process 1 bit of data at the point at which the search for the next start bit begins. Transmit and Receive clock can be selected from any of the several sources. In ASYNCHRONOUS mode, the \$\overline{SYNC}\$ pin may be programmed as an input with interrupt capability.

#### **SYNCHRONOUS Mode**

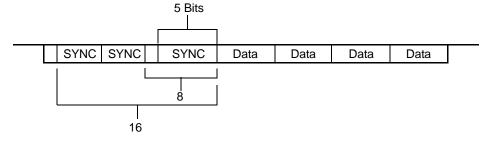

The ESCC supports both byte-oriented and bit-oriented SYNCHRONOUS communication. SYNCHRONOUS byte-oriented protocols are handled in several modes. They enable character synchronization with a 6- or 8-bit SYNC character (MONOSYNC) or a 12-bit or 16-bit synchronization pattern (BISYNC), or with an external sync signal. Leading sync characters are removed without interrupting the CPU.

5- or 7-bit sync characters are detected from 8- or 16-bit patterns in the ESCC by overlapping the larger pattern across multiple incoming sync characters as displayed in Figure 9.

Figure 9. Detecting 5- or 7-Bit Synchronous Characters

CRC checking for SYNCHRONOUS BYTE-ORIENTED mode is delayed by one character time so that the CPU may disable CRC checking on specific characters. This action permits the implementation of protocols such as IBM BISYNC.

Both CRC-16 ( $X^{16} + X^{15} + X^2 + 1$ ) and CRC-CCITT ( $X^{16} + X^{12} + X^5 + 1$ ) error checking polynomials are supported. Either polynomial may be selected in all synchronous modes. You can preset the CRC generator and checker to all 1s or all 0s. The ESCC also provides a feature that automatically transmits CRC data when no other data is available for transmission. This feature enables high-speed transmissions under DMA control, with no need for CPU intervention at the end of a message. When there is no data or CRC to send in the SYNCHRONOUS mode, the transmitter inserts 6-, 8-, 12-, or 16-bit SYNC characters, regardless of the programmed character length.

#### **SDLC Mode**

The ESCC supports SYNCHRONOUS bit-oriented protocols, such as SDLC and High-Level Data Link Control (HDLC), by performing automatic flag sending, zero insertion, and CRC generation.

A special command is used to abort a frame which is in transmission. At the end of a message, the ESCC automatically transmits the CRC and trailing flag when the transmitter underruns. The transmitter may also be programmed to send an idle line consisting of continuous flag characters or a steady marking condition.

If a transmit underrun occurs in the middle of a message, an External/Status interrupt warns the CPU of this status change so that an Abort command can be issued. The ESCC may also be programmed to send an Abort command by itself, in the event of an underrun, relieving the CPU of the task. The last character of a frame may consist of 1- to 8-bits, allowing reception of frames of any length.

The receiver automatically synchronizes on the leading flag of a frame in SDLC or HDLC and provides a synchronization signal on the  $\overline{SYNC}$  pin (an interrupt may also be programmed). The receiver may search for frames addressed by 1-byte or 4-bits within a byte of a user-specified address or for a global broadcast address. Frames not matching either the user-selected address or broadcast address are ignored.

The number of address bytes are extended under software control. To receive data, an interrupt can be selected on the first received character, or on every character, or On Special Condition Only (EOF). The receiver automatically deletes all zeros inserted by the transmitter during character assembly. CRC is also calculated and is automatically checked to validate frame transmission. At the end of transmission, the status of a received frame is available in the status registers. In SDLC mode, the ESCC must be programmed to use the CRC-CCITT polynomial, but the generator and checker may be pre-set to all 1s or all 0s. The CRC data is inverted before transmission and the receiver checks against the bit pattern 0001110100001111.

NRZ, NRZI, or FM coding may be used in any 1X mode. The parity options available in ASYNCHRONOUS mode are also available in SYNCHRONOUS mode. However, parity checking is not normally used for SDLC because CRC checking is more robust.

#### **SDLC LOOP Mode**

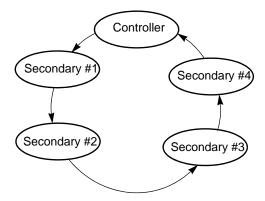

The ESCC supports SDLC LOOP mode as well as normal SDLC. In SDLC LOOP mode, a primary controller station manages the message traffic flow on the loop and any number of secondary stations. In SDLC LOOP mode, the ESCC performs the functions of a secondary station. An ESCC operation in regular SDLC mode may act as a controller (see Figure 10). SDLC LOOP mode is selected by setting WR10 bit 1 to 1.

Figure 10. SDLC LOOP mode

A secondary station in an SDLC LOOP mode always monitors the messages sent around the loop and passes these messages to the rest of the loop, retransmitting them with a one-bit time delay. The secondary station places its own message in the loop only at specific times. The controller indicates that the secondary stations can transmit messages by sending a special character, called EOP, around the loop. The EOP character has a bit pattern 111111110, the same pattern as an Abort character in normal HDLC. This bit pattern is unique and easily recognized, because of the zero insertion in the message.

When a secondary station has a message to transmit and recognizes an EOP on the line, it changes the last binary 1 of the EOP to a 0 before transmission. This action changes the EOP into a flag sequence. The secondary station now places its message on the loop and terminates the message with an EOP. Any secondary stations further down the loop with messages to transmit appends their messages to the message of the first secondary station using the same process. Secondary stations without any messages to transmit merely echo the incoming message. All secondary stations are prohibited from placing messages on the loop except upon recognizing an EOP. In SDLC LOOP mode, NRZ, NRZI or FM coding can be used.

#### **SDLC Status FIFO**

The ESCC's ability to receive high speed back-to-back SDLC frames is maximized by a 10-bit deep by 19-bit wide status FIFO buffer. When enabled (through WR15 bit 2 is 1), the storage area enables DMA to continue data transfer into the memory, so that the CPU examines the message later. For each SDLC frame, 14 counter bits and 5 Status/Error bits are stored. The byte count and status bits are accessed through Read Registers, RR6, and RR7. RR6 and RR7 are only used when the SDLC FIFO buffer is enabled. The 10 x 19 status FIFO buffer is separate from the 8-byte receive data FIFO buffer.

#### **Baud Rate Generator**

Each channel in the ESCC contains a programmable BRG. Each generator consists of two 8-bit registers that form a 16-bit time constant, a 16-bit down counter, and a flip-flop on the output, producing a square wave. At start-up, the flip-flop at the output is set High, the value in the time constant register is loaded into the counter, and the count down begins. When the BRG reaches zero, the output toggles, the counter is reloaded with the time constant, and the process repeats. The time constant can be changed at any time, but the new value does not take effect until the counter is loaded again.

The output of the BRG may be used as the Transmit clock, the Receive clock, or both. The output can also drive the DPLL. For more information, see <u>Digital Phase-Locked Loop</u>.

If the receive clock or the transmit clock is not programmed to come from the TRxC pin, the output of the BRG may be echoed out by the TRxC pin.

The following formula relates the time constant to the baud rate. PCLK or  $\overline{RTxC}$  is the clock input to the BRG. The clock mode is 1, 16, 32, or 64, as selected in WR 4 bits 6 and 7

Time Constant =

$$\frac{PCLK \text{ or RTxC Frequency}}{2(\text{Baud Rate}) \text{ (Clock Mode)}} - 2$$

#### **Digital Phase-Locked Loop**

The ESCC contains a DPLL to recover clock information from a data stream with NRZI or FM encoding. The DPLL is driven by a clock that is nominally 32 (NRZI) or 16 (FM) times the data rate. The DPLL uses this clock, along with the data stream, to construct a clock for the data. This clock is then used as the ESCC receive clock, the transmit clock, or both. When the DPLL is selected as the transmit clock source, it provides a jitter-free clock output. The clock output is the DPLL input frequency divided by the appropriate divisor for the selected encoding technique.

For NRZI encoding, the DPLL counts the 32x clock to create nominal bit times. As the 32x clock is counted, the DPLL searches the incoming data stream for edges (either 1 to 0 or 0 to 1). When a transition is detected the DPLL makes a count adjustment (during the next counting cycle), producing a terminal count closer to the center of the bit cell.

For FM encoding, the DPLL counts from 0 to 32, but with a cycle corresponding to two bit times. When the DPLL is locked, the clock edges in the data stream occurs between counts 15 and 16 and between counts 31 and 0. The DPLL looks for edges only during a time centered on the 15 to 16 counting transition.

The 32x clock for the DPLL can be programmed to come from either the RTxC input or the output of the BRG. The DPLL output is programmed to be echoed out the ESCC by the TRxC pin (if this pin is not being used as an input).

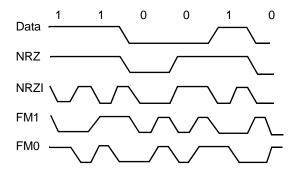

### **Data Encoding**

Data encoding allows the transmission of clock and data information over the same medium. This capability saves the need to transmit clock and data over separate medium as is normally required tor synchronous data. The ESCC provides four different data encoding methods, selected by bits 6 and 5 in WR10. Examples of these 4 encoding methods is displayed in Figure 11. Any encoding method is used in any X1 mode in the ESCC, ASYNCHRONOUS or SYNCHRONOUS. The data encoding selected is active even if the transmitter or receiver is idling or disabled.

Figure 11. Data Encoding Methods

Table 3 lists the four encoding methods, their levels, and values.

**Table 3. Data Encoding Descriptions**

| Code Type | Level               | Value  |  |  |

|-----------|---------------------|--------|--|--|

| NRZ       | High<br>Low         | 1<br>0 |  |  |

| NRZI      | No Change<br>Change | 1<br>0 |  |  |

**Table 3. Data Encoding Descriptions (Continued)**

| Code Type           | Level                                                                                                                                                                                                                | Value |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| FM1 (biphase mark)  | Additional Transition at the Center of the Bit Cell<br>No Additional Transition at the Center of the Bit<br>Cell                                                                                                     | 1 0   |

| FM0 (biphase space) | A transition occurs at the beginning of every bit call. A 0 is represented by an additional transition at the center of the bit cell.  A 1 is represented by no additional transition at the center of the bit cell. | 0     |

In addition to the four methods, ESCC can be used to decode Manchester (biphase level) data using DPLL in the FM mode and programming the receiver for NRZ data. Manchester encoding always produces a transition at the center of the bit cell. If the transition is 0 to 1, the bit is a 0. If the transition is 1 to 0, the bit is a 1.

### **Auto Echo and Local Loopback**

The ESCC is capable of automatically echoing everything it receives. This feature is useful mainly in ASYNCHRONOUS modes, but works in SYNCHRONOUS and SDLC modes as well. AUTO ECHO mode (TxD is RxD) is used with NRZI or FM encoding with an additional delay because the data stream is not decoded before retransmission. In AUTO ECHO mode, the  $\overline{CTS}$  input is ignored as a transmitter enable, (although transitions for this input can cause interrupts if programmed to do so). In this mode, the transmitter is actually bypassed and the programmer is responsible for disabling transmitter interrupts and  $\overline{Wait/Request}$  on transmit.

The ESCC is also capable of LOCAL LOOPBACK. In this mode the internal transmit data is tied to the internal receive data and RxD is ignored. The  $\overline{CTS}$  and  $\overline{DCD}$  inputs are also ignored as transmit and receive enables. However, transitions on these inputs can cause interrupts. LOCAL LOOPBACK works in ASYNCHRONOUS, SYNCHRONOUS, and SDLC modes with NRZ, NRZI, or FM coding of the data stream.

# Z80230/Z85230/L Enhancements

A detailed description of the enhancements to the Z80230/Z85230/L ESCC that differentiate it from the standard SCC is provided below:

# 4-Byte Transmit FIFO Buffer

The ESCC has a 4-byte transmit buffer with programmable interrupt and DMA request levels. It is not necessary to enable the FIFO buffer as it is always available. You can set the Transmit Buffer Empty (TBE) interrupt and DMA Request on Transmit command to be generated either when the top byte of transmit FIFO is empty or only when the FIFO is completely empty. A hardware or channel reset clears the transmit shift register, flushes the transmit FIFO, and sets WR7' bit 5 to 1.

If the transmitter generates the interrupt or DMA request for data when the top byte of the FIFO is empty (WR7' bit 5 is 0), the system allows for a long response time to the data request without underflowing. The interrupt service routine (ISR) writes 1byte and then tests RR0 bit 2. The DMA Request on Transmit in this mode is set to 0 after each data Write (that is, TBE), RR0 bit 2, is set to 1 when the top byte of the FIFO is empty. WR7' bit 5 resets to 1.

In applications for which the interrupt frequency is important, the transmit ISR can be optimized by programming the ESCC to generate the TBE interrupt only when the FIFO is completely empty (WR7' bit 5 is 1) and, writing 4 bytes to fill the FIFO. When WR7' bit 5 is 1, only one DMA request is generated, filling the bottom of the FIFO. However, this may be advantageous for applications where the possible reassertion of the DMA request is not required. The TBE status bit, RR0 bit 2, is set to 1 when the top byte of the FIFO is empty. WR7' bit 5 is set to 1 after a hardware or channel reset.

# 8-Byte Receive FIFO

The ESCC has an 8-byte receive FIFO with programmable interrupt levels. It is not necessary to enable the 8-byte FIFO as it is always available. A hardware or channel reset clears the Receive Shift register and flushes the Receive FIFO. The Receive Character Available interrupt is generated as selected by WR7' bit 3. The Receive Character Available bit, RR0 bit 0 is set to 1 when at least one byte is available at the top of the FIFO (independent of WR7' bit 3).

A DMA Request on Receive, if enabled, is generated whenever 1 byte is available in the receive FIFO independent of WR7' bit 3. If more than 1 byte is available in the FIFO, the Wait/Request pin becomes inactive and becomes active when the FIFO is emptied.

By resetting WR7' bit 3 to 0, applications which have a long latency to interrupts can generate the request to read data from the FIFO when one byte is available. The application can then test the Receive Character Available bit to determine if more data is available.

By setting WR7' bit 3 to 0, the ESCC can issue an interrupt when the receive FIFO is half full (4 bytes available), allowing the frequency of interrupts to be reduced. If WR7' bit 3 is 1, the Receive Character Available interrupt is generated when there are 4 bytes available. If the ISR reads 4 bytes during each routine, the frequency of interrupts is reduced.

If WR7' bit 3 is 1 and Receive Interrupt on All Characters and Special Conditions is enabled, the receive character available interrupt is generated when four characters are available. However, when a character is detected to have a special condition, an interrupt is generated when the character is loaded into the top four bytes of the FIFO. Therefore, the Special Condition ISR must be RR1 before reading the data to determine which byte has the special condition.

# Write Register 7 PRIME (WR7')

A new register, WR7', has been added to the ESCC to enable the programming of six new features. The format of this register is listed in Table 4.

Table 4. Write Register 7 Prime (WR7')

| Bit                                        | 7 | 6 | 5 | 4  | 3 | 2 | 1 | 0 |

|--------------------------------------------|---|---|---|----|---|---|---|---|

| R/W                                        | W | W | W | /W | W | W | W | W |

| Reset                                      | 0 | 0 | 0 | 0  | 0 | 0 | 0 | 0 |

| Note: R = Read W = Write X = Indeterminate |   |   |   |    |   |   |   |   |

| Bit<br>Position | R/W   | Value | Description             |

|-----------------|-------|-------|-------------------------|

| i Osition       | 17/44 | Value | Description             |

| 7               | W     | 0     | Reserved, must be 0     |

| 6               | W     |       | Extended Read Enable    |

| 5               | W     |       | Transmit FIFO Int Level |

| 4               | W     |       | DTR/REQ Timing Mode     |

| 3               | W     |       | Receive FIFO Int Level  |

| 2               | W     |       | Auto RTS Deactivation   |

| 1               | W     |       | Auto EOM Reset          |

| 0               | W     |       | Auto Transmit Flag      |

WR7' is written by first setting Bit 0 of Write Register 15 (WR15 bit 0) to 1 and then accessing WR7. All write commands to register 7 are to WR7' while WR15 bit 0 is set to

1. WR15 bit 0 must be reset to 0 to address the SYNC character in register WR7. If bit 6 of WR7' is set to 1, then WR7' can be read by performing a read cycle to RR14. The WR7' features remain enabled until specifically disabled or by a hardware or software reset. Bit 5 is set to 1 and all other bits are reset to 0 after a reset.

For applications which use either the Zilog Z8X30SCC or Z80230, these two device types can be identified in software with the following test:

- 1. Write 01H to Write Register 15

- 2. Read Register 15

If bit 0 is set to 0, the device is Z8X30SCC. If bit 0 is set to 1, it is a Z80C30. If the device is Z8XC30, a write to WR15 is required before proceeding. If the device is Z80230, all writes to address 7 are to WR7' until WR15 is set to 0.

The WR7 register bits are described below:

### Bit 7 (Not used)

This bit must always be 0.

### Bit 6 (Extended Read Enable)

Setting this bit to 1 enables WR3, WR4, WR5, WR7' and WR10 to be read by issuing a READ command for RR9 (WR3) RR4, RR5, RR14 (WR7') and RR11 (WR10), respectively.

#### **Bit 5 (Transmit FIFO Interrupt Level)**

If this bit is set to 1, the TBE interrupt is generated when the transmit FIFO is completely empty. If this bit is set to 0, the TBE interrupt is generated when the top byte of the transmit FIFO is empty. This bit is set following a hardware or channel reset.

In DMA REQUEST ON TRANSMIT mode, when using either the  $\overline{W/REQ}$  or  $\overline{DTR/REQ}$ pins, the request is asserted when the Tx FIFO is completely empty if WR7' bit 5 is set to 1. The request is asserted when the top byte of the FIFO is empty if bit 5 is reset.

# Bit 4 (DTR/REQ Timing)

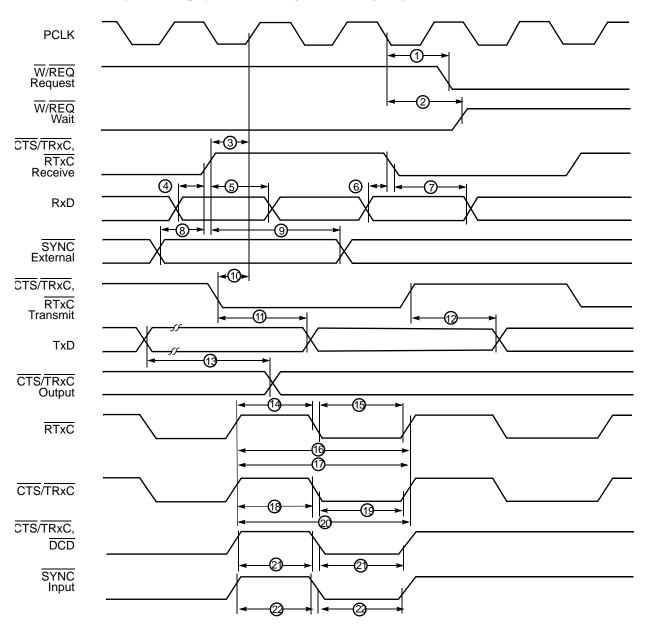

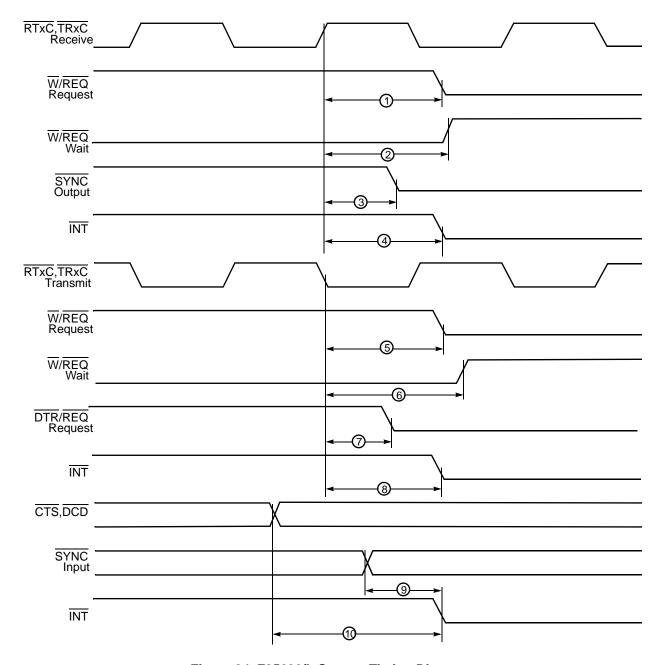

If this bit is set to 1 and the  $\overline{DTR}/\overline{REQ}$  pin is used for REQUEST mode (WR14 bit 2 is 1), the deactivation of the DTR/REQ pin is identical to the W/REQ pin as displayed in Figure 12 on page 25. If this bit is reset, the deactivation time is 4TcPc.

Figure 12. DMA Request on Transmit Deactivation Timing

#### Bit 3 (Receive FIFO Interrupt Level)

This bit sets the interrupt level of the receive FIFO. If this bit is set to 1, the receive data available bit is asserted when the receive FIFO is half full (4 bytes available). If this bit is reset to 0, the Receive Data Available interrupt is requested when all bytes are set. For more information, see 8-Byte Receive FIFO on page 22.

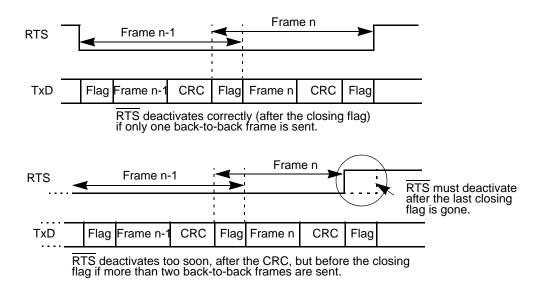

# Bit 2 (Automatic RTS Pin Deassertion)

This bit controls the timing of the deassertion of the  $\overline{RTS}$  pin in SDLC mode. If this bit is 1 and WR5 bit 1 is set to 0 during the transmission of an SDLC frame, the deassertion of the  $\overline{RTS}$  pin is delayed until the last bit of the closing flag clears the TxD pin. The  $\overline{RTS}$  pin is pulled High after the rising edge of the transmit clock cycle from the last bit of the closing flag. This action implies that the ESCC must be programmed for Flag on Underrun (WR10 bit 2 is 0) for the  $\overline{RTS}$  pin to deassert at the end of the frame. This feature works independently of the programmed Transmitter Idle state. In SYNCHRONOUS mode other than SDLC, the  $\overline{RTS}$  pin immediately follows the state programmed into WR5 bit 1. When WR7' bit 2 is set to 0, the  $\overline{RTS}$  follows the state of WR5 bit 1.

#### **Bit 1 (Automatic EOM Reset)**

If this bit is 1, the ESCC automatically resets the Tx Underrun/EOM latch and presets the transmit CRC generator to its programmed preset state (per values set in WR5 bit 2 and WR10 bit 7). Therefore, it is not necessary to issue the Reset Tx Underrun/EOM Latch command when this feature is enabled.

# Bit 0 (Automatic Tx SDLC Flag)

If this bit is 1, the ESCC automatically transmits an SDLC flag before transmitting data. This action removes the requirement to reset the Mark Idle bit (WR10 bit 3) before writing data to the transmitter.

Historically, the SCC latched the databus on the falling edge of WR. However, as many CPUs do not guarantee that the databus is valid when the WR pin goes Low, Zilog modified the databus timing to allow a maximum delay of 20 nS from the WR signal going active Low to the latching of the databus.

# **CRC Reception in SDLC Mode**

In SDLC mode, the entire CRC is clocked into the receive FIFO. The ESCC completes clocking in the CRC to allow it to be retransmitted or manipulated software. In the SCC, when the closing flag is recognized, the contents of the receive shift register are immediately transferred to the receive FIFO, resulting in the loss of the last two bits of the CRC. In the ESCC, it is not necessary to program this feature. When the closing flag is detected, the last 2 bits of the CRC are transferred into the receive FIFO. In all other SYNCHRONOUS mode, the ESCC does not clock in the last 2 CRC bits (same as the SCC).

# TxD Forced High in SDLC with NRZI Encoding When Marking Idle

When the ESCC is programmed for SDLC mode with NRZI data encoding and Mark Idle (WR10 bit 6 is 0, bit 5 is 1, bit 3 is 1), the TxD pin is automatically forced High when the transmitter enters the Mark Idle state. There are several different ways for the transmitter to enter the Idle state. In each of the following cases the TxD pin is forced High when the Mark Idle condition is reached:

- Data, CRC, flag, and Idle

- Data, flag, and Idle

- Data, abort (on underrun), and Idle

- Data, abort (command), and Idle

- Idle flag and command to Idle Mark

The Force High feature is disabled when the Mark Idle bit is set to 0.

This feature is used in combination with the automatic SDLC opening flag transmission feature, WR7' bit 0 is 1, to assure that data packets are formatted correctly. In this case, the CPU is not required to issue any commands. If WR7' bit 0 is 0, as on the SCC, the Mark Idle bit (WR10 bit 3), is set to 1, to enable flag transmission before an SDLC packet transmits.

# Improved Transmit Interrupt Handling

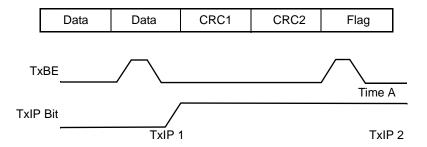

The ESCC latches the TBE interrupt because the CRC is loaded into the Transmit Shift register even if the TBE interrupt, due at the last data byte, has not been reset. The end of a synchronous frame is guaranteed to generate two TBE interrupts even if a Reset Transmit Buffer Interrupt command for the data created interrupt is issued after the CRC interrupt occurs (Time A in Figure 13). Two Reset TBE commands are required. The TxIP latches if the EOM latch resets before the end of the frame.

Figure 13. TxIP Latching

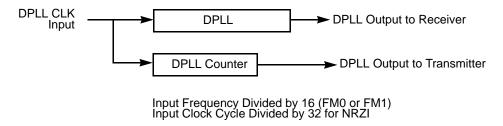

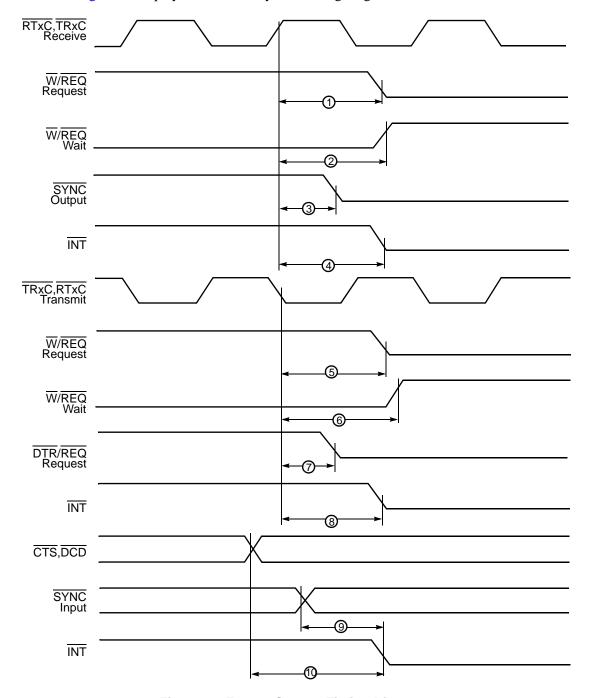

### **DPLL Counter Tx Clock Source**

When the DPLL is selected as the transmit clock source, the DPLL counter output is the DPLL source clock divided by the appropriate divisor for the programmed data encoding format. In FM mode (FM0 or FM1), the DPLL counter output signal is the input frequency divided by 16.

In NRZI mode, the DPLL counter output signal is the input clock cycle divided by 32. This feature provides a jitter-free output signal that replaces the DPLL transmit clock output as the transmit clock source. This action has no effect on the use of the DPLL as the receive clock source (see Figure 14).

Figure 14. DPLL Outputs

# Read Register 0 Status Latched During Read Cycle

The contents of Read Register 0, RR0 is latched during a Read operation. The ESCC prevents the contents of RR0 from changing during a Read operation. But, the SCC allows the status of RR0 to change while reading the register and may require reading RR0 twice. The contents of RR0 is updated after the rising edge of  $\overline{RD}$  signal.

# Software Interrupt Acknowledge

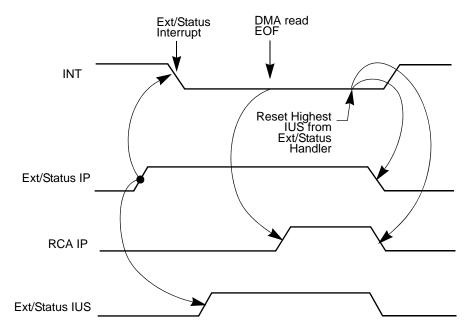

The Z80230/Z85230/L interrupt acknowledge cycle can be initiated using software. If Write Register 9 (WR9 bit 5 is 1), Read Register 2 (RR2) results in an interrupt INTACK cycle, a software acknowledgment causes the INT pin to go High. The IEO pin goes Low. The Interrupt Under Service (IUS) latch is set to the highest priority pending interrupt.

When a hardware INTACK signal is desired, a software acknowledge cycle requires that a Reset Highest IUS command be issued in the ISR. If RR2 is read from Channel A, the unmodified vector is returned. If RR2 is read from Channel B, then the vector is modified to indicate the source of the interrupt. The Vector Includes Status (VIS) and No Vector (NV) bits in WR9 are ignored when WR9 bit 5 is set to 1.

If the  $\overline{INTACK}$  and IEI pins are not used, they are pulled up to  $V_{CC}$  through a resistor (2.2 k?, typical).

# Fast SDLC Transmit Data Interrupt Response

To facilitate the transmission of back-to-back SDLC frames with a single shared flag between frames, the ESCC allows data for a second frame to be written to the transmit FIFO after the Tx Underrun/EOM interrupt occurs. This feature allows application software more time to write the data to the transmitter while allowing the current frame to conclude with CRC and flag. The SCC required that data not be written to the transmitter until a TBE interrupt is generated after the CRC completed transmission.

If data is written to the transmit FIFO after the Transmit Underrun/EOM interrupt is issued but before the TBE interrupt is issued, the Automatic EOM Reset function is enabled (WR7' bit 1 is 1). Consequently, the commands Reset Tx/Underrun EOM Latch and Reset Tx CRC Generator must never be used.

#### SDLC FIFO Frame Status Enhancement

When used with a DMA controller, the ESCC SDLC Frame Status FIFO enhancement maximizes the ESCC's ability to receive high-speed, back-to-back SDLC messages. It minimizes frame overruns due to CPU latencies in responding to interrupts. The feature (displayed in Figure 15 on page 29) includes:

- 10-bit deep by 19-bit wide status FIFO

- 14-bit receive byte counter

- Control logic

The 10 x 19 bits status FIFO is separate from the 8-byte receive data FIFO.

When the enhancement is enabled, the status in Read Register 1 (RR1) and byte count for the SDLC frame are stored in the 10- x 19-bit status FIFO. This action allows the DMA

controller to transfer the next frame into memory while the CPU verifies the previously received frame.

#### Frame Status FIFO Circuitry Reset on Flag Detect SCC Status Register Increment on RR1 Residue Bits (3) Overrun, CRC Error **Byte Counter** Each Received Character **Enable Count in SDLC EOF Signal** 5 Bits 14 Bits Status Read Complete FIFO Array 10- by 19- Bits Tail Pointer 4-Bit Counter **Head Pointer** 4-Bit Counter 4-Bit Comparator Over Equal 5 Bits 8 Bits EOF=1 6 Bits 6-Bit MU ΕN 6 Bits RR1 2 Bits **FIFO** Bit Bit Bits RR6 Enable **√**6 7 5-0 WR15 Bit 2 Set Enables Interface to SCC RR7 5 - 0 + RR6 7-0 14-Bit Byte Counter Status FIFO (16 KB Maximum Count) RR7 Bit 7 FIFO data-available status bit (1 during read) RR7 Bit 7 FIFO Overflow Status Bit (1 on overflow) See Notes:, next.

Figure 15. SDLC Frame Status FIFO

# Notes:

- 1. All Sent bypasses MUX and equals contents of SCC Status Register.

- 2. Parity bits bypass MUX and equals contents of SCC Status Register.

- 3. EOF is set to 1 whenever reading from the FIFO.

Summarizing the operation: Data is received, assembled, and loaded into the 8-byte FIFO before transferring to memory by the DMA controller.

When a flag is received at the end of an SDLC frame, the frame byte count from the 14-bit counter and 5 status bits are loaded into the status FIFO for verification by the CPU. The CRC checker is automatically reset in preparation for the next frame, which starts immediately.

Because the byte count and status are saved for each frame, the message integrity can be verified at a later time. Status information for up to ten frames is stored before a status FIFO overrun occurs.

If a frame is terminated with an Abort command, the byte count and status is loaded to the status FIFO and the counter is reset for the next frame.

#### FIFO Enable/Disable

This FIFO buffer is enabled when WR15 bit 2 is 1 and the ESCC is in the SDLC/HDLC mode. Otherwise, the status register contents bypass the FIFO and transfer directly to the bus interface (the FIFO pointer logic is reset either when disabled or by a channel or power-on reset). When the FIFO mode is disabled, the ESCC is downward-compatible with the NMOS Z8030/Z8530. The FIFO mode is disabled on power-up (WR15 bit 2 set to 0 on reset). The effects of backward compatibility on the register set are that RR4 is an image of RR0, RR5 is an image of RR1, RR6 is an image of RR2, and RR7 is an image of RR3. For information on the added registers, see Read Registers on page 53. The status of the FIFO Enable signal is read at RR15 bit 2. If the FIFO is enabled, the bit is set to 1; otherwise it is reset to 0.

# **FIFO Read Operation**

When WR15 bit 2 is 1 and the FIFO is not empty, the next read status register RR1 or the additional registers RR7 and RR6, reads the FIFO. Reading status register RR1 causes one location of the FIFO to empty, so status is read after reading the byte count; otherwise the count is incorrect. Before the FIFO underflows, it is disabled. In this case, the multiplexer is switched to allow status to read directly from the status register. In this state, reads from RR7 and RR6 are undefined bit 6 of RR7 (FIFO data available) status data is coming from the FIFO or directly from the status register, because it is set to 1 whenever the FIFO is not empty.

Since all status bits are not stored in the FIFO, the All Sent, Parity, and EOF bits bypass the FIFO. The status bits sent through the FIFO are the three Residue Bits, Overrun, and CRC Error.

The correct sequence for polling the byte count and FIFO logic is RR7, RR6, then RR1 (reading RR6 is optional). Additional logic prevents the FIFO from emptying by multiple reads from RR1. The read from RR7 latches the FIFO empty/full status bit (bit 6) and steers the status multiplexer to read the ESCC megacell instead of the status FIFO

(because the status FIFO is empty). The read from RR1 allows an entry to be read from the FIFO (if the FIFO is empty, the logic prevents a FIFO underflow condition).

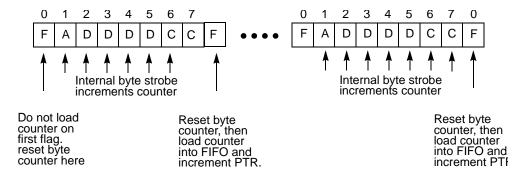

# **FIFO Write Operation**

When the end of an SDLC frame is received and the Status FIFO is enabled, the contents of the status and byte-count registers load into the FIFO. The EOF signal increments the FIFO. If the FIFO overflows, the RR7 bit 7 (FIFO overflow) is set, indicating the overflow. This bit and the FIFO control logic is reset by disabling and re-enabling the FIFO control bit (WR15 bit 2). For details about FIFO control timing during an SDLC frame, see Figure 16.

Figure 16. SDLC Byte Counting Detail

#### SDLC Status FIFO Anti-Lock Feature

When the Frame Status FIFO is enabled and the ESCC is programmed for Special Receive Condition Only (WR1 bit 4 = bit 3=1), the data FIFO is not locked when a character with EOF status is read. When EOF status is at the top of the FIFO, an interrupt with a vector for receive data is generated. The command Reset Highest IUS must be issued at the end of the ISR regardless of whether an Interrupt Acknowledge cycle was executed (hardware or software).

This action allows the DMA to complete the transfer of the received frame to memory, then interrupt the CPU that a frame was completed, without locking the FIFO. Because in the RECEIVE INTERRUPT ON SPECIAL CONDITION ONLY mode the interrupt vector for receive data is not used, it indicates that the last byte of a frame has been read from the receive FIFO. Reading the frame status (CRC, byte count and other status stored in the status FIFO) determines that EOF is not required.

When a character with a special receive condition other than EOF is received (receiver overrun or parity), a special receive condition interrupt is generated after the character is read from the FIFO and the receive FIFO is locked until the Error Reset command is issued.

# **Programming**

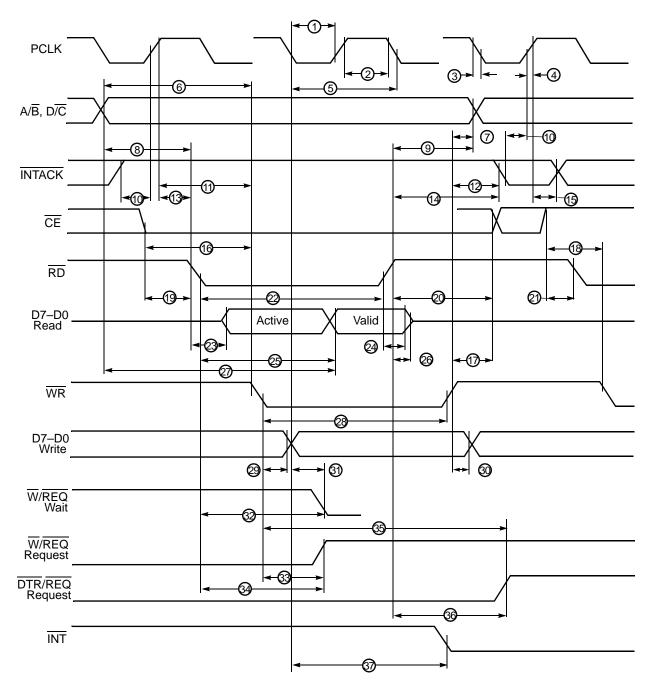

The ESCC contains write registers in each channel that are programmed by the system separately to configure the function of each channel.

In the Z85230/L ESCC, the data FIFOs are directly accessible by selecting a High on the  $D/\overline{C}$  pin. Except WR0 and RR0, programming the write registers requires two write operations and reading a read register requires a write and a read operation. The first Write is to WR0 which contains bits that point to the selected register. If the next operation is a Write the selected write register is written. If the next operation is a read, the selected read register is read. The pointer bits are automatically cleared after the second operation so the next read or write comes from RR0 or goes to WR0. It is not necessary to write 00 to WR0 to access WR0 or RR0.

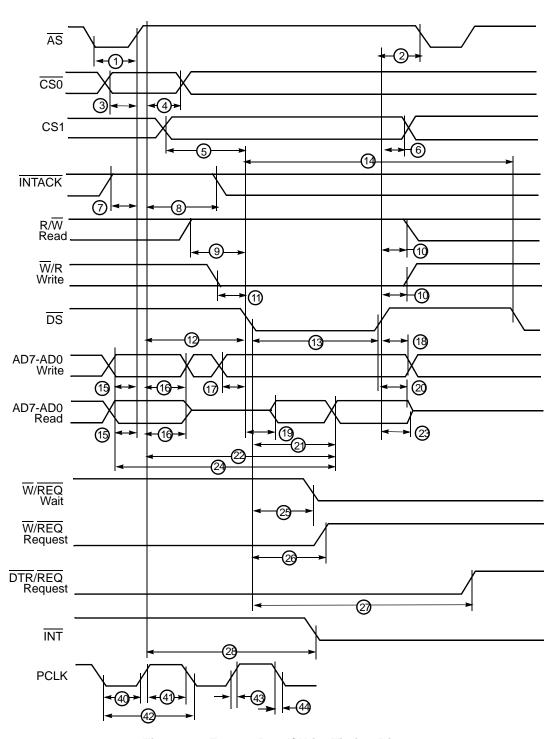

For the Z80230 ESCC, the registers are directly addressable. A command issued to WR0B determines how the ESCC decodes the address placed on the address/data bus at the beginning of a Read or Write cycle. In Shift Right mode the channel select  $A/\overline{B}$  is taken from AD0 and the state of AD5 is ignored. In Shift Left mode, the channel select  $A/\overline{B}$  is taken from AD5 and the state of AD0 is ignored. AD7 and AD6 are always ignored as address bits and the register address itself occupies AD4–AD1.

#### Initializing

The software first issues a series of commands to initialize the basic mode of operation. These commands are followed by other commands to qualify conditions within the selected mode. For example, in the ASYNCHRONOUS mode, character length, clock rate, number of stop bits, and even and odd parity is set first. Next, the INTERRUPT mode is set. Finally, the receiver and transmitter are enabled.

# Write Registers

The ESCC contains 16 write registers (17 counting the transmit buffer) in each channel. These write registers are programmed to configure the function of the channel. There are two registers (WR2 and WR9) shared by the two channels, which can be accessed through either of them. WR2 contains the interrupt vector for both channels. WR9 contains the interrupt control bits and reset commands. Register WR7' can be written to if WR15 bit 0 is 1.

#### **Z80X20 Register Access**

The Z80230 registers are addressed using the address on AD7–AD0 which are latched by the rising edge of  $\overline{AS}$ . The Shift Right/Shift Left bit in the Channel B WR0 controls which

bits are decoded to form the register address. This bit is placed in this register to simplify programming when the current state of the Shift right/Shift Left bit is not known.

A hardware reset forces SHIFT LEFT mode where the address is decoded from AD5–AD0. In SHIFT RIGHT mode, the address is decoded from AD4–AD0. The Shift Right/Shift Left bit is written using a command to make the software writing to WR0 independent of the state of the Shift Right/Shift Left bit.

While in the SHIFT LEFT mode, the register address is placed on AD4–AD0 and the Channel Select bit  $A/\overline{B}$ , is decoded from AD5. In SHIFT RIGHT mode, the register address is again placed on AD4–AD1 but the Channel Select  $A/\overline{B}$  is decoded from AD0.

Since Z80230 does not contain 16 read registers, the decoding of the read registers is not complete; this state is listed in Table 4 on page 23 and Table 5 by parentheses around the register name. These addresses may also be used to access the read registers. The Z80230 contains only one WR2 and WR9; these registers may be written from either channel.

SHIFT LEFT mode is used when Channel A and B are programmed differently. Using SHIFT LEFT mode allows the software to sequence through the registers of one channel at a time. The SHIFT RIGHT mode is used when the channels are programmed the same. By incrementing the address, you can program the same data value into both Channel A and Channel B registers.

Table 5 lists details of the Z80X30 Register Map in SHIFT LEFT Mode.

Table 5. Z80230 Register Map (Shift Left Mode)

| AD5 | AD4 | AD3 | AD2 | AD1 | Write | 80230<br>WR15 D2=0 | 80230<br>WR15 D2=1 | 80230<br>WR15 D2=1<br>WR7' D6=1 |

|-----|-----|-----|-----|-----|-------|--------------------|--------------------|---------------------------------|

| 0   | 0   | 0   | 0   | 0   | WR08  | RR0B               | RR0B               | RR08                            |

| 0   | 0   | 0   | 0   | 1   | WR1B  | RR1B               | RR1B               | RR1B                            |

| 0   | 0   | 0   | 1   | 0   | WR2   | RR2B               | RR2B               | RR2B                            |

| 0   | 0   | 0   | 1   | 1   | WR3B  | RR3B               | RR3B               | RR3B                            |

| 0   | 0   | 1   | 0   | 0   | WR4B  | (RR0B)             | (RR0B)             | (WR4B)                          |