# zilog

# SCC/ESCC

## **User Manual**

UM010904-0318

Copyright © 2018 by Zilog<sup>®</sup>, Inc. All rights reserved. www.zilog.com

Warning: DO NOT USE IN LIFE SUPPORT

### LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

#### As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

#### **Document Disclaimer**

©2018 by Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

Z8, Z80 are registered trademarks of Zilog, Inc. All other product or service names are the property of their respective owners.

SCC/ESCC User Manual Zilog

# **Revision History**

Each instance in Revision History reflects a change to this document from its previous revision. For more details, refer to the corresponding pages and appropriate links in the table below.

|            | Revision |                                     |                |

|------------|----------|-------------------------------------|----------------|

| Date       | Level    | Description                         | Page No        |

| March 2018 | 04       | Added missing images                | 212, 213, 217, |

|            |          |                                     | 218, 220, 222, |

|            |          |                                     | 227, 230, 234, |

|            |          |                                     | 236, 244       |

| May 2015   | 03       | Updated /SYNCA and /SYNCB           | 14             |

| -          |          | Updated /RTxCA, /RTxCB              | 15             |

|            |          | Updated Data Encoding Method Figure | 75             |

| June 2009  | 02       | Added Low Voltage ESCC information  | All            |

| May 2009   | 01       | Original Document                   | All            |

SCC/ESCC User Manual

# **Table of Contents**

| General Description                               |     |

|---------------------------------------------------|-----|

|                                                   | . 1 |

| SCC's Capabilities                                |     |

| Block Diagram                                     | . 5 |

| Pin Descriptions                                  | . 7 |

| Pin Descriptions                                  | 9   |

| Pins Common to both Z85X30 and Z80X30             | 13  |

| Pin Descriptions, (Z85X30 Only)                   |     |

| Pin Descriptions, (Z80X30 Only)                   | 16  |

| Interfacing the SCC/ESCC                          | 17  |

| Introduction                                      | 17  |

| Z80X30 Interface Timing                           | 17  |

| Z80X30 Read Cycle Timing                          | 17  |

| Z80X30 Write Cycle Timing                         | 18  |

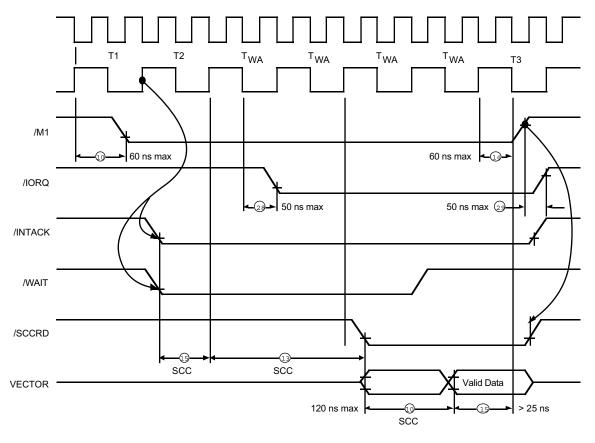

| Z80X30 Interrupt Acknowledge Cycle Timing         | 19  |

| Z80X30 Register Access                            | 21  |

| Z80C30 Register Enhancement                       |     |

| Z80230 Register Enhancements                      |     |

| Z80X30 Reset                                      |     |

| Z85X30 Interface Timing                           |     |

| Z85X30 Read Cycle Timing                          |     |

| Z85X30 Write Cycle Timing                         |     |

| Z85X30 Interrupt Acknowledge Cycle Timing         |     |

| Z85X30 Register Access                            |     |

| Z85C30 Register Enhancement                       |     |

| Z85C30/Z85230/L Register Enhancements             |     |

| Z85X30 Reset                                      |     |

|                                                   |     |

| I/O Programming Introduction                      |     |

| Polling                                           |     |

| Interrupts                                        |     |

| Interrupt Control                                 |     |

| Daisy-Chain Resolution                            |     |

| Interrupt Acknowledge                             |     |

| The Receiver Interrupt                            |     |

| Transmit Interrupts and Transmit Buffer Empty Bit | 49  |

# SCC/ESCC User Manual Zilog

| External/Status Interrupts                |      |

|-------------------------------------------|------|

| Block/DMA Transfer                        | . 60 |

| Block Transfers                           | . 60 |

| DMA Requests                              | . 63 |

| Test Functions                            | . 69 |

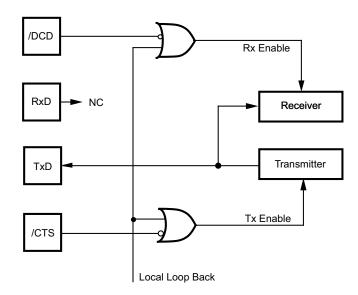

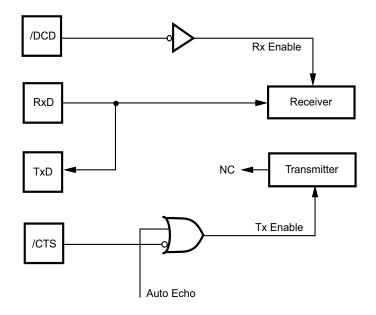

| Local Loopback                            | . 69 |

| Auto Echo                                 | . 69 |

| SCC/ESCC Ancillary Support Circuitry      | . 71 |

| Introduction                              | . 71 |

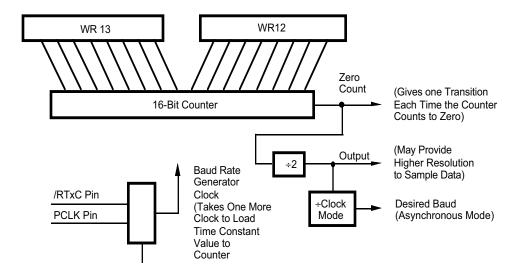

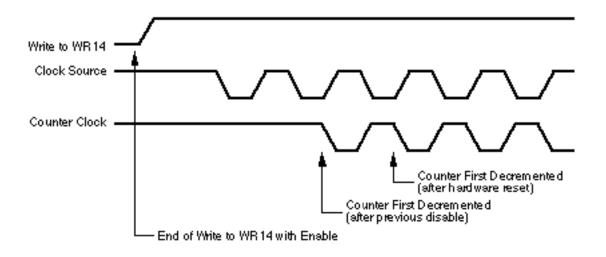

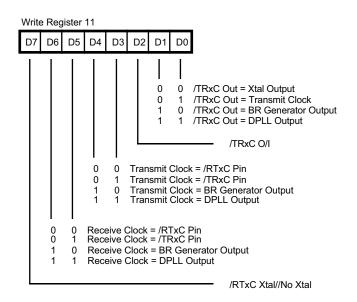

| Baud Rate Generator                       | . 71 |

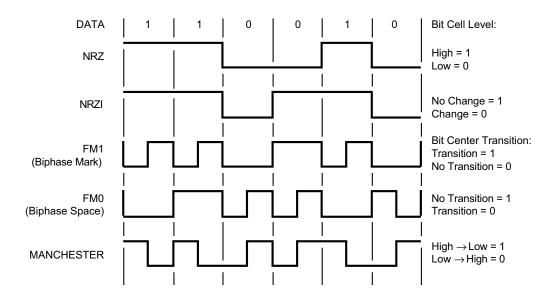

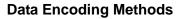

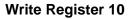

| Data Encoding/Decoding                    | . 74 |

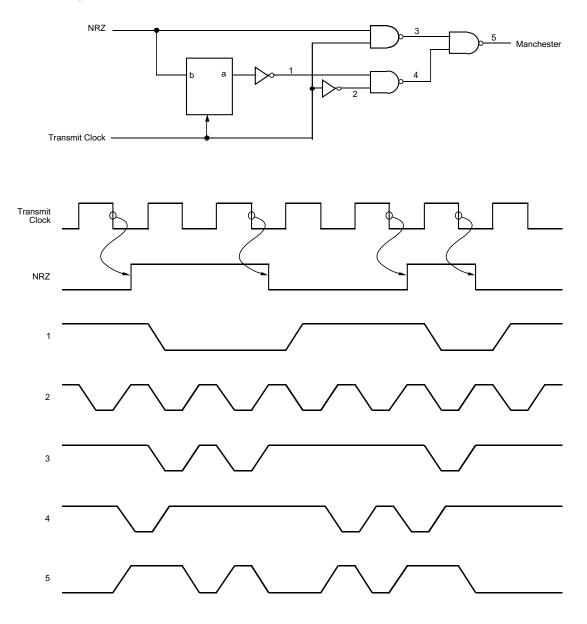

| DPLL Digital Phase-Locked Loop            |      |

| DPLL Operation in the NRZI Mode           |      |

| DPLL Operation in the FM Modes            |      |

| DPLL Operation in the Manchester Mode     |      |

| Transmit Clock Counter (ESCC only)        |      |

| Clock Selection                           |      |

| Crystal Oscillator                        |      |

| Data Communication Modes                  | . 88 |

| Introduction                              |      |

| Transmit Data Path Description            |      |

| Receive Data Path Description             |      |

| Asynchronous Mode                         |      |

| Asynchronous Transmit                     |      |

| Asynchronous Receive                      |      |

| Asynchronous Initialization               |      |

| Byte-Oriented Synchronous Mode            |      |

| Byte-Oriented Synchronous Transmit        |      |

| Byte-Oriented Synchronous Receive         |      |

| Transmitter/Receiver Synchronization      |      |

| Bit-oriented Synchronous (SDLC/HDLC) Mode |      |

| SDLC Transmit                             |      |

| SDLC Receive                              |      |

| SDLC Frame Status FIFO                    |      |

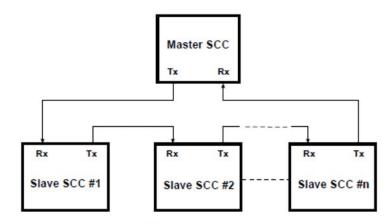

| SDLC Loop Mode                            |      |

|                                           |      |

| Register Descriptions                     |      |

|                                           |      |

| Write Registers                           |      |

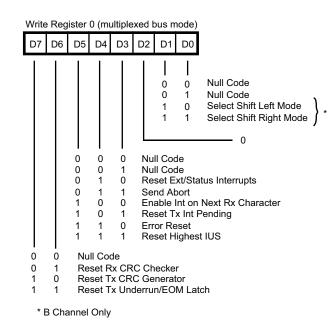

| Write Register 0 (Command Register)       | 139  |

# SCC/ESCC User Manual Zilog <sub>vi</sub>

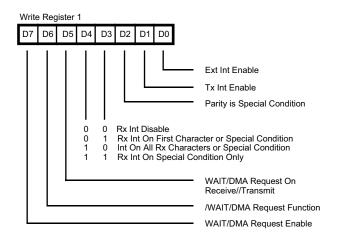

| Write Register 1 (Transmit/Receive Interrupt and Data Transfer Mode Definition) | 142 |

|---------------------------------------------------------------------------------|-----|

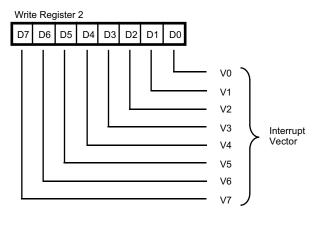

| Write Register 2 (Interrupt Vector)                                             |     |

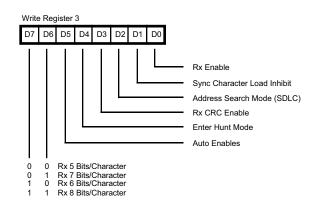

| Write Register 3 (Receive Parameters and Control)                               |     |

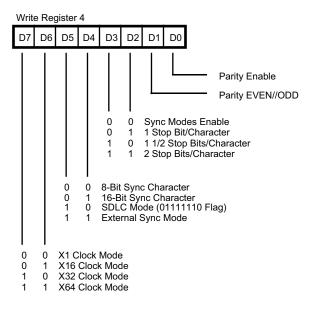

| Write Register 4 (Transmit/Receive Miscellaneous Parameters                     |     |

| and Modes)                                                                      | 150 |

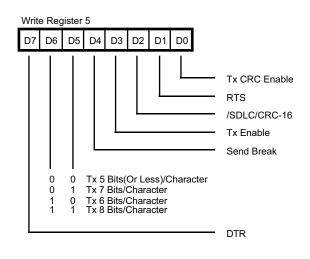

| Write Register 5 (Transmit Parameters and Controls)                             | 152 |

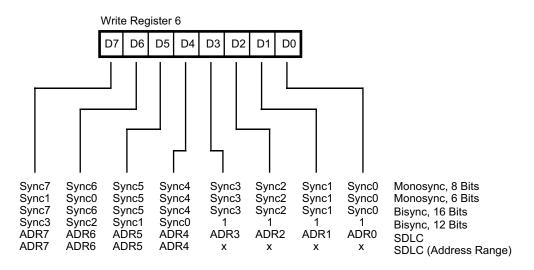

| Write Register 6 (Sync Characters or SDLC Address Field) 154                    |     |

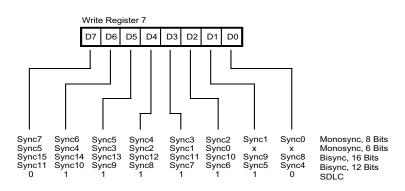

| Write Register 7 (Sync Character or SDLC Flag)                                  |     |

| Write Register 7 Prime (ESCC only)                                              | 155 |

| Write Register 7 Prime (85C30 Only)                                             | 157 |

| Write Register 8 (Transmit Buffer)                                              |     |

| Write Register 9 (Master Interrupt Control)                                     |     |

| Write Register 10 (Miscellaneous Transmitter/Receiver Control Bits)             |     |

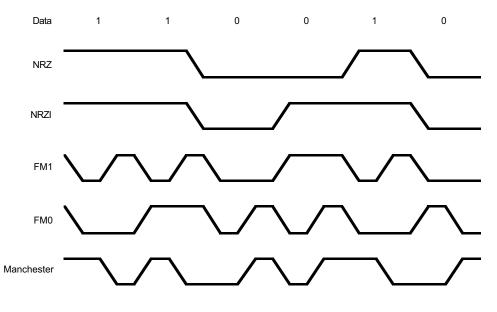

| Write Register 11 (Clock Mode Control)                                          |     |

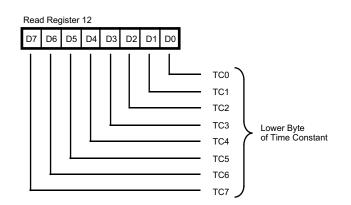

| Write Register 12 (Lower Byte of Baud Rate Generator Time Constant)             | 167 |

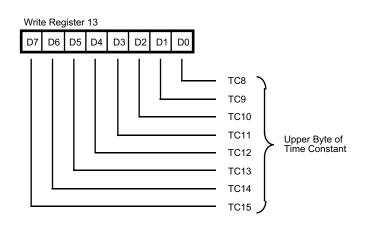

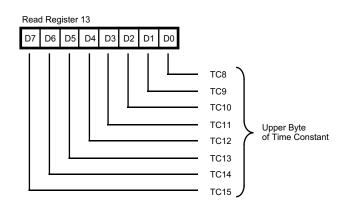

| Write Register 13 (Upper Byte of Baud Rate Generator Time Constant)             |     |

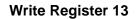

| Write Register 14 (Miscellaneous Control Bits)                                  |     |

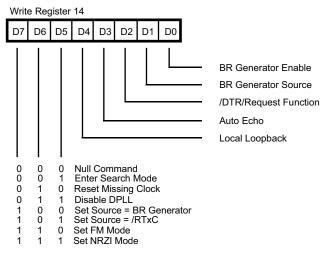

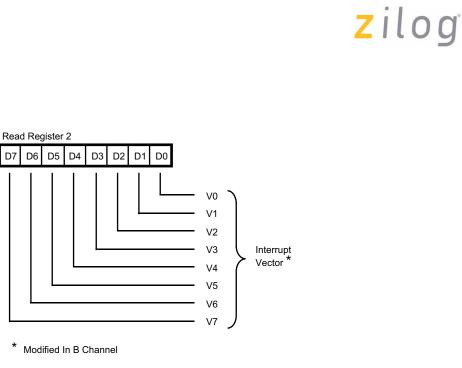

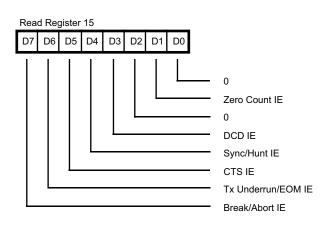

| Write Register 15 (External/Status Interrupt Control)                           | 172 |

| ······································                                          | 174 |

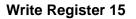

| Read Register 0 (Transmit/Receive Buffer Status and External Status) 1          |     |

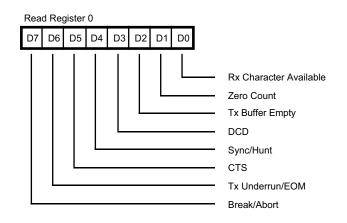

| Read Register 1                                                                 | 178 |

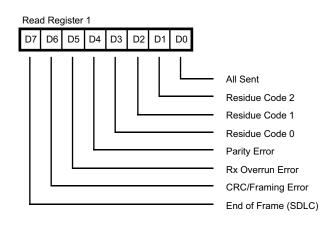

| Read Register 2                                                                 | 180 |

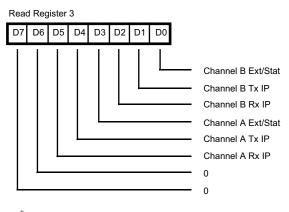

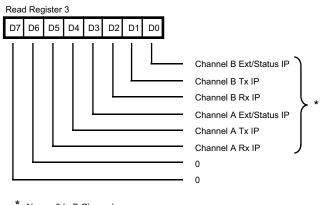

| Read Register 3                                                                 | 181 |

| Read Register 4 (ESCC and 85C30 Only)                                           |     |

| Read Register 5 (ESCC and 85C30 Only)                                           |     |

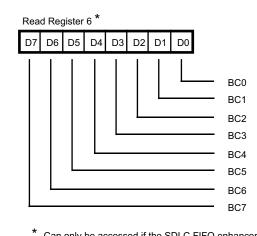

| Read Register 6 (Not on NMOS)                                                   |     |

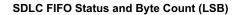

| Read Register 7 (Not on NMOS)                                                   |     |

| Read Register 8                                                                 |     |

| Read Register 9 (ESCC and 85C30 Only)                                           |     |

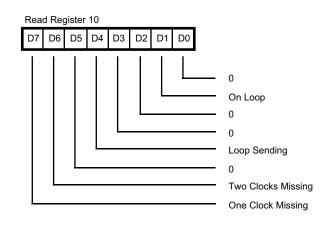

| Read Register 10                                                                |     |

| Read Register 11 (ESCC and 85C30 Only)                                          |     |

| Read Register 12                                                                |     |

| Read Register 13                                                                |     |

| Read Register 14 (ESCC and 85C30 Only)                                          | 187 |

| Read Register 15 187                                                            |     |

## **Application Notes188**

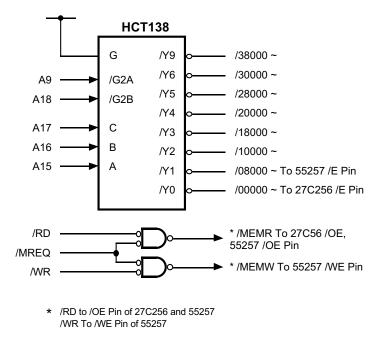

| Interfacing Z80® CPUs to the Z8500 Peripheral Family | 188 |

|------------------------------------------------------|-----|

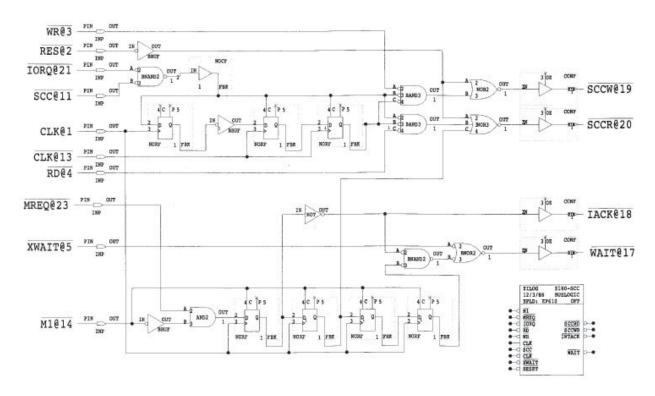

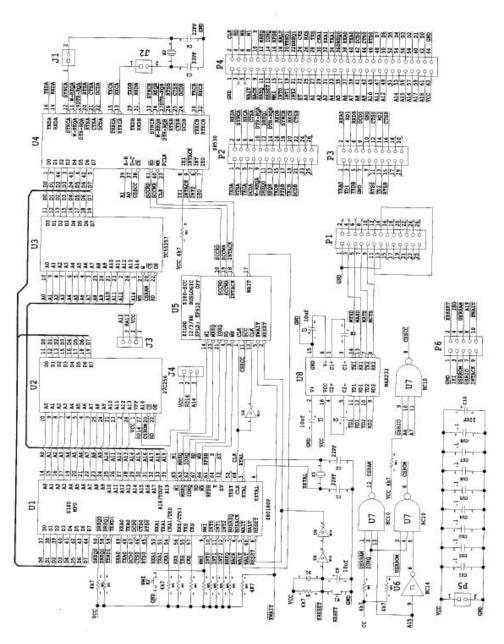

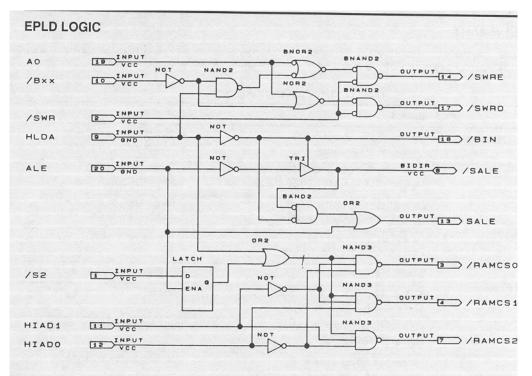

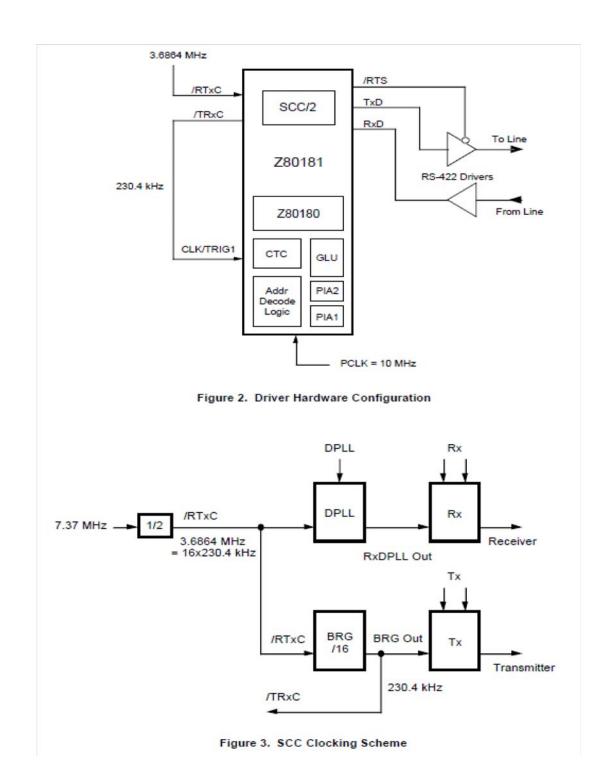

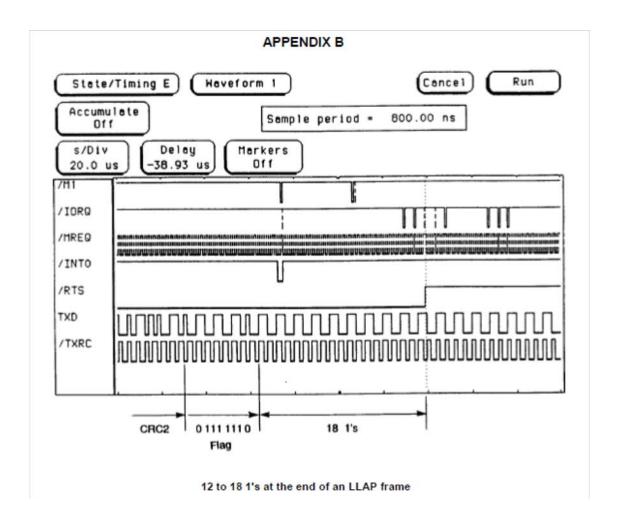

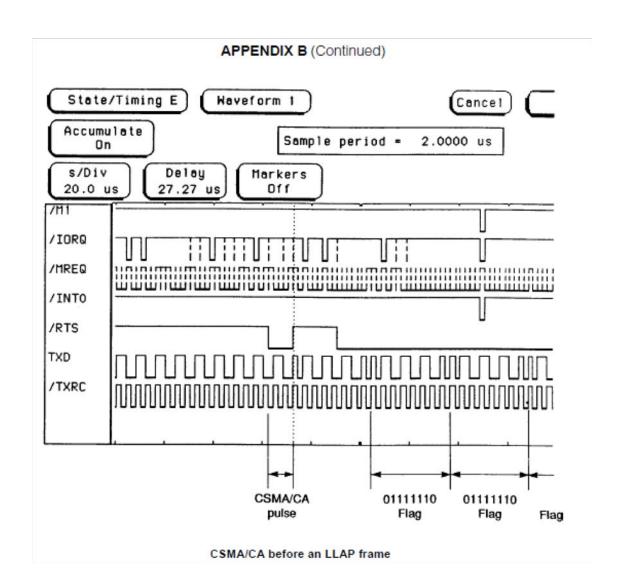

| AN0096: The Z180 Interfaced with the SCC at 10 MHz   | 210 |

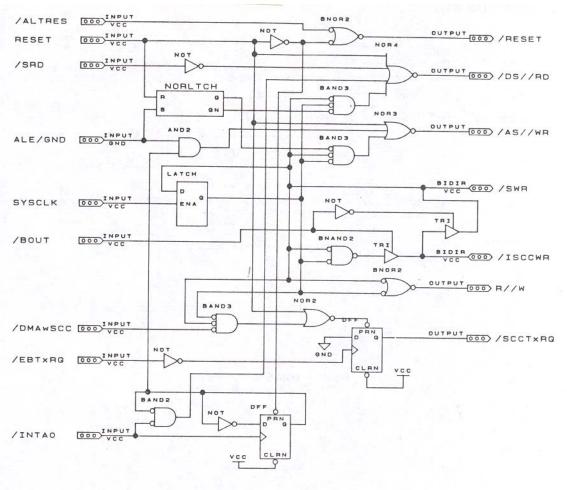

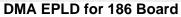

| AN0097: The Zilog® Datacom Family with the 80186 CPU | 250 |

# SCC/ESCC User Manual Zilog <sub>vii</sub>

| SCC in Binary Synchronous Communications                                 |

|--------------------------------------------------------------------------|

| Serial Communication Controller (SCC): SDLC Mode of Operation 288        |

| Using SCC with Z8000 in SDLC Protocol                                    |

| AN0300: Boost Your System Performance Using the Zilog ESCC<br>Controller |

| AN006: Technical Considerations When Implementing Localtalk Link Access  |

| Protocol                                                                 |

| AN0075: On-Chip Oscillator Design                                        |

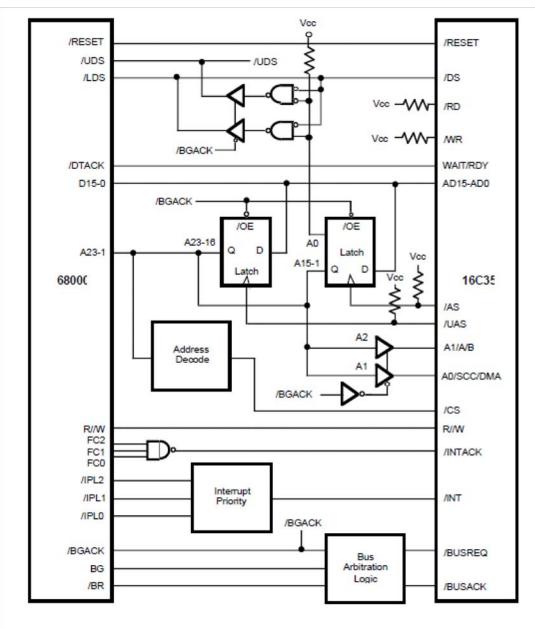

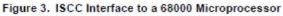

| Interfacing the ISCC to the 68000 and 8086                               |

| Zilog SCC Z8030/Z8530 Questions and Answers                              |

| Zilog ESCC Controller Questions and Answers                              |

| Questions and Answers                                                    |

| Zilog SCC Z8030/Z8530 Questions and Answers                              |

| Zilog ESCC Controller Questions and Answers                              |

| Customer Support                                                         |

# **General Description**

## Introduction

Zilog's SCC Serial Communication Controller is a dual channel, multiprotocol data communication peripheral designed for use with 8- and 16-bit microprocessors. The SCC functions as a serialto-parallel, parallel-to-serial converter/controller. The SCC can be software-configured to satisfy a wide variety of serial communications applications. The device contains a variety of new, sophisticated internal functions including on-chip baud rate generators, digital phase-lock loops, and crystal oscillators, which dramatically reduce the need for external logic.

The SCC handles asynchronous formats, synchronous byte-oriented protocols such as IBM Bisync, and synchronous bit-oriented protocols such as HDLC and IBM SDLC. This versatile device supports virtually any serial data transfer application (telecommunication, LAN, etc.).

The device can generate and check CRC codes in any synchronous mode and can be programmed to check data integrity in various modes. The SCC also has facilities for modem control in both channels. In applications where these controls are not needed, the modem controls can be used for general-purpose I/O.

With access to 14 Write registers and 7 Read registers per channel (the number of the registers varies depending on the version), the user can configure the SCC to handle all synchronous formats regardless of data size, number of stop bits, or parity requirements.

Within each operating mode, the SCC also allows for protocol variations by checking odd or even parity bits, character insertion or deletion, CRC generation, checking break and abort generation and detection, and many other protocol-dependent features.

|                  | Z-Bus  | Universal-Bus |

|------------------|--------|---------------|

| NMOS             | Z8030  | Z8530         |

| CMOS             | Z80C30 | Z85C30        |

| ESCC             | Z80230 | Z85230/Z8523L |

| EMSCC            |        | Z85233        |

| Low Voltage ESCC |        | Z8523L        |

|                  |        |               |

The SCC/ESCC family consists of the following eight devices;

As a convention, use the following words to distinguish the devices throughout this document. **SCC:** Description applies to all versions.

**NMOS:** Description applies to NMOS version (Z8030/Z8530)

CMOS: Description applies to CMOS version (Z80C30/Z85C30)

ESCC: Description applies to ESCC (Z80230/Z85230/Z8523L)

EMSCC: Description applies to EMSCC (Z85233)

**Z80X30:** Description applies to Z-Bus version of the device (Z8030/Z80C30/Z80230)

**Z85X3X:** Description applies to Universal version of the device (Z8530/Z85C30/Z85230/ Z8523L/Z85233)

The Z-Bus version has a multiplexed bus interface and is directly compatible with the Z8000, Z16C00, and 80x86 CPUs. The Universal version has a non-multiplexed bus interface and easily interfaces with virtually any CPU, including the 8080,  $Z80^{\$}$ , 68X00.

## SCC's Capabilities

The NMOS version of the SCC is Zilog's original device. The design is based on the Z80 SIO architecture. If you are familiar with the Z80 SIO, the SCC can be treated as an SIO with support circuitry such as DPLL, BRG, etc. Its features include:

- Two independent full-duplex channels

- Synchronous/Isosynchronous data rates:

- Up to 1/4 of the PCLK using external clock source

- Up to 5 Mbits/sec at 20 MHz PCLK (ESCC)

- Up to 4 Mbits/sec at 16 MHz PCLK (CMOS)

- Up to 2 Mbits/sec at 8 MHz PCLK (NMOS)

- Up to 1/8 of the PCLK (up to 1/16 on NMOS) using FM encoding with DPLL

- Up to 1/16 of the PCLK (up to 1/32 on NMOS) using NRZI encoding with DPLL

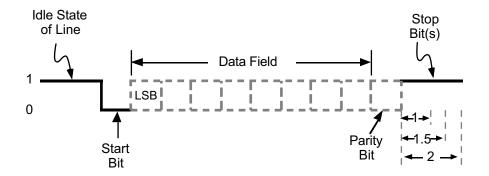

- Asynchronous Capabilities

- 5, 6, 7 or 8 bits/character (capable of handling 4 bits/character or less.)

- 1, 1.5, or 2 stop bits

- Odd or even parity

- Times 1, 16, 32 or 64 clock modes

- Break generation and detection

- Parity, overrun and framing error detection

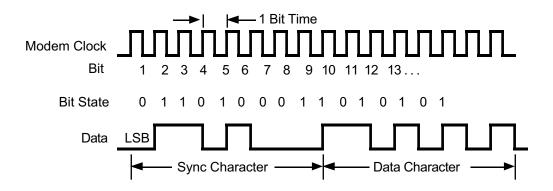

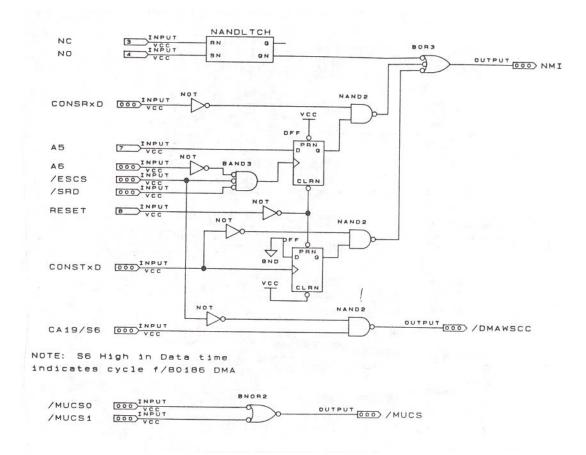

- Byte oriented synchronous capabilities:

- Internal or external character synchronization

- One or two sync characters (6 or 8 bits/sync character) in separate registers

- Automatic Cyclic Redundancy Check (CRC) generation/detection

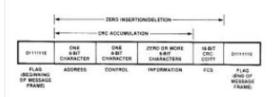

- SDLC/HDLC capabilities:

- Abort sequence generation and checking

- Automatic zero insertion and detection

- Automatic flag insertion between messages

- Address field recognition

- I-field residue handling

- CRC generation/detection

- SDLC loop mode with EOP recognition/loop entry and exit

- Receiver FIFO

ESCC: 8 bytes deep

NMOS/CMOS: 3 bytes deep

• Transmitter FIFO

ESCC: 4 bytes deep

NMOS/CMOS: 1 byte deep

- NRZ, NRZI or FM encoding/decoding. Manchester code decoding (encoding with external logic)

- Baud Rate Generator in each channel

- Digital Phase Locked Loop (DPLL) for clock recovery

- Crystal oscillator

The CMOS version of the SCC is 100% plug in compatible to the NMOS versions of the device, while providing the following additional features:

- Status FIFO

- Software interrupt acknowledge feature

- Enhanced timing specifications

- Faster system clock speed

- Designed in Zilog's Superintegration<sup>TM</sup> core format

- When the DPLL clock source is external, it can be up to 2x the PCLK, where NMOS allows up to PCLK (32.3 MHz max with 16/20 MHz version).

The Z85C30 CMOS SCC has added new features, while maintaining 100% hardware/software compatibility. It has the following new features:

- New programmable WR7' (write register 7 prime) to enable new features.

- Improvements to support SDLC mode of synchronous communication:

- Improved functionality to ease sending back-to back frames

- Automatic SDLC opening Flag transmission\*

- Automatic Tx Underrun/EOM Latch reset in SDLC mode\*

- Automatic /RTS deactivation\*

- TxD pin forced "H" in SDLC NRZI mode after closing flag\*

- Complete CRC reception\*

- Improved response to Abort sequence in status FIFO

- Automatic Tx CRC generator preset/reset

- Extended read for write registers\*

- Write data setup timing improvement

- Improved AC timing:

- Three to 3.5 PCLK access recovery time.

- Programmable /DTR//REQ timing\*

- Elimination of write data to falling edge of /WR setup time requirement

- Reduced /INT timing

- Other features include:

- Extended read function to read back the written value to the write registers\*

- Latching RR0 during read

- RR0, bit D7 and RR10, bit D6 now has reset default value

Some of the features listed above are available by default, and some of them (features with "\*") are disabled on default.

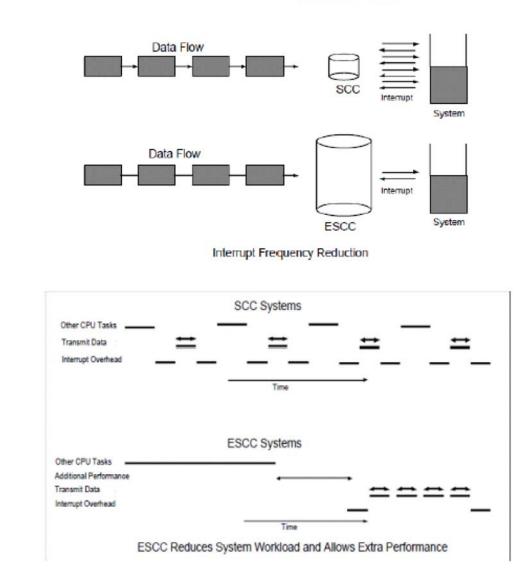

ESCC (Enhanced SCC) is pin and software compatible to the CMOS version, with the following additional enhancements.

- Deeper transmit FIFO (4 bytes)

- Deeper receive FIFO (8 bytes)

- Programmable FIFO interrupt and DMA request level

- Seven enhancements to improve SDLC link layer supports:

- Automatic transmission of the opening flag

- Automatic reset of Tx Underrun/EOM latch

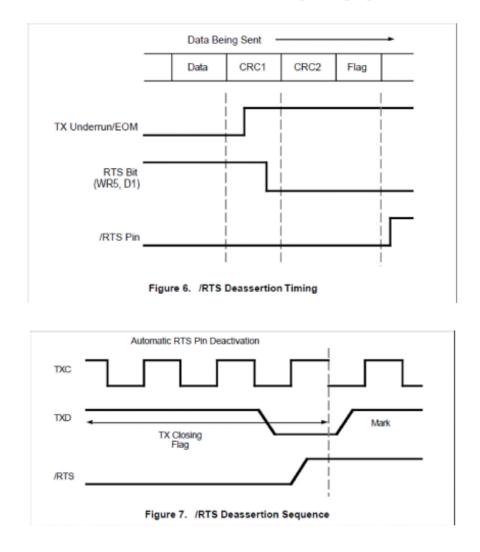

- Deactivation of /RTS pin after closing flag

- Automatic CRC generator preset

- Complete CRC reception

- TxD pin automatically forced high with NRZI encoding when using mark idle

- Status FIFO handles better frames with an ABORT

- Receive FIFO automatically unlocked for special receive interrupts when using the SDLC status FIFO

- Delayed bus latching for easier microprocessor interface

- New programmable features added with Write Register 7' (WR seven prime)

- Write registers 3, 4, 5 and 10 are now readable

- Read register 0 latched during access

- DPLL counter output available as jitter-free transmitter clock source

- Enhanced /DTR, /RTS deactivation timing

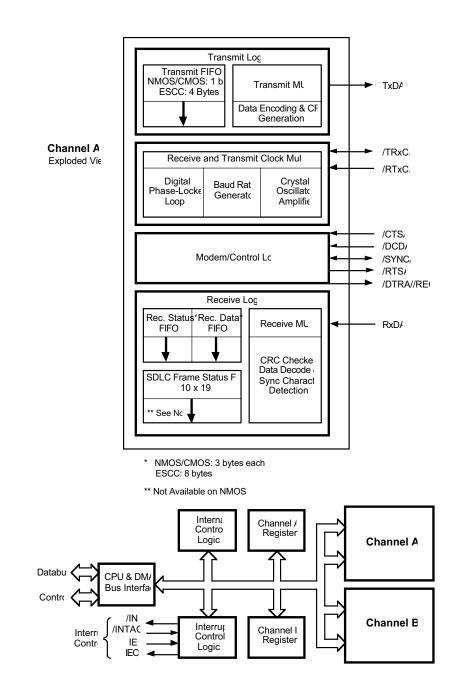

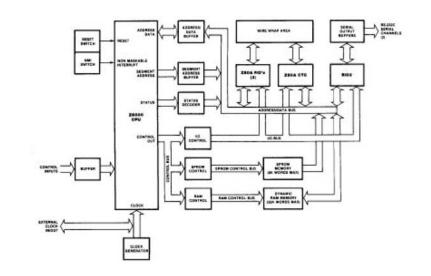

## **Block Diagram**

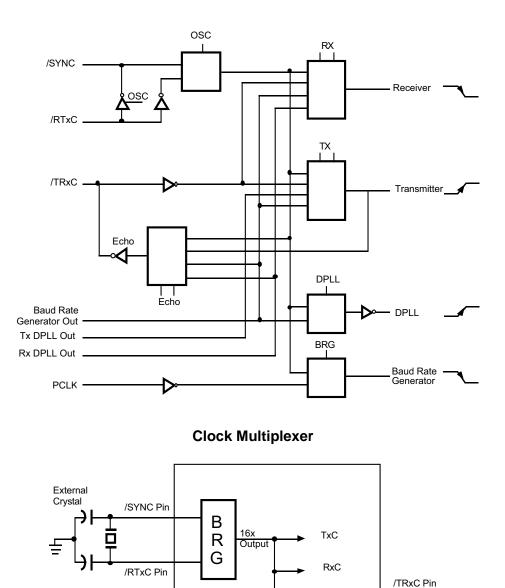

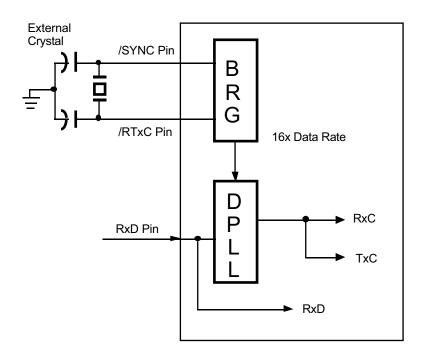

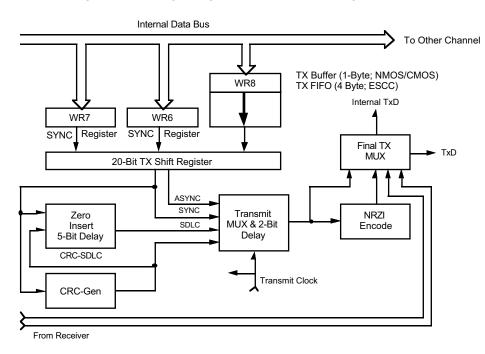

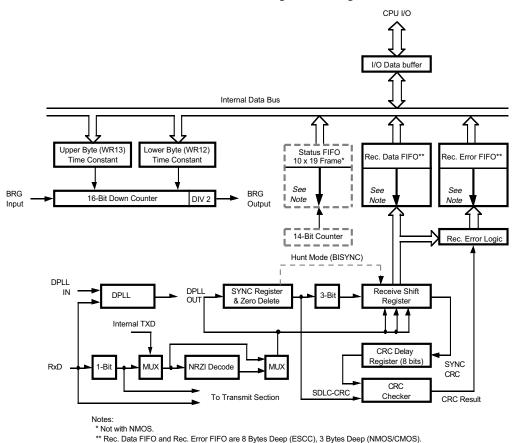

Figure on page 6 displays the block diagram of the SCC. Note that the depth of the FIFO differs depending on the version. The 10X19 SDLC Frame Status FIFO is not available on the NMOS version of the SCC. Detailed internal signal path will be discussed in Data Communication Modes on page 88.

SCC/ESCC User Manual Zilog<sup>°</sup>

SCC Block Diagram

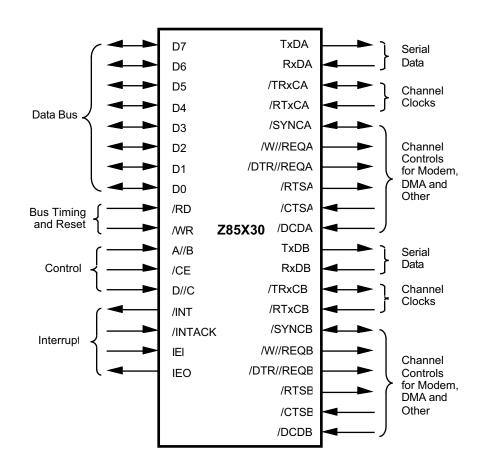

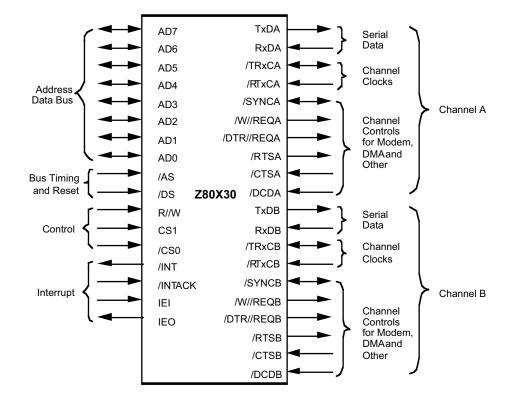

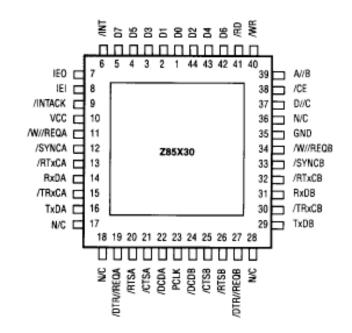

## **Pin Descriptions**

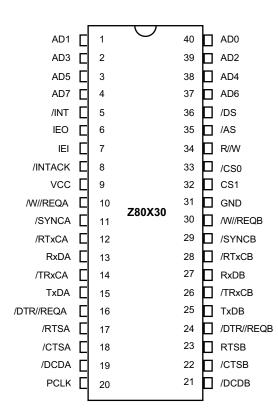

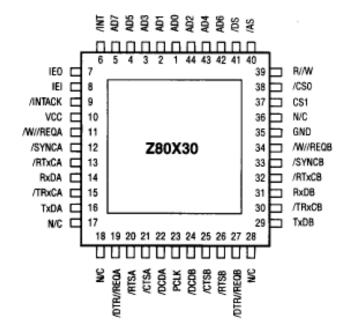

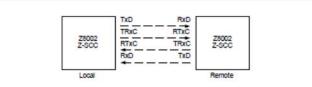

The SCC pins are divided into seven functional groups: Address/Data, Bus Timing and Reset, Device Control, Interrupt, Serial Data (both channels), Peripheral Control (both channels), and Clocks (both channels). Figure on page 8 and Figure on page 9 display the pins in each functional group for both Z80X30 and Z85X30. Notice the pin functions unique to each bus interface version in the Address/Data group, Bus Timing and Reset group, and Control groups.

The Address/Data group consists of the bidirectional lines used to transfer data between the CPU and the SCC (Addresses in the Z80X30 are latched by /AS). The direction of these lines depends on whether the operation is a Read or Write.

The timing and control groups designate the type of transaction to occur and when it will occur. The interrupt group provides inputs and outputs to conform to the Z-Bus<sup>®</sup> specifications for handling and prioritizing interrupts. The remaining groups are divided into channel A and channel B groups for serial data (transmit or receive), peripheral control (such as DMA or modem), and the input and output lines for the receive and transmit clocks.

8

The signal functionality and pin assignments (Figure on page 10 through Figure on page 13) stay constant within the same bus interface group (i.e., Z80X30, Z85X30), except for some timing and/ or DC specification differences. For details, refer the individual product specifications.

**Z85X30 Pin Functions**

User Manual

SCC/ESCC

## **Pin Descriptions**

**Z80x30 Pin Functions**

SCC/ESCC User Manual

zilog<sup>°</sup>

|            |   |    |            |    | - |            |

|------------|---|----|------------|----|---|------------|

| D1         |   | 1  | $\bigcirc$ | 40 | þ | D0         |

| D3         |   | 2  |            | 39 | þ | D2         |

| D5         |   | 3  |            | 38 | þ | D4         |

| D7         |   | 4  |            | 37 | þ | D6         |

| /INT       |   | 5  |            | 36 | þ | /RD        |

| IEO        | С | 6  |            | 35 | þ | <b>WR</b>  |

| IEI        | П | 7  |            | 34 | Þ | A//B       |

| /INTACK    | Ц | 8  |            | 33 | þ | /CE        |

| VCC        | С | 9  |            | 32 | Þ | D//C       |

| /W//REQA   | Ц | 10 | Z85X30     | 31 | þ | GND        |

| /SYNCA     | С | 11 | 200830     | 30 | Þ | /W//REQB   |

| /RTxCA     | Ц | 12 |            | 29 | Þ | /SYNCB     |

| RxDA       | С | 13 |            | 28 | Þ | /RTxCB     |

| /TRxCA     | С | 14 |            | 27 | Þ | RxDB       |

| TxDA       | Γ | 15 |            | 26 | Þ | /TRxCB     |

| /DTR//REQA |   | 16 |            | 25 | Þ | TxDB       |

| /RTSA      | Γ | 17 |            | 24 | Þ | /DTR//REQB |

| /CTSA      |   | 18 |            | 23 | Þ | RTSB       |

| /DCDA      | Ц | 19 |            | 22 | Þ | /CTSB      |

| PCLK       | Ц | 20 |            | 21 | þ | /DCDB      |

|            | L |    |            |    |   |            |

Z85X30 DIP Pin Assignments

SCC/ESCC User Manual Zilog

Z85X30 PLCC Pin Assignments

SCC/ESCC **User Manual** zilog

SCC/ESCC User Manual Zilog <sub>13</sub>

#### Z80X30 PLCC Pin Assignments

## Pins Common to both Z85X30 and Z80X30

**/CTSA, /CTSB.** Clear To Send (inputs, active Low). These pins function as transmitter enables if they are programmed for Auto Enable (WR3, D5=1). A Low on the inputs enables the respective transmitters. If not programmed as Auto Enable, they may be used as general-purpose inputs. Both inputs are Schmitt-trigger buffered to accommodate slow rise-time inputs. The SCC detects pulses on these inputs and can interrupt the CPU on both logic level transitions.

**/DCDA**, **/DCDB**. Data Carrier Detect (inputs, active Low). These pins function as receiver enables if they are programmed for Auto Enable (WR3, D5=1); otherwise, they are used as general-purpose input pins. Both pins are Schmitt-trigger buffered to accommodate slow rise time signals. The SCC detects pulses on these pins and can interrupt the CPU on both logic level transitions.

**/RTSA, /RTSB.** Request To Send (outputs, active Low). The /RTS pins can be used as generalpurpose outputs or with the Auto Enable feature. When used with Auto Enable ON (WR3, D5=1) in asynchronous mode, the /RTS pin goes High after the transmitter is empty. When Auto Enable is OFF, the /RTS pins are used as general-purpose outputs, and, they strictly follow the inverse state of WR5, bit D1.

ESCC and 85C30:

In SDLC mode, the /RTS pins can be programmed to be deasserted when the closing flag of the message clears the TxD pin, if WR7' D2 is set.

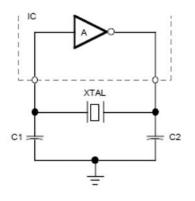

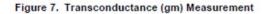

**/SYNCA**, **/SYNCB**. Synchronization (inputs or outputs, active Low). These pins can act either as inputs, outputs, or part of the crystal oscillator circuit. In the Asynchronous Receive mode (crystal oscillator option not selected), these pins are inputs similar to CTS and DCD. In this mode, transitions on these lines affect the state of the Synchronous/Hunt status bits in Read Register 0 but have no other function. With the crystal oscillator option selected, these /SYNCA, /SYNCB pins becomes the oscillator Xout pins and /RTxCA, /RTxCB.becomes the Xin pins, respectively.

In External Synchronization mode, with the crystal oscillator not selected, these lines also act as inputs. In this mode, /SYNC is driven Low to receive clock cycles after the last bit in the synchronous character is received. Character assembly begins on the rising edge of the receive clock immediately preceding the activation of SYNC.

In the Internal Synchronization mode (Monosync and Bisync) with the crystal oscillator not selected, these pins act as outputs and are active only during the part of the receive clock cycle in which the synchronous condition is not latched. These outputs are active each time a synchronization pattern is recognized (regardless of character boundaries). In SDLC mode, the pins act as outputs and are valid on receipt of a flag. The /SYNC pins switch from input to output when monosync, bisync, or SDLC is programmed in WR4 and sync modes are enabled.

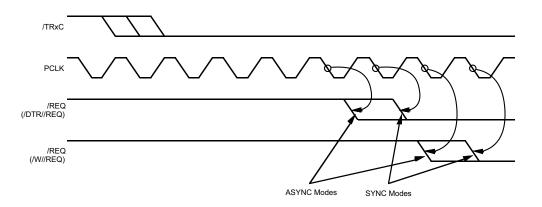

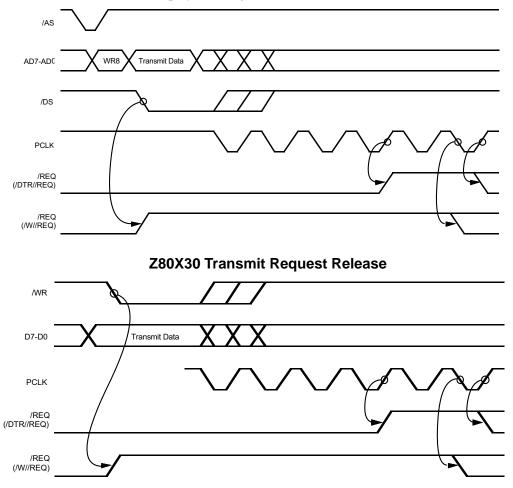

**/DTR//REQA, /DTR//REQB**. Data Terminal Ready/Request (outputs, active Low). These pins are programmable (WR14, D2) to serve either as general-purpose outputs or as DMA Request lines. When programmed for DTR function (WR14 D2=0), these outputs follow the state programmed into the DTR bit of Write Register 5 (WR5 D7). When programmed for Ready mode, these pins serve as DMA Requests for the transmitter.

ESCC and 85C30:

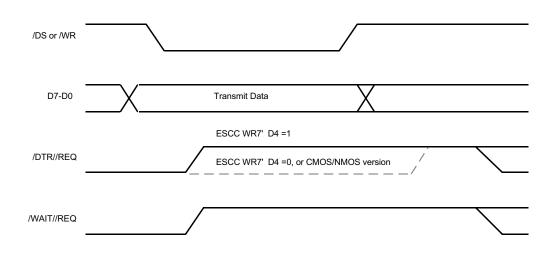

When used as DMA request lines (WR14, D2=1), the timing for the deactivation request can be programmed in the added register, Write Register 7' (WR7') bit D4. If this bit is set, the /DTR// REQ pin is deactivated with the same timing as the /W/REQ pin. If WR7' D4 is reset, the deactivation timing of /DTR//REQ pin is four clock cycles, the same as in the Z85C30.

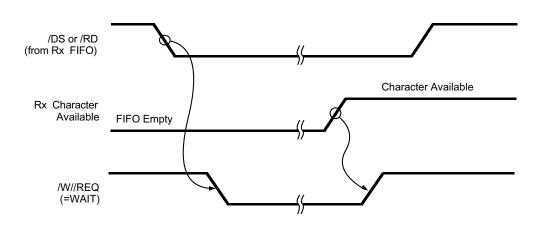

/W//REQA, /W//REQB. Wait/Request (outputs, open-drain when programmed for Wait function, driven High or Low when programmed for Ready function). These dual-purpose outputs may be programmed as Request lines for a DMA controller or as Wait lines to synchronize the CPU to the SCC data rate. The reset state is Wait.

**RxDA, RxDB.** Receive Data (inputs, active High). These input signals receive serial data at standard TTL levels.

**/RTxCA, /RTxCB.** Receive/Transmit Clocks (inputs, active Low). These pins can be programmed to several modes of operation. In each channel, /RTxC may supply the receive clock, the transmit

clock, the clock for the baud rate generator, or the clock for the Digital Phase-Locked Loop. These pins can also be programmed for use with the respective SYNC pins as a crystal oscillator. The receive clock may be 1, 16, 32, or 64 times the data rate in asynchronous modes. With the crystal oscillator option selected, these /RTxCA, /RTxCB pins becomes the oscillator Xin pins and. /SYNCA, /SYNCB become the Xout pins, respectively.

**TxDA, TxDB.** Transmit Data (outputs, active High). These output signals transmit serial data at standard TTL levels.

**/TRxCA, /TRxCB.** Transmit/Receive Clocks (inputs or outputs, active Low). These pins can be programmed in several different modes of operation. /TRxC may supply the receive clock or the transmit clock in the input mode or supply the output of the Transmit Clock Counter (which parallels the Digital Phase-Locked Loop), the crystal oscillator, the baud rate generator, or the transmit clock in the output mode.

**PCLK.** Clock (input). This is the master SCC clock used to synchronize internal signals. PCLK is a TTL level signal. PCLK is not required to have any phase relationship with the master system clock.

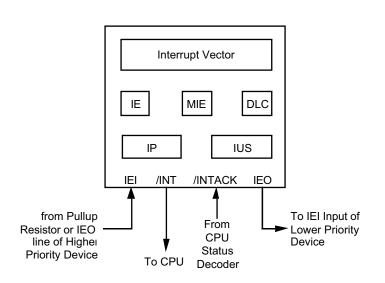

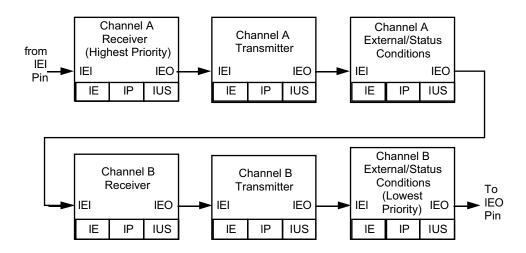

**IEI.** Interrupt Enable In (input, active High). IEI is used with IEO to form an interrupt daisy chain when there is more than one interrupt driven device. A high IEI indicates that no other higher priority device has an interrupt under service or is requesting an interrupt.

**IEO.** Interrupt Enable Out (output, active High). IEO is High only if IEI is High and the CPU is not servicing the SCC interrupt or the SCC is not requesting an interrupt (Interrupt Acknowledge cycle only). IEO is connected to the next lower priority device's IEI input and thus inhibits interrupts from lower priority devices.

**/INT.** Interrupt (output, open drain, active Low). This signal is activated when the SCC requests an interrupt. Note that /INT is an open-drain output.

**/INTACK.** Interrupt Acknowledge (input, active Low). This is a strobe which indicates that an interrupt acknowledge cycle is in progress. During this cycle, the SCC interrupt daisy chain is resolved. The device is capable of returning an interrupt vector that may be encoded with the type of interrupt pending. During the acknowledge cycle, if IEI is high, the SCC places the interrupt vector on the databus when /RD goes active. /INTACK is latched by the rising edge of PCLK.

## Pin Descriptions, (Z85X30 Only)

**D7-D0.** Data bus (bidirectional, tri-state). These lines carry data and commands to and from the Z85X30.

/CE. Chip Enable (input, active Low). This signal selects the Z85X30 for a read or write operation.

**/RD.** Read (input, active Low). This signal indicates a read operation and when the Z85X30 is selected, enables the Z85X30's bus drivers. During the Interrupt Acknowledge cycle, /RD gates the interrupt vector onto the bus if the Z85X30 is the highest priority device requesting an interrupt.

SCC/ESCC User Manual

## 16

/WR. Write (input, active Low). When the Z85X30 is selected, this signal indicates a write operation. This indicates that the CPU wants to write command bytes or data to the Z85X30 write registers.

A//B. Channel A/Channel B (input). This signal selects the channel in which the read or write operation occurs. High selects channel A and Low selects channel B.

**D**//**C**. Data/Control Select (input). This signal defines the type of information transferred to or from the Z85X30. High means data is being transferred and Low indicates a command.

## Pin Descriptions, (Z80X30 Only)

**AD7-AD0**. Address/Data Bus (bidirectional, active High, tri-state). These multiplexed lines carry register addresses to the Z80X30 as well as data or control information to and from the Z80X30.

**R**//**W**. Read//Write (input, read active High). This signal specifies whether the operation to be performed is a read or a write.

**/CS0**. Chip Select 0 (input, active Low). This signal is latched concurrently with the addresses on AD7-AD0 and must be active for the intended bus transaction to occur.

**CS1**. Chip Select 1 (input, active High). This second select signal must also be active before the intended bus transaction can occur. CS1 must remain active throughout the transaction.

**/DS**. Data Strobe (input, active Low). This signal provides timing for the transfer of data into and out of the Z80X30. If /AS and /DS are both Low, this is interpreted as a reset.

**/AS**. Address Strobe (input, active Low). Address on AD7AD0 are latched by the rising edge of this signal.

# Interfacing the SCC/ESCC

## Introduction

This chapter covers the system interface requirements with the SCC. Timing requirements for both devices are described in a general sense here, and the user should refer to the SCC Product Specification for detailed AC/DC parametric requirements.

The ESCC and the 85C30 have an additional register, Write Register Seven Prime (WR7'). Its features include the ability to read WR3, WR4, WR5, WR7', and WR10. Both the ESCC and the 85C30 have the ability to deassert the /DTR//REG pin quickly to ease DMA interface design. Additionally, the Z85230/L features a relaxed requirement for a valid data bus when the /WR pin goes Low. The effects of the deeper data FIFOs should be considered when writing the interrupt service routines. The user should read the sections which follow for details on these features.

## Z80X30 Interface Timing

The Z-Bus compatible SCC is suited for system applications with multiplexed address/data buses similar to the  $Z8^{\textcircled{R}}$ , Z8000, and Z280.

Two control signals, /AS and /DS, are used by the Z80X30 to time bus transactions. In addition, four other control signals (/CS0, CS1, R//W, and /INTACK) are used to control the type of bus transaction that occurs. A bus transaction is initiated by /AS; the rising edge latches the register address on the Address/Data bus and the state of /INTACK and /CS0.

In addition to timing bus transactions, /AS is used by the interrupt section to set the Interrupt Pending (IP) bits.

Because of this, /AS must be kept cycling for the interrupt section to function properly.

The Z80X30 generates internal control signals in response to a register access. Since /AS and /DS have no phase relationship with PCLK, the circuit generating these internal control signals provides time for metastable conditions to disappear. This results in a recovery time related to PCLK.

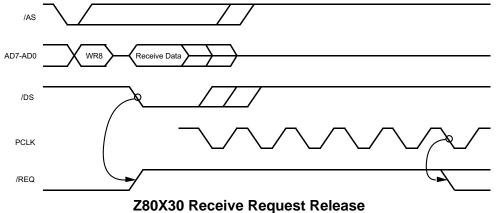

This recovery time applies only to transactions involving the Z80X30, and any intervening transactions are ignored. This recovery time is four PCLK cycles, measured from the falling edge of / DS of one access to the SCC, to the falling edge of /DS for a subsequent access.

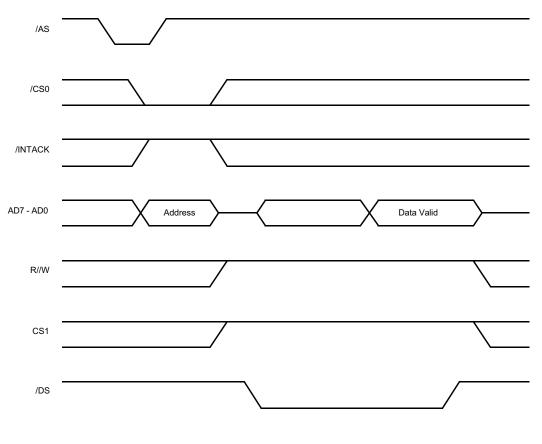

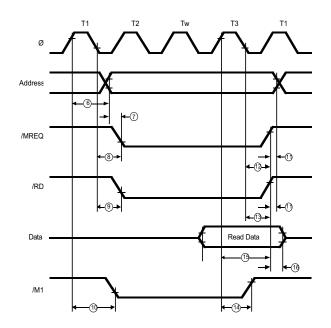

## Z80X30 Read Cycle Timing

The read cycle timing for the Z80X30 is displayed in Figure . R//W must be High before /DS falls to indicate a read The register address on AD7-AD0, as well as the state of cycle. The Z80X30 data bus drivers are enabled while CS1 /CS0 and /INTACK, are latched by the rising edge of /AS. is High and /DS is Low.

Z80X30 Read Cycle

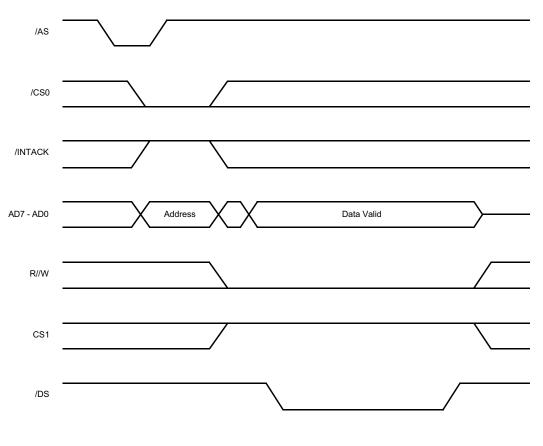

## Z80X30 Write Cycle Timing

The write cycle timing for the Z80X30 is displayed in Figure on page 19. The register address on AD7-AD0, as well as the state of /CS0 and /INTACK, are latched by the rising edge of /AS. R//W must be Low when /DS falls to indicate a write cycle. The leading edge of the coincidence of CS1 High and /DS Low latches the write data on AD7-AD0, as well as the state of R//W.

SCC/ESCC User Manual

zilog

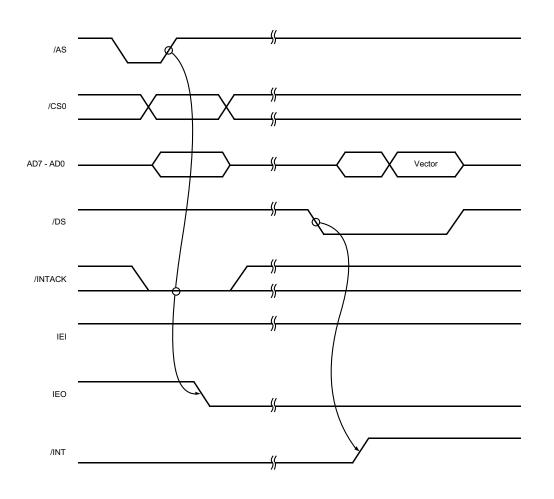

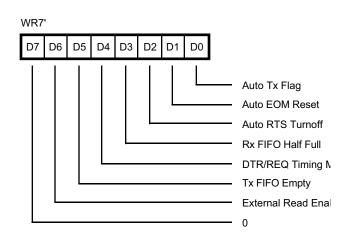

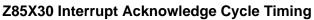

## Z80X30 Interrupt Acknowledge Cycle Timing

The interrupt acknowledge cycle timing for the Z80X30 is displayed in Figure on page 20. The address on AD7-AD0 and the state of /CS0 and /INTACK are latched by the rising edge of /AS. However, if /INTACK is Low, the address, /CS0, CS1 and R//W are ignored for the duration of the interrupt acknowledge cycle.

SCC/ESCC User Manual

19

zilog

SCC/ESCC User Manual Zilog<sup>•</sup> 20

The Z80X30 samples the state of /INTACK on the rising edge of /AS, and AC parameters #7 and #8 specify the setup and hold-time requirements. Between the rising edge of /AS and the falling edge of /DS, the internal and external daisy chains settle (AC parameter #29). A system with no external daisy chain should provide the time specified in spec #29 to settle the interrupt daisy-chain priority internal to the SCC. Systems using an external daisy chain should refer to Note 5 referenced in the Z80X30 Read/Write & Interrupt Acknowledge Timing for the time required to settle the daisy chain.

Note:

/INTACK is sampled on the rising edge of /AS. If it does not meet the setup time to the first rising edge of /AS of the interrupt acknowledge cycle, it is latched on the next rising edge of /AS. Therefore, if /INTACK is asynchronous to /AS, it may be necessary to add a PCLK cycle to the calculation for /INTACK to /RD delay time.

SCC/ESCC User Manual Zilog<sup>\*</sup>

If there is an interrupt pending in the SCC, and IEI is High when /DS falls, the acknowledge cycle was intended for the SCC. This being the case, the Z80X30 sets the Interrupt-Under-Service (IUS) latch for the highest priority pending interrupt, as well as placing an interrupt vector on AD7-AD0. The placing of a vector on the bus can be disabled by setting WR9, D1=1. The /INT pin also goes inactive in response to the falling edge of /DS. Note that there should be only one / DS per acknowledge cycle. Another important fact is that the IP bits in the Z80X30 are updated by /AS, which may delay interrupt requests if the processor does not supply /AS strobes during the time between accesses of the Z80X30.

## Z80X30 Register Access

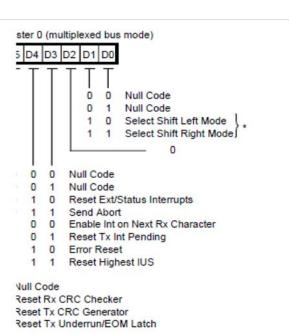

The registers in the Z80X30 are addressed via the address on AD7-AD0 and are latched by the rising edge of /AS. The Shift Right/Shift Left bit in the Channel B WR0 controls which bits are decoded to form the register address. It is placed in this register to simplify programming when the current state of the Shift Right/Shift Left bit is not known.

A hardware reset forces Shift Left mode where the address is decoded from AD5-AD1. In Shift Right mode, the address is decoded from AD4-AD0. The Shift Right/Shift Left bit is written via a command to make the software writing to WR0 independent of the state of the Shift Right/Shift Left bit.

While in the Shift Left mode, the register address is placed on AD4-AD1 and the Channel Select bit, A/B, is decoded from AD5. The register map for this case is listed in Table on page 21. In Shift Right mode, the register address is again placed on AD4-AD1 but the channel select A/B is decoded from AD0. The register map for this case is listed in Table on page 23.

Because the Z80X30 does not contain 16 read registers, the decoding of the read registers is not complete; this is listed in Table on page 21 and Table on page 23 by parentheses around the register name. These addresses may also be used to access the read registers. Also, note that the Z80X30 contains only one WR2 and WR9; these registers may be written from either channel.

Shift Left Mode is used when Channel A and B are to be programmed differently. This allows the software to sequence through the registers of one channel at a time. The Shift Right Mode is used when the channels are programmed the same. By incrementing the address, the user can program the same data value into both the Channel A and Channel B register.

## Z80X30 Register Map (Shift Left Mode)

|     |     |     |     |     |       | READ 8030   |           | 80230     |

|-----|-----|-----|-----|-----|-------|-------------|-----------|-----------|

|     |     |     |     |     |       | 80C30/230*  | 80C30/230 | WR15 D2=1 |

| AD5 | AD4 | AD3 | AD2 | AD1 | WRITE | WR15 D2 = 0 | WR15 D2=1 | WR7' D6=1 |

| 0   | 0   | 0   | 0   | 0   | WR0B  | RR0B        | RR0B      | RR0B      |

| 0   | 0   | 0   | 0   | 1   | WR1B  | RR1B        | RR1B      | RR1B      |

SCC/ESCC User Manual **z**ilog<sup>°</sup>

# 22

| Z80X30 Register Map (Shift Left Mode) | (Continued) |

|---------------------------------------|-------------|

|---------------------------------------|-------------|

|     |     |     |     |     |       | READ 8030   |           | 80230     |

|-----|-----|-----|-----|-----|-------|-------------|-----------|-----------|

|     |     |     |     |     |       | 80C30/230*  | 80C30/230 | WR15 D2=1 |

| AD5 | AD4 | AD3 | AD2 | AD1 | WRITE | WR15 D2 = 0 | WR15 D2=1 | WR7' D6=1 |

| 0   | 0   | 0   | 1   | 0   | WR2   | RR2B        | RR2B      | RR2B      |

| 0   | 0   | 0   | 1   | 1   | WR3B  | RR3B        | RR3B      | RR3B      |

| 0   | 0   | 1   | 0   | 0   | WR4B  | (RR0B)      | (RR0B)    | (WR4B)    |

| 0   | 0   | 1   | 0   | 1   | WR5B  | (RR1B)      | (RR1B)    | (WR5B)    |

| 0   | 0   | 1   | 1   | 0   | WR6B  | (RR2B)      | RR6B      | RR6B      |

| 0   | 0   | 1   | 1   | 1   | WR7B  | (RR3B)      | RR7B      | RR7B      |

| 0   | 1   | 0   | 0   | 0   | WR8B  | RR8B        | RR8B      | RR8B      |

| 0   | 1   | 0   | 0   | 1   | WR9   | (RR13B)     | (RR13B)   | (WR3B)    |

| 0   | 1   | 0   | 1   | 0   | WR10B | RR10B       | RR10B     | RR10B     |

| 0   | 1   | 0   | 1   | 1   | WR11B | (RR15B)     | (RR15B)   | (WR10B)   |

| 0   | 1   | 1   | 0   | 0   | WR12B | RR12B       | RR12B     | RR12B     |

| 0   | 1   | 1   | 0   | 1   | WR13B | RR13B       | RR13B     | RR13B     |

| 0   | 1   | 1   | 1   | 0   | WR14B | RR14B       | RR14B     | (WR7'B)   |

| 0   | 1   | 1   | 1   | 1   | WR15B | RR15B       | RR15B     | RR15B     |

| 1   | 0   | 0   | 0   | 0   | WR0A  | RR0A        | RR0A      | RR0A      |

| 1   | 0   | 0   | 0   | 1   | WR1A  | RR1A        | RR1A      | RR1A      |

| 1   | 0   | 0   | 1   | 0   | WR2   | RR2A        | RR2A      | RR2A      |

| 1   | 0   | 0   | 1   | 1   | WR3A  | RR3A        | RR3A      | RR3A      |

| 1   | 0   | 1   | 0   | 0   | WR4A  | (RR0A)      | (RR0A)    | (WR4A)    |

| 1   | 0   | 1   | 0   | 1   | WR5A  | (RR1A)      | (RR1A)    | (WR5A)    |

| 1   | 0   | 1   | 1   | 0   | WR6A  | (RR2A)      | RR6A      | RR6A      |

| 1   | 0   | 1   | 1   | 1   | WR7A  | (RR3A)      | RR7A      | RR7A      |

| 1   | 1   | 0   | 0   | 0   | WR8A  | RR8A        | RR8A      | RR8A      |

| 1   | 1   | 0   | 0   | 1   | WR9   | (RR13A)     | (RR13A)   | (WR3A)    |

| 1   | 1   | 0   | 1   | 0   | WR10A | RR10A       | RR10A     | RR10A     |

| 1   | 1   | 0   | 1   | 1   | WR11A | (RR15A)     | (RR15A)   | (WR10A)   |

| 1   | 1   | 1   | 0   | 0   | WR12A | RR12A       | RR12A     | RR12A     |

|     |     |     |     |     |       |             |           |           |

## Z80X30 Register Map (Shift Left Mode) (Continued)

| 80C30/230* 80C30/230 WR15<br>AD5 AD4 AD3 AD2 AD1 WRITE WR15 D2 = 0 WR15 D2=1 WR7' D |           |

|-------------------------------------------------------------------------------------|-----------|

| AD5 AD4 AD3 AD2 AD1 WRITE WR15 D2 = 0 WR15 D2=1 WR7' D                              | D2=1      |

|                                                                                     | )6=1      |

| 1 1 1 0 1 WR13A RR13A RR13A RR13A                                                   |           |

| 1 1 1 1 0 WR14A RR14A RR14A (WR7'A                                                  | <b>\)</b> |

| 1 1 1 1 1 WR15A RR15A RR15A RR15A                                                   |           |

Notes

1. The register names in () are the values read out from that register location.

2. WR15 bit D2 enables status FIFO function (not available on NMOS).

3. WR7' bit D6 enables extend read function (only on ESCC).

4. Includes 80C30/230 when WR15 D2=0.

## Z80X30 Register Map (Shift Right Mode)

|     |     |     |     |     |       | READ 8030   |           | 80230      |

|-----|-----|-----|-----|-----|-------|-------------|-----------|------------|

|     |     |     |     |     |       | 80C30/230*  | 80C30/230 | WR15 D2=1  |

| AD4 | AD3 | AD2 | AD1 | AD0 | WRITE | WR15 D2 = 0 | WR15 D2=1 | WR7' D6 =1 |

| 0   | 0   | 0   | 0   | 0   | WR0B  | RR0B        | RR0B      | RR0B       |

| 0   | 0   | 0   | 0   | 1   | WR0A  | RR0A        | RR0A      | RR0A       |

| 0   | 0   | 0   | 1   | 0   | WR1B  | RR1B        | RR1B      | RR1B       |

| 0   | 0   | 0   | 1   | 1   | WR1A  | RR1A        | RR1A      | RR1A       |

| 0   | 0   | 1   | 0   | 0   | WR2   | RR2B        | RR2B      | RR2B       |

| 0   | 0   | 1   | 0   | 1   | WR2   | RR2A        | RR2A      | RR2A       |

| 0   | 0   | 1   | 1   | 0   | WR3B  | RR3B        | RR3B      | RR3B       |

| 0   | 0   | 1   | 1   | 1   | WR3A  | RR3A        | RR3A      | RR3A       |

| 0   | 1   | 0   | 0   | 0   | WR4B  | (RR0B)      | (RR0B)    | (WR4B)     |

| 0   | 1   | 0   | 0   | 1   | WR4A  | (RR0A)      | (RR0A)    | (WR4A)     |

| 0   | 1   | 0   | 1   | 0   | WR5B  | (RR1B)      | (RR1B)    | (WR5B)     |

| 0   | 1   | 0   | 1   | 1   | WR5A  | (RR1A)      | (RR1A)    | (WR5A)     |

| 0   | 1   | 1   | 0   | 0   | WR6B  | (RR2B)      | RR6B      | RR6B       |

| 0   | 1   | 1   | 0   | 1   | WR6A  | (RR2A)      | RR6A      | RR6A       |

|     |     |     |     |     |       |             |           |            |

| Z80X | Z80X30 Register Map (Shift Right Mode) (Continued) |     |     |     |       |             |           |            |  |  |  |  |  |  |

|------|----------------------------------------------------|-----|-----|-----|-------|-------------|-----------|------------|--|--|--|--|--|--|

|      |                                                    |     |     |     |       | READ 8030   |           | 80230      |  |  |  |  |  |  |

|      |                                                    |     |     |     |       | 80C30/230*  | 80C30/230 | WR15 D2=1  |  |  |  |  |  |  |

| AD4  | AD3                                                | AD2 | AD1 | AD0 | WRITE | WR15 D2 = 0 | WR15 D2=1 | WR7' D6 =1 |  |  |  |  |  |  |

| 0    | 1                                                  | 1   | 1   | 0   | WR7B  | (RR3B)      | RR7B      | RR7B       |  |  |  |  |  |  |

| 0    | 1                                                  | 1   | 1   | 1   | WR7A  | (RR3A)      | RR7A      | RR7A       |  |  |  |  |  |  |

| 1    | 0                                                  | 0   | 0   | 0   | WR8B  | RR8B        | RR8B      | RR8B       |  |  |  |  |  |  |

| 1    | 0                                                  | 0   | 0   | 1   | WR8A  | RR8A        | RR8A      | RR8A       |  |  |  |  |  |  |

| 1    | 0                                                  | 0   | 1   | 0   | WR9   | (RR13B)     | (RR13B)   | (WR3B)     |  |  |  |  |  |  |

| 1    | 0                                                  | 0   | 1   | 1   | WR9   | (RR13A)     | (RR13A)   | (WR3A)     |  |  |  |  |  |  |

| 1    | 0                                                  | 1   | 0   | 0   | WR10B | RR10B       | RR10B     | RR10B      |  |  |  |  |  |  |

| 1    | 0                                                  | 1   | 0   | 1   | WR10A | RR10A       | RR10A     | RR10A      |  |  |  |  |  |  |

| 1    | 0                                                  | 1   | 1   | 0   | WR11B | (RR15B)     | (RR15B)   | (WR10B)    |  |  |  |  |  |  |

| 1    | 0                                                  | 1   | 1   | 1   | WR11A | (RR15A)     | (RR15A)   | (WR10A)    |  |  |  |  |  |  |

| 1    | 1                                                  | 0   | 0   | 0   | WR12B | RR12B       | RR12B     | RR12B      |  |  |  |  |  |  |

| 1    | 1                                                  | 0   | 0   | 1   | WR12A | RR12A       | RR12A     | RR12A      |  |  |  |  |  |  |

| 1    | 1                                                  | 0   | 1   | 0   | WR13B | RR13B       | RR13B     | RR13B      |  |  |  |  |  |  |

| 1    | 1                                                  | 0   | 1   | 1   | WR13A | RR13A       | RR13A     | RR13A      |  |  |  |  |  |  |

| 1    | 1                                                  | 1   | 0   | 0   | WR14B | RR14B       | RR14B     | (WR7'B)    |  |  |  |  |  |  |

| 1    | 1                                                  | 1   | 0   | 1   | WR14A | RR14A       | RR14A     | (WR7'A)    |  |  |  |  |  |  |

| 1    | 1                                                  | 1   | 1   | 0   | WR15B | RR15B       | RR15B     | RR15B      |  |  |  |  |  |  |

| 1    | 1                                                  | 1   | 1   | 1   | WR15A | RR15A       | RR15A     | RR15A      |  |  |  |  |  |  |

an (Chiff Diath Mada) (Continued)

Notes

1. The register names in () are the values read out from that register location.

2. WR15 bit D2 enables status FIFO function (not available on NMOS).

3. WR7' bit D6 enables extend read function (only on ESCC).

4. \* Includes 80C30/230 when WR15 D2=0.

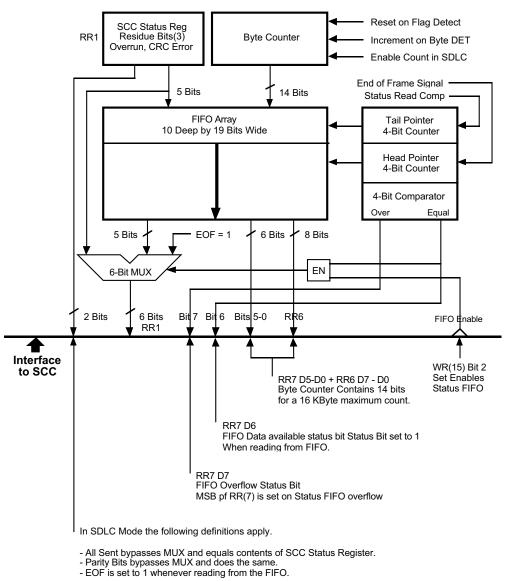

#### Z80C30 Register Enhancement

The Z80C30 has an enhancement to the NMOS Z8030 register set, which is the addition of a 10x19 SDLC Frame Status FIFO. When WR15 bit D2=1, the SDLC Frame Status FIFO is enabled, and it changes the functionality of RR6 and RR7. See Section SDLC Frame Status FIFO on page 126 for more details on this feature.

# SCC/ESCC User Manual Zilog

## Z80230 Register Enhancements

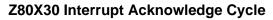

In addition to the Z80C30 enhancements, the 80230 has several enhancements to the SCC register set. These include the addition of Write Register 7 Prime (WR7'), and the ability to read registers that are read only in the 8030.

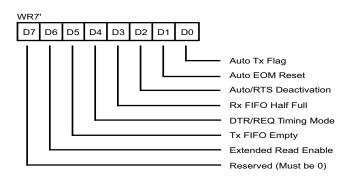

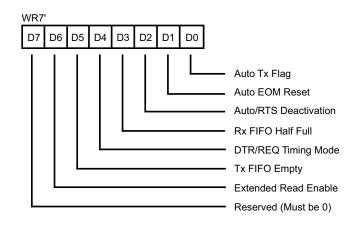

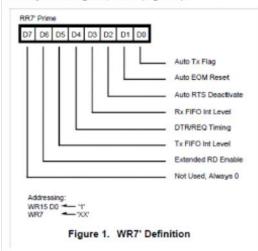

Write Register 7' is addressed by setting WR15 bit, D0=1 and then addressing WR7. Figure displays the register bit location of the six features enabled through this register. All writes to address seven are to WR7' when WR15, D0=1. Refer to Register Descriptions on page 136 for detailed information on WR7'.

WR7' bit D6=1, enables the extended read register capability. This allows the user to read the contents of WR3, WR4, WR5, WR7' and WR10 by reading RR9, RR4, RR5, RR14 and RR11, respectively. When WR7' D6=0, these write registers are write only.

Table lists what functions are enabled for the various combinations of register bit enables. See Table on page 21 (Shift Left) and Table on page 23 (Shift Right) for the register address map with the SDLC FIFO enabled only and the map with both the extended read and SDLC FIFO features enabled.

| WR15   |        | WR7'   |                                                     |

|--------|--------|--------|-----------------------------------------------------|

| Bit D2 | Bit D0 | Bit D6 | Functions Enabled                                   |

| 0      | 1      | 0      | WR7' enabled only                                   |

| 0      | 1      | 1      | WR7' with extended read enabled                     |

| 1      | 0      | Х      | 10x19 SDLC FIFO enhancement enabled only            |

| 1      | 1      | 0      | 10x19 SDLC FIFO and WR7'                            |

| 1      | 1      | 1      | 10x19 SDLC FIFO and WR7' with extended read enabled |

#### Z80230 SDLC/HDLC Enhancement Options

#### Z80X30 Reset

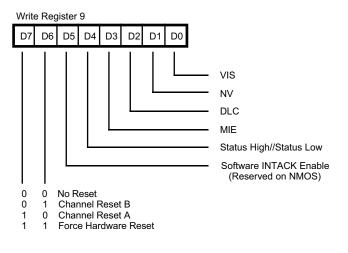

The Z80X30 may be reset by either a hardware or software reset. Hardware reset occurs when /AS and /DS are both Low at the same time, which is normally an illegal condition.

As long as both /AS and /DS are Low, the Z80X30 recognizes the reset condition. However, once this condition is removed, the reset condition is asserted internally for an additional four to five PCLK cycles. During this time, any attempt to access is ignored.

The Z80X30 has three software resets that are encoded into two command bits in WR9. There are two channel resets, which only affect one channel in the device and some bits of the write registers. The command forces the same result as the hardware reset, the Z80X30 stretches the reset signal an additional four to five PCLK cycles beyond the ordinary valid access recovery time. The bits in WR9 may be written at the same time as the reset command because these bits are affected only by a hardware reset. The reset values of the various registers are listed in Table .

|     |   | ŀ | Hard | dwa | re F | RES | ET |   |   |   | Ch | anr | nel F | RES | ΕT |   |

|-----|---|---|------|-----|------|-----|----|---|---|---|----|-----|-------|-----|----|---|

|     | 7 | 6 | 5    | 4   | 3    | 2   | 1  | 0 | 7 | 6 | 5  | 4   | 3     | 2   | 1  | 0 |

| WR0 | 0 | 0 | 0    | 0   | 0    | 0   | 0  | 0 | 0 | 0 | 0  | 0   | 0     | 0   | 0  | 0 |

| WR1 | 0 | 0 | Х    | 0   | 0    | Х   | 0  | 0 | 0 | 0 | Х  | 0   | 0     | Х   | 0  | 0 |

| WR2 | Х | Х | Х    | Х   | Х    | Х   | Х  | Х | Х | Х | Х  | Х   | Х     | Х   | Х  | Х |

| WR3 | Х | Х | Х    | Х   | Х    | Х   | Х  | 0 | Х | Х | Х  | Х   | Х     | Х   | Х  | 0 |

| WR4 | Х | Х | Х    | Х   | Х    | 1   | Х  | Х | Х | Х | Х  | Х   | Х     | 1   | Х  | Х |

| WR5 | 0 | Х | Х    | 0   | 0    | 0   | 0  | Х | 0 | Х | Х  | 0   | 0     | 0   | 0  | Х |

#### Z80X30 Register Reset Values

UM010904-0318

|           |        | ł   | Hard | dwa   | re F  | RES   | ET   |       |       |   | Ch | anr | x x x x x x<br>x x x x x x |   |   |   |  |  |  |  |

|-----------|--------|-----|------|-------|-------|-------|------|-------|-------|---|----|-----|----------------------------|---|---|---|--|--|--|--|

|           | 7      | 6   | 5    | 4     | 3     | 2     | 1    | 0     | 7     | 6 | 5  | 4   | 3                          | 2 | 1 | 0 |  |  |  |  |

| WR6       | Х      | Х   | Х    | Х     | Х     | Х     | Х    | Х     | Х     | Х | Х  | Х   | Х                          | Х | Х | Х |  |  |  |  |

| WR7       | Х      | Х   | Х    | Х     | Х     | Х     | Х    | Х     | Х     | Х | Х  | Х   | Х                          | Х | Х | Х |  |  |  |  |

| WR7'*     | 0      | 0   | 1    | 0     | 0     | 0     | 0    | 0     | 0     | 0 | 1  | 0   | 0                          | 0 | 0 | 0 |  |  |  |  |

| WR9       | 1      | 1   | 0    | 0     | 0     | 0     | Х    | Х     | Х     | Х | 0  | Х   | Х                          | Х | Х | Х |  |  |  |  |

| WR10      | 0      | 0   | 0    | 0     | 0     | 0     | 0    | 0     | 0     | Х | Х  | 0   | 0                          | 0 | 0 | 0 |  |  |  |  |

| WR11      | 0      | 0   | 0    | 0     | 1     | 0     | 0    | 0     | Х     | Х | Х  | Х   | Х                          | Х | Х | Х |  |  |  |  |

| WR12      | Х      | Х   | Х    | Х     | Х     | Х     | Х    | Х     | Х     | Х | Х  | Х   | Х                          | Х | Х | Х |  |  |  |  |

| WR13      | Х      | Х   | Х    | Х     | Х     | Х     | Х    | Х     | Х     | Х | Х  | Х   | Х                          | Х | Х | Х |  |  |  |  |

| WR14      | Х      | Х   | 1    | 1     | 0     | 0     | 0    | 0     | Х     | Х | 1  | 0   | 0                          | 0 | Х | Х |  |  |  |  |

| WR15      | 1      | 1   | 1    | 1     | 1     | 0     | 0    | 0     | 1     | 1 | 1  | 1   | 1                          | 0 | 0 | 0 |  |  |  |  |

| RR0       | Х      | 1   | Х    | Х     | Х     | 1     | 0    | 0     | Х     | 1 | Х  | Х   | Х                          | 1 | 0 | 0 |  |  |  |  |

| RR1       | 0      | 0   | 0    | 0     | 0     | 1     | 1    | Х     | <br>0 | 0 | 0  | 0   | 0                          | 1 | 1 | Х |  |  |  |  |

| RR3       | 0      | 0   | 0    | 0     | 0     | 0     | 0    | 0     | 0     | 0 | 0  | 0   | 0                          | 0 | 0 | 0 |  |  |  |  |

| RR10      | 0      | Х   | 0    | 0     | 0     | 0     | 0    | 0     | 0     | Х | 0  | 0   | 0                          | 0 | 0 | 0 |  |  |  |  |

| Note: *WF | R7' is | ava | ilab | le or | nly o | n the | e Z8 | 0230. |       |   |    |     |                            |   |   |   |  |  |  |  |

#### Z80X30 Register Reset Values (Continued)

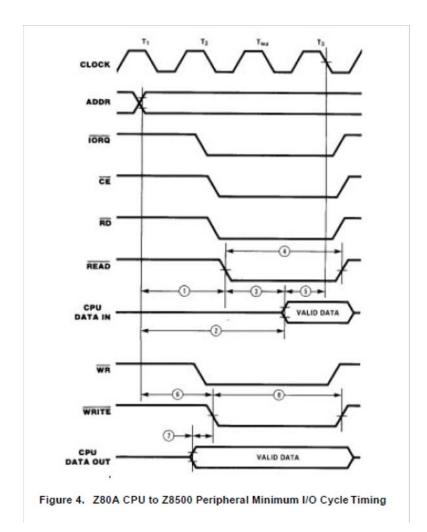

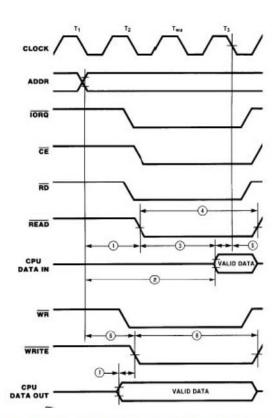

## Z85X30 Interface Timing

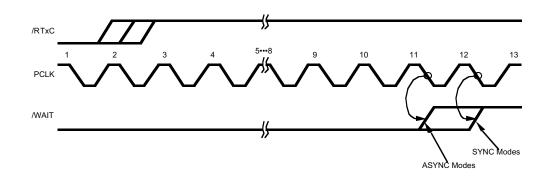

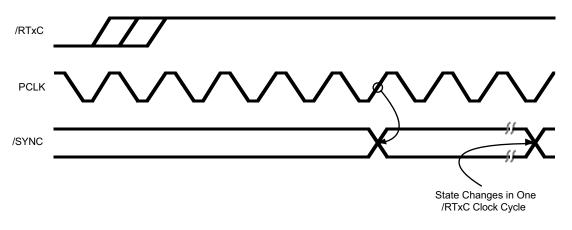

Two control signals, /RD and /WR, are used by the Z85X30 to time bus transactions. In addition, four other control signals, /CE, D//C, A//B and /INTACK, are used to control the type of bus transaction that occurs. A bus transaction starts when the addresses on D//C and A//B are asserted before /RD or /WR fall (AC Spec #6 and #8). The coincidence of /CE and /RD or /CE and /WR latches the state of D//C and A//B and starts the internal operation. The /INTACK signal must have been previously sampled High by a rising edge of PCLK for a read or write cycle to occur. In addition to sampling /INTACK, PCLK is used by the interrupt section to set the IP bits.

The Z85X30 generates internal control signals in response to a register access. Since /RD and /WR have no phase relationship with PCLK, the circuitry generating these internal control signals provides time for metastable conditions to disappear. This results in a recovery time related to PCLK.

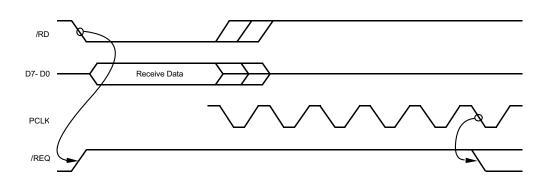

This recovery time applies only between transactions involving the Z85X30, and any intervening transactions are ignored. This recovery time is four PCLK cycles (AC Spec #49), measured from the falling edge of /RD or /WR in the case of a read or write of any register.

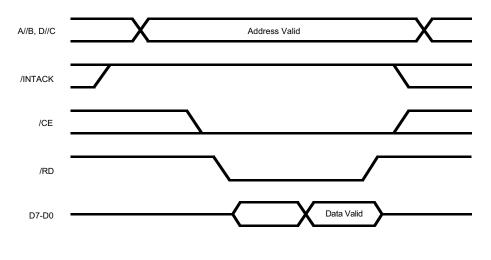

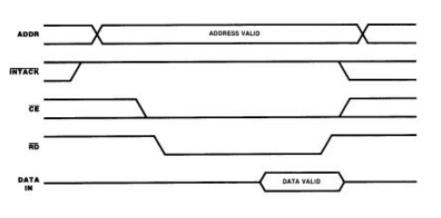

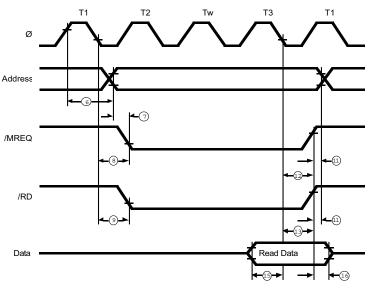

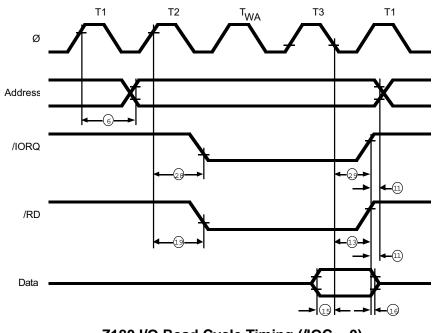

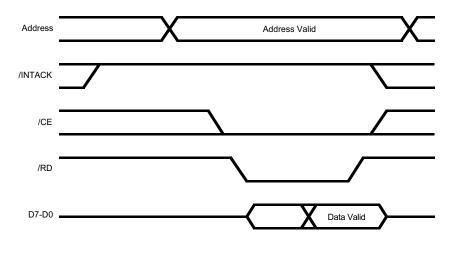

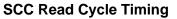

## Z85X30 Read Cycle Timing

The read cycle timing for the Z85X30 is displayed in Figure on page 28. The address on A//B and D//C is latched by the coincidence of /RD and /CE active. /CE must remain Low and /INTACK must remain High throughout the cycle. The Z85X30 bus drivers are enabled while /CE and /RD are both Low. A read with D//C High does not disturb the state of the pointers and a read cycle with D//C Low resets the pointers to zero after the internal operation is complete

Z85X30 Read Cycle Timing

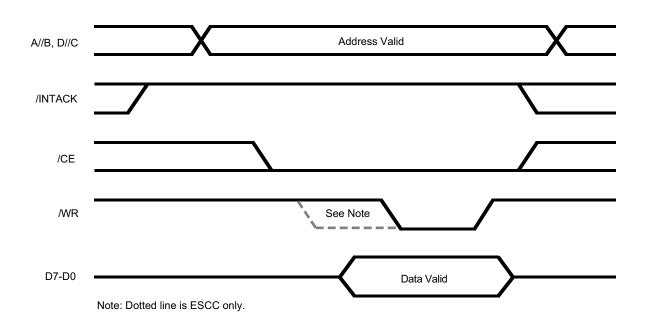

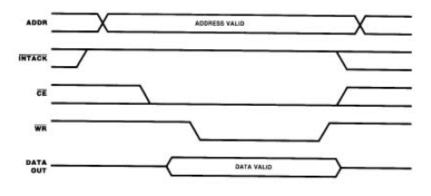

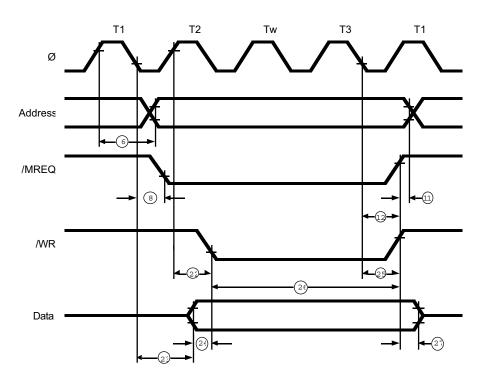

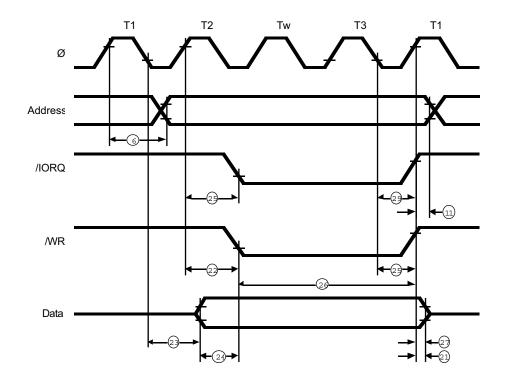

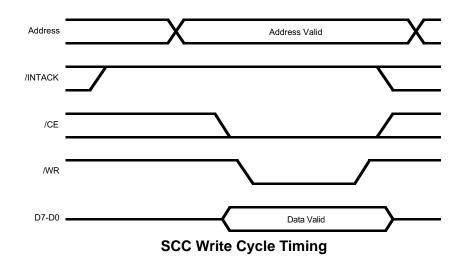

## Z85X30 Write Cycle Timing

The write cycle timing for the Z85X30 is displayed in Figure on page 29. The address on A//B and D//C, as well as the data on D7-D0, is latched by the coincidence of /WR and /CE active. /CE must remain Low and /INTACK must remain High throughout the cycle. A write cycle with D//C High does not disturb the state of the pointers and a write cycle with D//C Low resets the pointers to zero after the internal operation is complete.

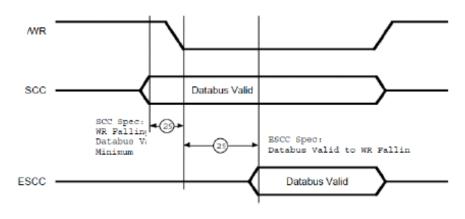

Historically, the NMOS/CMOS version latched the data bus on the falling edge of /WR. However, many CPUs do not guarantee that the data bus is valid at the time when the /WR pin goes low, so the data bus timing was modified to allow a maximum delay from the falling edge of /WR to the latching of the data bus. On the Z85230/L, the AC Timing parameter #29 TsDW(WR), Write Data to /WR falling minimum, has been changed to: /WR falling to Write Data Valid maximum. Refer to the AC Timing Characteristic section of the Z85230/L Product Specification for more information regarding this change.

SCC/ESCC User Manual Zilog<sup>°</sup> 29

## Z85X30 Write Cycle Timing

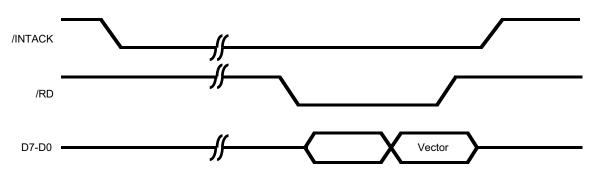

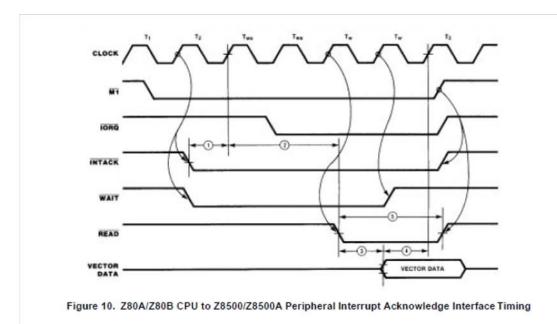

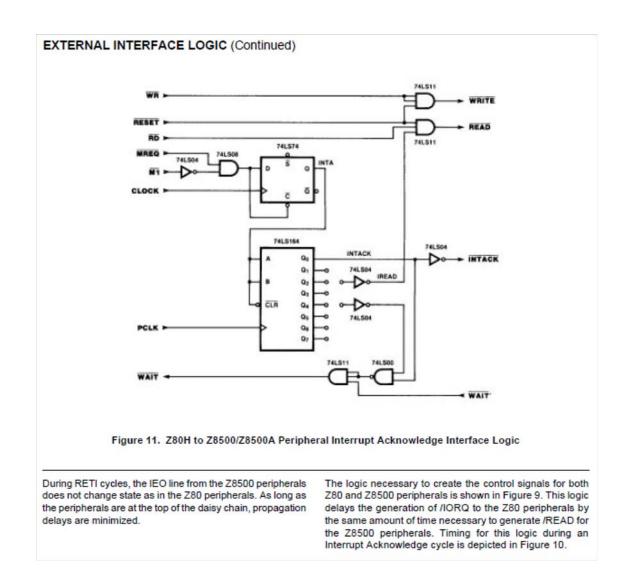

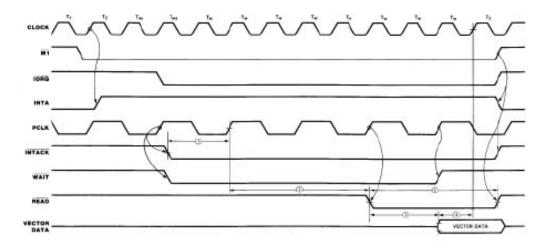

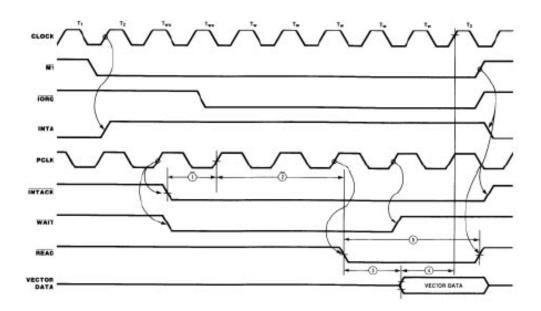

## Z85X30 Interrupt Acknowledge Cycle Timing

The interrupt acknowledge cycle timing for the Z85X30 is displayed in Figure on page 29. The state of /INTACK is latched by the rising edge of PCLK (AC Spec #10). While /INTACK is Low, the state of A//B, /CE, D//C, and /WR are ignored.

falls, the internal and external

Between the time /INTACK is first sampled Low and the time /RD falls, the internal and external IEI/IEO daisy chain settles (AC parameter #38 TdIAI(RD) Note 5). A system with no external daisy chain must provide the time specified in AC Spec #38 to settle the interrupt daisy chain priority internal to the SCC. Systems using the external IEI/IEO daisy chain should refer to Note 5 referenced in the Z85X30 Read/Write and Interrupt Acknowledge Timing for the time required to settle the daisy chain.

>

**Note:** /INTACK is sampled on the rising edge of PCLK. If it does not meet the setup time to the first rising edge of PCLK of the interrupt acknowledge cycle, it is latched on the next rising edge of PCLK. Therefore, if /INTACK is asynchronous to PCLK, it may be necessary to add a PCLK cycle to the calculation for /INTACK to /RD delay time.

If there is an interrupt pending in the Z85X30, and IEI is High when /RD falls, the interrupt acknowledge cycle was intended for the Z85X30. In this case, the Z85X30 sets the appropriate Interrupt-Under-Service latch, and places an interrupt vector on D7-D0.

If the falling edge of /RD sets an IUS bit in the Z85X30, the /INT pin goes inactive in response to the falling edge. Note that there should be only one /RD per acknowledge cycle.

- **Notes:** 1. The IP bits in the Z85X30 are updated by PCLK. However, when the register pointer is pointing to RR2 and RR3, the IP bits are prevented from changing. This prevents data changing during a read, but will delay interrupt requests if the pointers are left pointing at these registers.

- 2. The SCC should only receive one INTACK signal per acknowledge cycle. Therefore, if the CPU generates more than one (as is common for the 80X86 family), an external circuit should be used to convert this into a single pulse or does not use Interrupt Acknowledge.

# Z85X30 Register Access

The registers in the Z85X30 are accessed in a two step process, using a Register Pointer to perform the addressing. To access a particular register, the pointer bits are set by writing to WR0. The pointer bits may be written in either channel because only one set exists in the Z85X30. After the pointer bits are set, the next read or write cycle of the Z85X30 having D//C Low will access the desired register. At the conclusion of this read or write cycle the pointer bits are reset to 0s, so that the next control write is to the pointers in WR0.

A read to RR8 (the receive data FIFO) or a write to WR8 (the transmit data FIFO) is either done in this fashion or by accessing the Z85X30 having D//C pin High. A read or write with D//C High accesses the data registers directly, and independently of the state of the pointer bits. This allows single-cycle access to the data registers and does not disturb the pointer bits.

The fact that the pointer bits are reset to 0, unless explicitly set otherwise, means that WR0 and RR0 may also be accessed in a single cycle. That is, it is not necessary to write the pointer bits with 0 before accessing WR0 or RR0.

There are three pointer bits in WR0, and these allow access to the registers with addresses 7 through 0. Note that a command may be written to WR0 at the same time that the pointer bits are written. To access the registers with addresses 15 through 8, the Point High command must accompany the pointer bits. This precludes concurrently issuing a command when pointing to these registers.

The register map for the Z85X30 is listed in Table on page 31. If, for some reason, the state of the pointer bits is unknown they may be reset to 0 by performing a read cycle with the D//C pin held Low. Once the pointer bits have been set, the desired channel is selected by the state of the A//B pin during the actual read or write of the desired register.

|      |         |         |       |       | Read 8530   |           |           |  |  |  |  |

|------|---------|---------|-------|-------|-------------|-----------|-----------|--|--|--|--|

|      |         |         |       |       | 85C30/230   | 85C30/230 | WR15 D2=1 |  |  |  |  |

| A//B | PNT2    | PNT1    | PNT0  | WRITE | WR15 D2 = 0 | WR15 D2=1 | WR7' D6=1 |  |  |  |  |

| 0    | 0       | 0       | 0     | WR0B  | RR0B        | RR0B      | RR0B      |  |  |  |  |

| 0    | 0       | 0       | 1     | WR1B  | RR1B        | RR1B      | RR1B      |  |  |  |  |

| 0    | 0       | 1       | 0     | WR2   | RR2B        | RR2B      | RR2B      |  |  |  |  |

| 0    | 0       | 1       | 1     | WR3B  | RR3B        | RR3B      | RR3B      |  |  |  |  |

| 0    | 1       | 0       | 0     | WR4B  | (RR0B)      | (RR0B)    | (WR4B)    |  |  |  |  |

| 0    | 1       | 0       | 1     | WR5B  | (RR1B)      | (RR1B)    | (WR5B)    |  |  |  |  |

| 0    | 1       | 1       | 0     | WR6B  | (RR2B)      | RR6B      | RR6B      |  |  |  |  |

| 0    | 1       | 1       | 1     | WR7B  | (RR3B)      | RR7B      | RR7B      |  |  |  |  |

| 1    | 0       | 0       | 0     | WR0A  | RR0A        | RR0A      | RR0A      |  |  |  |  |

| 1    | 0       | 0       | 1     | WR1A  | RR1A        | RR1A      | RR1A      |  |  |  |  |

| 1    | 0       | 1       | 0     | WR2   | RR2A        | RR2A      | RR2A      |  |  |  |  |

| 1    | 0       | 1       | 1     | WR3A  | RR3A        | RR3A      | RR3A      |  |  |  |  |

| 1    | 1       | 0       | 0     | WR4A  | (RR0A)      | (RR0A)    | (WR4A)    |  |  |  |  |

| 1    | 1       | 0       | 1     | WR5A  | (RR1A)      | (RR1A)    | (WR5A)    |  |  |  |  |

| 1    | 1       | 1       | 0     | WR6A  | (RR2A)      | RR6A      | RR6A      |  |  |  |  |

| 1    | 1       | 1       | 1     | WR7A  | (RR3A)      | RR7A      | RR7A      |  |  |  |  |

| With | Point H | ligh Co | ommar | nd    |             |           |           |  |  |  |  |

| 0    | 0       | 0       | 0     | WR8B  | RR8B        | RR8B      | RR8B      |  |  |  |  |

| 0    | 0       | 0       | 1     | WR9   | (RR13B)     | (RR13B)   | (WR3B)    |  |  |  |  |

|      |         |         |       |       |             |           |           |  |  |  |  |

# Z85X30 Register Map

SCC/ESCC User Manual zilog

# Z85X30 Register Map (Continued)

|      |      |      |      |       | Read 8530   |           |           |

|------|------|------|------|-------|-------------|-----------|-----------|

|      |      |      |      |       | 85C30/230   | 85C30/230 | WR15 D2=1 |

| A//B | PNT2 | PNT1 | PNT0 | WRITE | WR15 D2 = 0 | WR15 D2=1 | WR7' D6=1 |

| 0    | 0    | 1    | 0    | WR10B | RR10B       | RR10B     | RR10B     |

| 0    | 0    | 1    | 1    | WR11B | (RR15B)     | (RR15B)   | (WR10B)   |

| 0    | 1    | 0    | 0    | WR12B | RR12B       | RR12B     | RR12B     |

| 0    | 1    | 0    | 1    | WR13B | RR13B       | RR13B     | RR13B     |

| 0    | 1    | 1    | 0    | WR14B | RR14B       | RR14B     | (WR7'B)   |

| 0    | 1    | 1    | 1    | WR15B | RR15B       | RR15B     | RR15B     |

| 1    | 0    | 0    | 0    | WR8A  | RR8A        | RR8A      | RR8A      |

| 1    | 0    | 0    | 1    | WR9   | (RR13A)     | (RR13A)   | (WR3A)    |

| 1    | 0    | 1    | 0    | WR10A | RR10A       | RR10A     | RR10A     |

| 1    | 0    | 1    | 1    | WR11A | (RR15A)     | (RR15A)   | (WR10A)   |

| 1    | 1    | 0    | 0    | WR12A | RR12A       | RR12A     | RR12A     |

| 1    | 1    | 0    | 1    | WR13A | RR13A       | RR13A     | RR13A     |

| 1    | 1    | 1    | 0    | WR14A | RR14A       | RR14A     | (WR7'A)   |

| 1    | 1    | 1    | 1    | WR15A | RR15A       | RR15A     | RR15A     |

Notes

1. WR15 bit D2 enables status FIFO function. (Not available on NMOS).

2. WR7' bit D6 enables extend read function. (Only on ESCC and 85C30).

# Z85C30 Register Enhancement

The Z85C30 has an enhancement to the NMOS Z8530 register set, which is the addition of a 10x19 SDLC Frame Status FIFO. When WR15 bit D2=1, the SDLC Frame Status FIFO is enabled, and it changes the functionality of RR6 and RR7. See SDLC Frame Status FIFO on page 126 for more details on this feature.

#### Z85C30/Z85230/L Register Enhancements

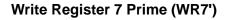

In addition to the enhancements mentioned in Z85C30 Register Enhancement on page 32, the 85C30/85230/L provides several enhancements to the SCC register set. These include the addition of Write Register 7 Prime (WR7), the ability to read registers that are write-only in the SCC.

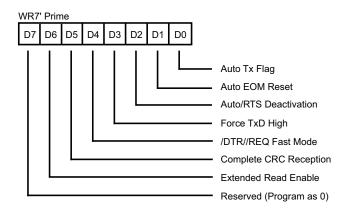

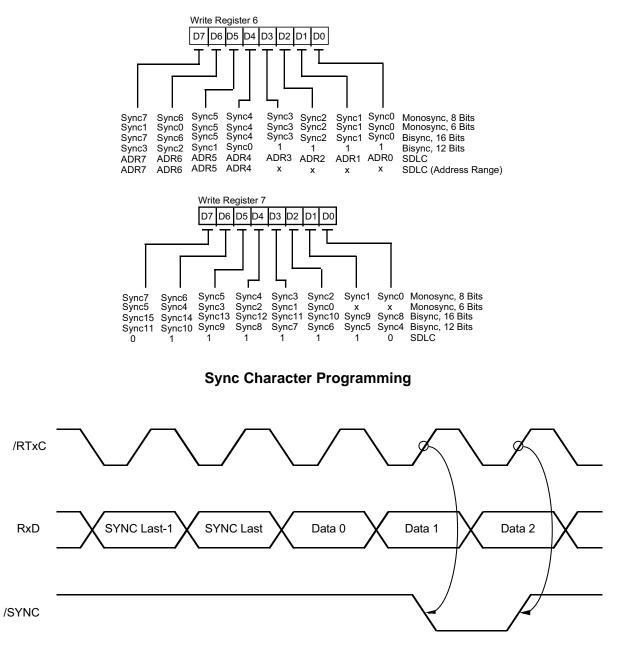

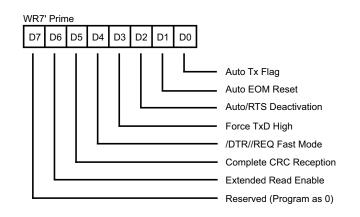

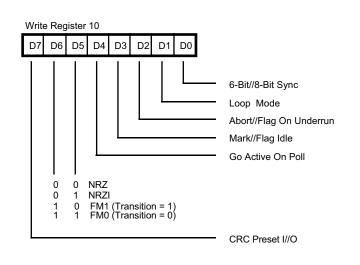

Write Register 7' is addressed by setting WR15, D0=1 and then addressing WR7. Figure and Figure on page 33 displays the register bit location of the six features enabled through this register

for the 85230/L, while Figure on page 29 displays the register bit location for the 85C30. Note that the difference between the two WR7' registers for the 85230/L and the 85C30 is bit D5 and bit D4. All writes to address seven are to WR7' when WR15 D0=1. Refer to Register Descriptions on page 136 for detailed information on WR7'.

Write Register 7 Prime (WR7') for the 85230/L

Write Register 7 Prime for the 85C30

SCC/ESCC User Manual Zilog

Setting WR7' bit D6=1 enables the extended read register capability. This allows the user to read the contents of WR3, WR4, WR5, WR7' and WR10 by reading RR9, RR4, RR5, RR14 and RR11, respectively. When WR7' D6=0, these write registers are write-only.

Table lists what functions are enabled for the various combinations of register bit enables. See Table on page 31 for the register address map with only the SDLC FIFO enabled and with both the extended read and SDLC FIFO features enabled.

| W            | R15 | WR7'   |                                                     |  |  |  |  |  |

|--------------|-----|--------|-----------------------------------------------------|--|--|--|--|--|

| Bit D2 Bit D |     | Bit D6 | Functions Enabled                                   |  |  |  |  |  |

| 0            | 1   | 0      | WR7' enabled only                                   |  |  |  |  |  |

| 0            | 1   | 1      | WR7' with extended read enabled                     |  |  |  |  |  |

| 1            | 0   | Х      | 10x19 SDLC FIFO enhancement enabled only            |  |  |  |  |  |

| 1            | 1   | 0      | 10x19 SDLC FIFO and WR7'                            |  |  |  |  |  |

| 1            | 1   | 1      | 10x19 SDLC FIFO and WR7' with extended read enabled |  |  |  |  |  |

# Z85C30/Z85230/L Register Enhancement Options

# Z85X30 Reset

The Z85X30 may be reset by either a hardware or software reset. Hardware reset occurs when / WR and /RD are both Low at the same time, which is normally an illegal condition.

As long as both /WR and /RD are Low, the Z85X30 recognizes the reset condition. However, once this condition is removed, the reset condition is asserted internally for an additional four to five PCLK cycles. During this time any attempt to access is ignored.

The Z85X30 has three software resets that are encoded into the command bits in WR9. There are two channel resets which only affect one channel in the device and some bits of the write registers. The command forces the same result as the hardware reset, the Z85X30 stretches the reset signal an additional four to five PCLK cycles beyond the ordinary valid access recovery time. The bits in WR9 may be written at the same time as the reset command because these bits are affected only by a hardware reset. The reset values of the various registers are listed in Table .

# SCC/ESCC User Manual

# Z85X30 Register Reset Value

|         | Hardware RESET |         |      |     |        |      |       |      |          |       | Channel RESET |    |   |   |   |   |   |

|---------|----------------|---------|------|-----|--------|------|-------|------|----------|-------|---------------|----|---|---|---|---|---|

|         | 7              | 6       | 5    | 4   | 3      | 2    | 1     | 0    |          | 7     | 6             | 5  | 4 | 3 | 2 | 1 | 0 |

| WR0     | 0              | 0       | 0    | 0   | 0      | 0    | 0     | 0    |          | 0     | 0             | 0  | 0 | 0 | 0 | 0 | 0 |

| WR1     | 0              | 0       | Х    | 0   | 0      | Х    | 0     | 0    |          | 0     | 0             | Х  | 0 | 0 | Х | 0 | 0 |

| WR2     | Х              | Х       | Х    | Х   | Х      | Х    | Х     | Х    |          | Х     | Х             | Х  | Х | Х | Х | Х | Х |

| WR3     | Х              | Х       | Х    | Х   | Х      | Х    | Х     | 0    |          | Х     | Х             | Х  | Х | Х | Х | Х | 0 |

| WR4     | Х              | Х       | Х    | Х   | Х      | 1    | Х     | Х    |          | Х     | Х             | Х  | Х | Х | 1 | Х | Х |

| WR5     | 0              | Х       | Х    | 0   | 0      | 0    | 0     | Х    |          | 0     | Х             | Х  | 0 | 0 | 0 | 0 | Х |

| WR6     | Х              | Х       | Х    | Х   | Х      | Х    | Х     | Х    |          | Х     | Х             | Х  | Х | Х | Х | Х | Х |

| WR7     | Х              | Х       | Х    | Х   | Х      | Х    | Х     | Х    |          | Х     | Х             | Х  | Х | Х | Х | Х | Х |

| WR7'*   | 0              | 0       | 1    | 0   | 0      | 0    | 0     | 0    |          | 0     | 0             | 1  | 0 | 0 | 0 | 0 | 0 |

| WR9     | 1              | 1       | 0    | 0   | 0      | 0    | Х     | Х    |          | Х     | Х             | 0  | Х | Х | Х | Х | Х |

| WR10    | 0              | 0       | 0    | 0   | 0      | 0    | 0     | 0    |          | 0     | Х             | Х  | 0 | 0 | 0 | 0 | 0 |

| WR11    | 0              | 0       | 0    | 0   | 1      | 0    | 0     | 0    |          | Х     | Х             | Х  | Х | Х | Х | Х | Х |

| WR12    | Х              | Х       | Х    | Х   | Х      | Х    | Х     | Х    |          | Х     | Х             | Х  | Х | Х | Х | Х | Х |

| WR13    | Х              | Х       | Х    | Х   | Х      | Х    | Х     | Х    |          | Х     | Х             | Х  | Х | Х | Х | Х | Х |

| WR14    | Х              | Х       | 1    | 1   | 0      | 0    | 0     | 0    |          | Х     | Х             | 1  | 0 | 0 | 0 | Х | Х |

| WR15    | 1              | 1       | 1    | 1   | 1      | 0    | 0     | 0    |          | 1     | 1             | 1  | 1 | 1 | 0 | 0 | 0 |

| RR0     | Х              | 1       | Х    | Х   | Х      | 1    | 0     | 0    |          | Х     | 1             | Х  | Х | Х | 1 | 0 | 0 |

| RR1     | 0              | 0       | 0    | 0   | 0      | 1    | 1     | Х    |          | 0     | 0             | 0  | 0 | 0 | 1 | 1 | Х |

| RR3     | 0              | 0       | 0    | 0   | 0      | 0    | 0     | 0    |          | 0     | 0             | 0  | 0 | 0 | 0 | 0 | 0 |

| RR10    | 0              | Х       | 0    | 0   | 0      | 0    | 0     | 0    |          | 0     | Х             | 0  | 0 | 0 | 0 | 0 | 0 |

| Note: * | NR.            | 7' is ( | only | ava | ilable | e on | the 8 | 85C3 | 0 and th | ne Es | sco           | ). |   |   |   |   |   |

# **Interface Programming**

The following subsections explain and illustrate all areas of interface programming.

# I/O Programming Introduction

The SCC can work with three basic forms of I/O operations: polling, interrupts, and block transfer. All three I/O types involve register manipulation during initialization and data transfer. However, the interrupt mode also incorporates Z-Bus interrupt protocol for a fast and efficient data transfer.

Regardless of the version of the SCC, all communication modes can use a choice of polling, interrupt and block transfer. These modes are selected by the user to determine the proper hardware and software required to supply data at the rate required.

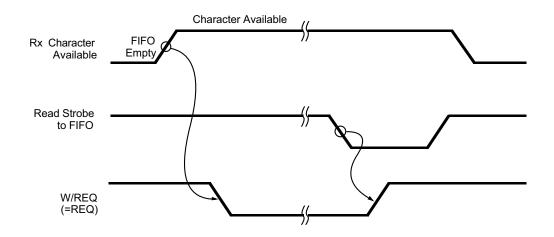

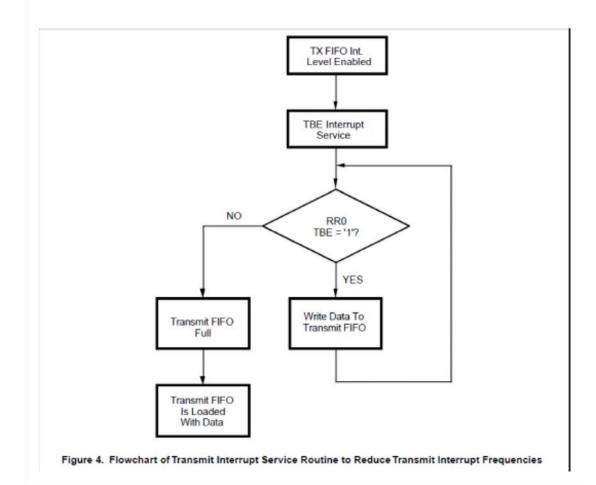

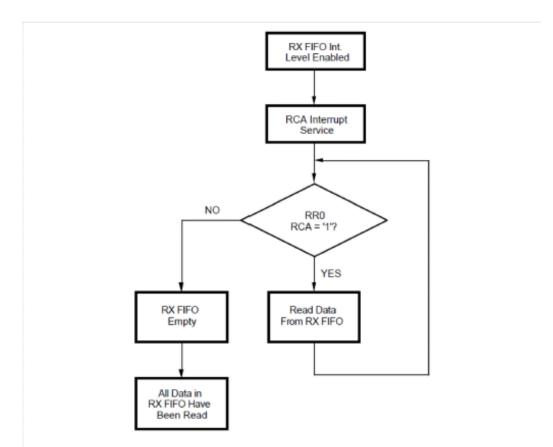

**Note to ESCC Users:** Those familiar with the NMOS/CMOS version will find the ESCC I/O operations very similar but should note the following differences: the addition of software acknowledge (which is available in the current version of the CMOS SCC, but not in NMOS); the /DTR//REQ pin can be programmed to be deasserted faster; and the programmability of the data interrupts to the FIFO fill level.

# Polling

This is the simplest mode to implement. The software must poll the SCC to determine when data is to be input or output from the SCC. In this mode, MIE (WR9, bit 3), and Wait/DMA Request Enable (WR1, bit 7) are both reset to 0 to disable any interrupt or DMA requests. The software must then poll RR0 to determine the status of the receive buffer, transmit buffer and external status.

During a polling sequence, the status of Read Register 0 is examined in each channel. This register indicates whether or not a receive or transmit data transfer is needed and whether or not any special conditions are present, e.g., errors.

This method of I/O transfer avoids interrupts and, consequently, all interrupt functions should be disabled. With no interrupts enabled, this mode of operation must initiate a read cycle of Read Register 0 to detect an incoming character before jumping to a data handler routine.

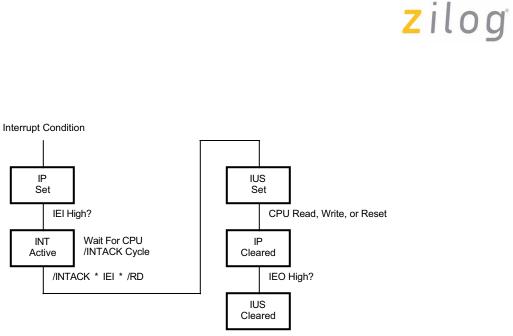

# Interrupts

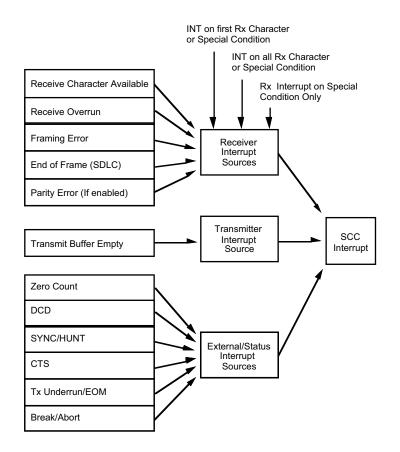

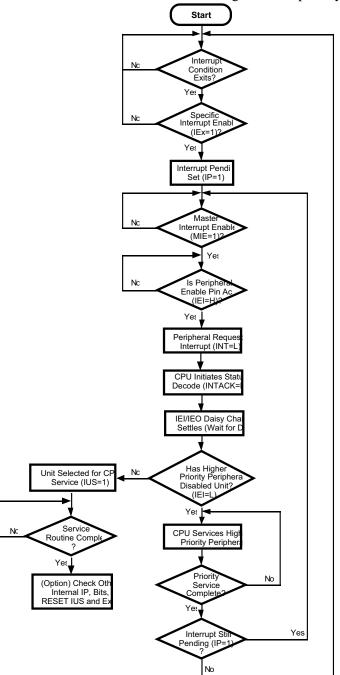

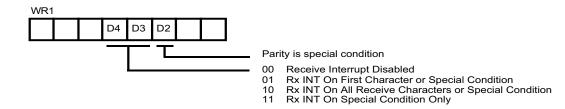

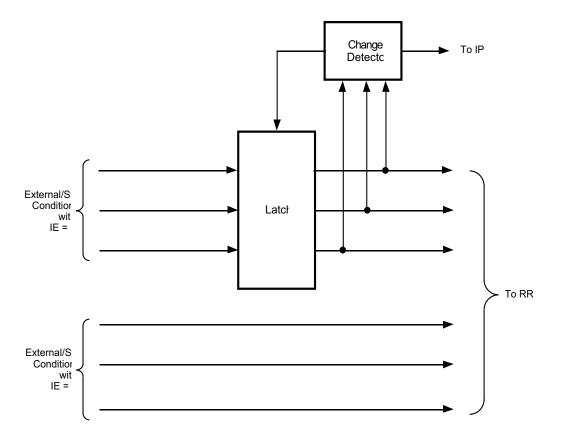

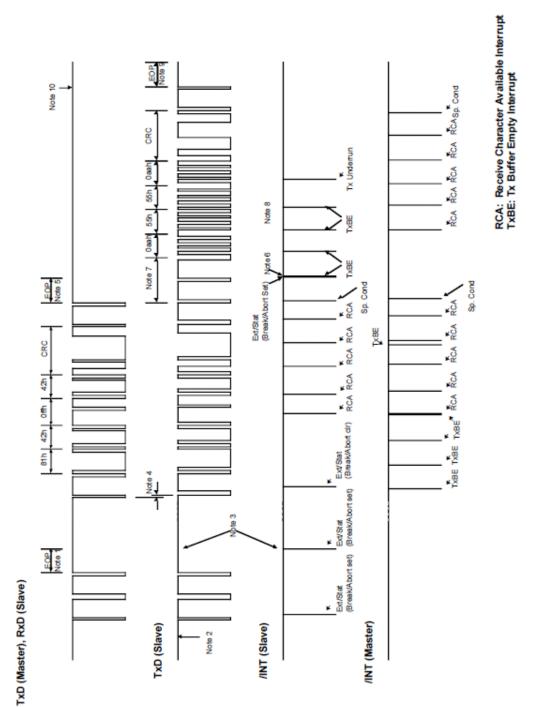

Each of the SCC's two channels contain three sources of interrupts, making a total of six interrupt sources. These three sources of interrupts are: 1) Receiver, 2) Transmitter, and 3) External/Status conditions. In addition, there are several conditions that may cause these interrupts. Figure on page 37 displays the different conditions for each interrupt source and each is enabled under program control. Channel A has a higher priority than Channel B with Receive, Transmit, and External/Status Interrupts prioritized, respectively, within each channel as listed in Table . The SCC internally updates the interrupt status on every PCLK cycle in the Z85X30 and on /AS in the Z80X30.

#### **Interrupt Source Priority**

**Receive Channel A**

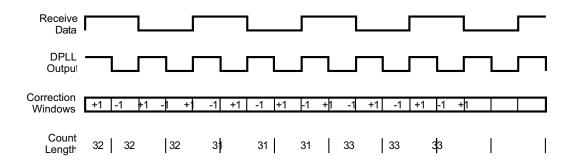

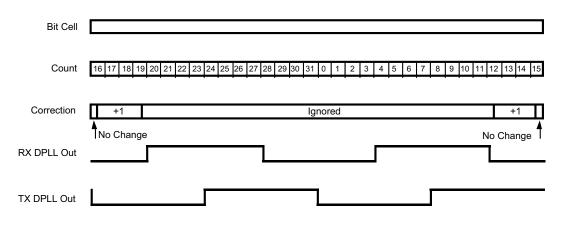

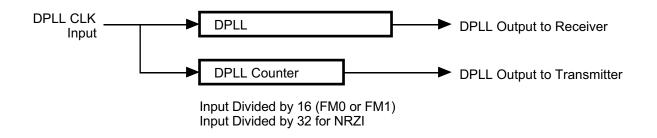

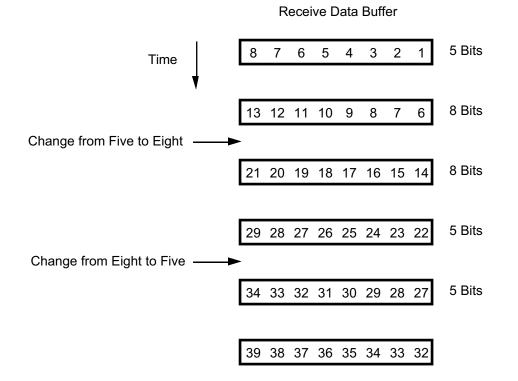

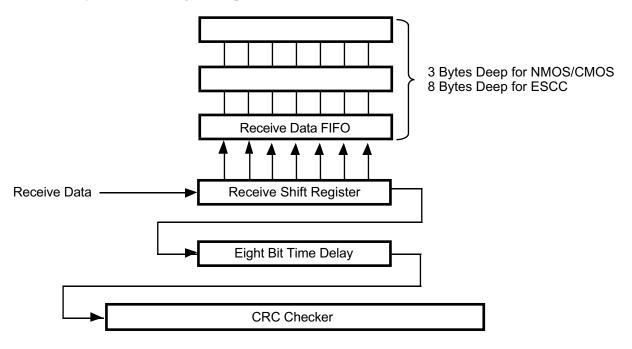

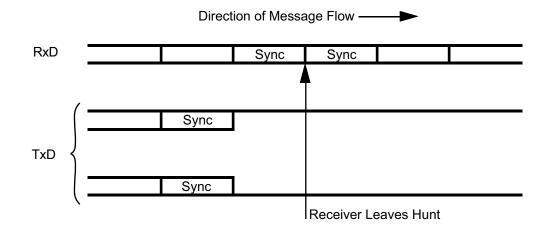

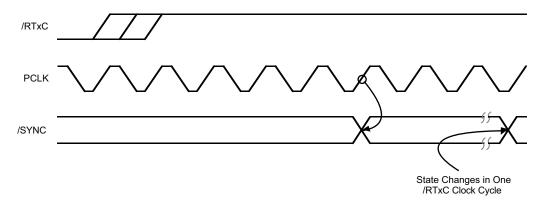

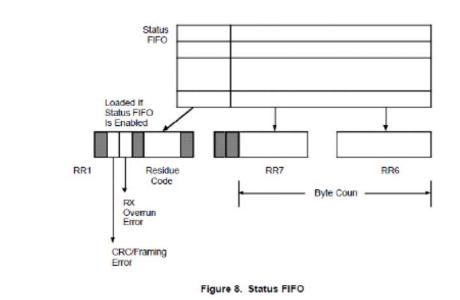

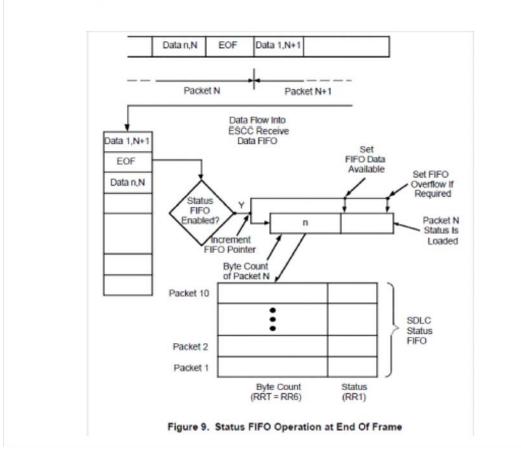

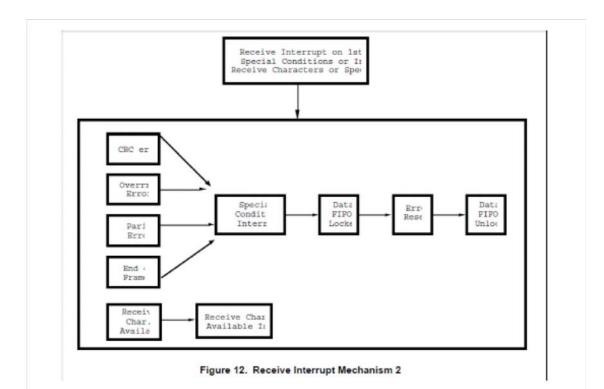

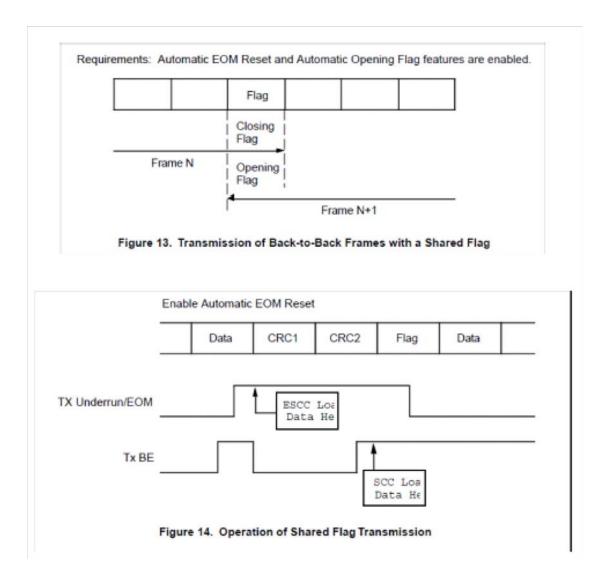

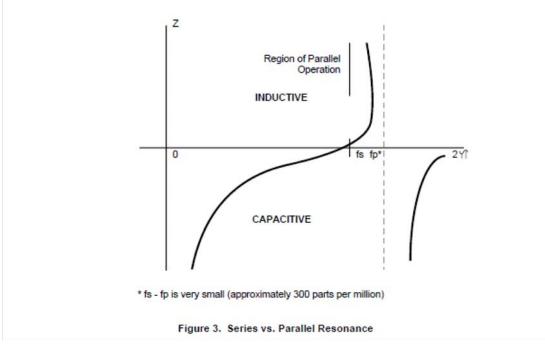

Highest